Abschlussbericht DFG-Schwerpunktprogramm 1040: Entwurf und ... · Überblick über das...

Transcript of Abschlussbericht DFG-Schwerpunktprogramm 1040: Entwurf und ... · Überblick über das...

AbschlussberichtDFG-Schwerpunktprogramm 1040:

Entwurf und Entwurfsmethodik eingebetteter Systeme

Wolfgang RosenstielUniversität Tübingen

1997 – 2003

Überblick über das Schwerpunktprogramm

Das hier zusammenfassend vorgestellte von der DFG geförderte Schwerpunktprogramm “Ent-wurf und Entwurfsmethodik eingebetteter Systeme” hat vor allem die Methodik für den System-entwurf eingebetteter Systeme erforscht und weiter entwickelt, sowie bei konkreten Anwendun-gen exemplarisch eingesetzt.

Als eingebettete Systeme(engl.: embedded systems)bezeichnet man im Allgemeinen elek-tronische Systeme, die in größere Systeme oder Umgebungen integriert sind. Sie werden fürspezielle Anwendungen entworfen und können sowohl aus Mikrocontrollern, als auch aus denfür die jeweilige Anwendung entworfenen Hard- und Software-Komponenten bestehen.

Die Kombination von Methodenentwicklung mit exemplarischem Entwurf eingebetteter Sy-steme war ein besonderer Schwerpunkt dieses Schwerpunktprogramms. Der Entwurf eingebet-teter Systeme hat sich zu einem viel beachteten eigenständigen Forschungsgebiet entwickelt,dessen besondere Anforderungen sich aus der Optimierung des Zusammenwirkens heterogenerTeilsysteme ergeben. Dabei kam es in den durchgeführten Forschungsarbeiten nicht nur daraufan, dass das eingebettete System die gewünschte Funktion erfüllt, sondern dass darüber hinausvor allem Anforderungen bezüglich der gewünschten Leistung, der Kosten des Gesamtsystems,der Zuverlässigkeit, der Sicherheit, des Energieverbrauchs usw. erfüllt werden.

Ein wichtiger Punkt ist hierbei die Beherrschung der exponentiell wachsenden Komplexitätsolcher Systeme, deren Entwurf sich erheblich vom klassischen Software-Entwurf für Desktop-Anwendungen unterscheidet. Um derart komplexe eingebettete Systeme mit vertretbaren Kostenund in möglichst kurzer Zeit entwickeln zu können, wurden im SPP neue Methoden entwickelt,die es dem Entwickler ermöglichen, Entwurfsanforderungen in einer möglichst frühen Phasedes Entwurfs zu überprüfen, und die Entwurfskosten durch fortschrittliche Entwurfsmethodikenmöglichst gering zu halten.

Neben der technischen Entwicklung eingebetteter Systeme sei auch auf die enorme wirt-schaftliche Bedeutung hingewiesen. Immer stärker entscheidet der Elektronik- und Software-Anteil (also das eingebettete System) über die gesamte Wertschöpfung neuer Produkte. DerEinsatz neuer Methoden im Entwurf komplexer Eingebetteter Systeme ist somit wettbewerbs-entscheidend und kann für Betriebe in diesem Sektor überlebenswichtig sein.

Typische Beispiele für eingebettete Systeme sind im Telekommunikationsbereich, der indu-striellen Automation und Robotik, der Unterhaltungselektronik, der Luft- und Raumfahrt undinsbesondere der Automobilindustrie zu finden. Neben dem Trend zur Steigerung der Komplexi-tät eingebetteter Systeme, ist auch der Trend zu steigender Kommunikation zwischen den hete-rogenen Komponenten eingebetteter Systeme und die durch die Mobilität hervorgerufen Anfor-derungen, wie Miniaturisierung und geringer Stromverbrauch zu beobachten.

Im Schwerpunktprogramm “Eingebettete Systeme” sind 14 Projekte gefördert worden. Indiesem Zusammenhang entstanden mehr als 100 Publikationen und mehr als 20 Dissertationen.

Die beiliegende CD enthält eine Kurzbeschreibung der Projekte des SPP und deren wichtigsteErgebnisse. Die Reihenfolge entspricht der Reihenfolge der Vorträge beim Abschlusskolloquiumdes Schwerpunktprogramms, das im Rahmen eines Workshops bei der Robert Bosch GmbH inLeonberg im November 2003 veranstaltet wurde.

Exemplarisch sollen im Folgenden einige Ergebnisse herausgegriffen und kurz beschriebenwerden.

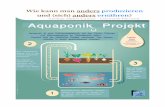

ii

Exemplarische Ergebnisse

Ein charakteristisches Merkmal eingebetteter Systemeist, dass sie speziell für eine Anwendung entworfen wur-den. Mit derDigital Versatile Architectureerarbeitete dieUniversität Leipzig eine Methodik, mit der eingebetteteSysteme genauso flexibel wie herkömmliche Computer-systeme eingesetzt werden können, ohne jedoch die ho-hen Kosten und Stromverbrauch dieser Systeme aufzuwei-sen. Dies wird dadurch erreicht, dass in den Systemen re-konfigurierbare Hardware eingesetzt wird. Die Konfigura-tionsdaten werden dabei über Accesspoints von dezentra-len Konfigurationsservern angefordert, wie folgende Ab-bildung schematisch zeigt. Um den Rechenaufwand imEingebetteten System möglichst gering zu halten, über-nehmen Accesspoints einen großen Teil, der zur Kommu-nikation mit Servern benötigten Funktionalität.

Institut für Informatik (Prof. Dr. U. Kebschull), Univer-sität Leipzig

bauen und sie so zu erweitern, dass sie unseren Ansprü-chen gerecht wird.Diese Technologie ist unter den Namen „Enterprise JavaBeans“ (EJB) bekannt. EJB baut auf der Java Technolo-gie der Firma SunTM auf. Java hat den Vorteil, dass einin dieser Sprache geschriebenes Programm auf den unter-schiedlichsten Systemen läuft, die Java unterstützen. Al-lerdings wird dieser Vorteil damit erkauft, dass man stetsetwas mehr an Prozessorleistung und Speicher benötigt.Für kleine eingebettete Systeme ist daher Java Unterstüt-zung aus Kostengründen nicht immer möglich. Wir habenallerdings eine Möglichkeit gefunden auch diese Gerätean unser System anzubinden. Dazu haben wir sogenann-te „Accesspoints“ in unser System integriert. Ein Access-point ist ein Computer, der sowohl Java beherrscht als auchmit dem einfachen Client kommunizieren kann. Beispiels-weise könnte der heimische Internet PC als Access Pointdienen. Das elektronische Notizbuch des Benutzers könn-te dann über eine einfache Infrarot Schnittstelle mit demPC kommunizieren und dieser reicht diese Anfragen dannzum Management System weiter. Access Points kann mansich also am besten als Vermittler zwischen eingebettetenSystem und Management Schicht vorstellen.

4. Ergebnisse�Erfahrungen

Wir haben mehrere einfache Prototypen entwickelt undmit ihnen unser System unter Laborbedingungen getestet.

Client Server

Thin Client(SH3 Board)

Access Point(Linux Box)

HTTPS Server

EJB Client EJB Server

opt.xml

res.xml

Eine Aufgabe der Tests war herauszufinden, wie das Sys-tem funktioniert, d.h. z.B. wie schnell es auf Anfragenreagiert. Als eingebettetes System diente dazu eine Expe-rimentierplatine mit einem Prozessor (SH3 von Hitachi)und einem FPGA (Virtex von Xilinx). Auf diesem Systemlief kein Java. Daher erfolgte die Kommunikation mit demManagement System über einen Access Point, in unseremFall einen PC. Die Kommunikation vom Experimentier-board zum PC erfolgte in HTTP, dem gleichen Protokoll,wie es auch im WWW verwendet wird. Der PC wieder-um reichte die Daten an das Management System weiter,welches durch einen EJB Server bereitgestellt wurde. Zieldes Experiments war, dass das eingebettete System Pro-grammcode anforderte, um das FPGA zu programmieren.Diese Anfrage erging an das Management System, wel-ches dann aus einer Datenbank die Code Komponente aus-wählte, die auf dem FPGA lauffähig war.

� Ergebnis: Die Zeit, die für Anfrage, Übertragung,verschiedene Initialisierungen und Datenbankabfra-gen benötigt wurde, lag bei ca. 1 Sekunde.

Ein anderes Experiment beschäftigte sich mit den Mög-lichkeiten der Energieeinsparung. Dazu programmiertenwir ein Testprogramm einmal für den Mikroprozessor undeinmal für das FPGA. Bei den anschließenden Probeläu-fen haben wir gemessen, wie groß die jeweiligen Rechen-zeiten sind und zum anderen den Stromverbrauch festge-stellt.

� Ergebnis: Im Experiment war das FPGA ca.2400mal schneller als der einfache Prozessor. Umden Stromverbrauch zu vergleichen haben wir er-rechnet, wieviel Energie (gemessen in Wattsekun-den) der Prozessor bzw. das FPGA pro „Rechen-schritt“ verbrauchen. Dabei mussten wir feststellen,dass das FPGA (1 � 10 � 8 Ws) trotz höherer Ge-schwindigkeit nur ca 1 � 1000 der Energie verbrauchtwie der Prozessor (1 � 10 � 5 Ws).

5. Fazit

Wir haben ein System aus Methoden entwickelt, die es er-möglichen können, zukünftige eingebettete Systeme ge-nau so leistungsfähig und flexibel zu gestalten wie es bis-her nur mit herkömmlicher Rechentechnik möglich ist.Unsere Labortests haben gezeigt, dass diese Metho-den prinzipiell funktionieren und daher erfolgverspre-chend sind. Zukünftige Arbeiten werden zum Ziel haben,dieses System weiter zu verbessern. Insbesondere wür-den wir uns auf Kooperationen mit Industriepartnernfreuen, um das System auch im praktischen Einsatz tes-ten zu können.

6. Weitere Informationen

Im Rahmen dieser Zusammenfassung konnte das Projektnatürlich nur kurz umrissen werden. Ausführliche Infor-mationen finden sich in unseren Veröffentlichungen:

Literatur

[1] NITSCH, LARA, KEBSCHULL: A Novel Design Technolo-gy for Next Generation Ubiquitous Computing Architectu-res. In: IPDPS RAW, Nice, 2003.

[2] LANGE, KEBSCHULL: Virtual Hardware Byte Code as aDesign Platform for Reconfigurable Embedded Systems. In:Proceedings of the Design Automation and Test in EuropeConference (DATE2003), München, 2003.

[3] NITSCH, KEBSCHULL: The Use of Runtime ConfigurationCapabilities for Networked Embedded Systems. In: Procee-dings of the Design Automation and Test in Europe Confe-rence (DATE2002), Paris, 2002.

[4] NITSCH, KEBSCHULL: Konzeption einer virtuellen, offe-nen, echtzeitfähigen Systemarchitektur. In: Workshop Mo-delltransformation und Werkzeugkopplung, Braunschweig,2001.

4

Beim Entwurf eingebetteter Systeme wird eine Evalu-ierung des Systems zu einem möglichst frühen Zeitpunktim Entwurfsprozess angestrebt. An der Universität Tübin-gen wurden zum Einen analytische Methoden entwickelt,mit denen die zeitlichen Eigenschaften von Software ineingebetteten Systemen analysiert werden können. Insbe-sondere können hiermit Schranken für denWorst-Caseer-mittelt werden. Eine andere Methodik ist die Validierungdurch Emulation, wodurch die Funktionalität von System-komponenten unter realen Bedingungen getestet werdenkann. Damit diese Methodik eine hohe Aussagekraft undAkzeptanz bei den Entwicklern erhält, sind im SPP lei-stungsstarke Werkzeuge – die EmulationsumgebungSpy-der – definiert und implementiert worden. Im Folgendensieht man ein Foto und das Blockschaltbild derSpyder-FPGA-Plattform.

Wilhelm Schickard Institut (Prof. Dr. W. Rosenstiel),Universität Tübingen

• Virtex-FPGA (XCV400-2000E)

• Konfiguration und Kommunikation über PCI-Bus

• Erweiterungsstecker mit bis zu 168Verbindungsmöglichkeiten

• On-board Speicher:• 2 x SDRAM: 4Mx32• 2 x SSRAM: 256Kx32

• Debugging• Mictor Logikanalysator Stecker• Chipscope ILA Kerne• 2 LEDs

Im Rahmen der Komponentenbasierten Entwicklungeingebetteter Systeme wurde ein eingebetteter Webserver( IAS-WebStack) eintwickelt. Passend zu diesem Webser-ver wurde eine kostengünstige Mikrocontrollerplattform,das IAS-WebBoard, realisiert, das hier abgebildet ist.

Institut für Automatisierungs- und Softwaretech-nik (Prof. Dr. P. Göhner), Universität Stuttgart

Ziel der Arbeiten der Universität Paderborn war es,das Betriebssystem und insbesondere das Kommmunika-tionssystem den Anforderungen der Anwendung entspre-chend anzupassen. Der Ansatz zeichnet sich dadurch aus,dass Betriebssystem und Kommunikationssystem aus ei-nem Baukasten kleinerer Objekte zusammensetzen. Da-bei werden nur die Elemente integriert, die wirklich be-

iii

nötigt werden. Aus unterschiedlichen Alternativen werdendie optimalen Lösungen ausgewählt, wie die folgende Ab-bildung zeigt.

Heinz Nixdorf Institut (Prof. Dr. F. Rammig), Universi-tät Paderborn

bedingungen des fertig konfigurierten Systems vor sei-ner Laufzeit zu überprüfen. Es werden Betriebsmittelbe-legungspläne erstellt und die Verzögerungs- und Latenz-zeiten der Kommunikation berechnet.

Im Projekt TEReCS wurden hierfür Verfahren undWerkzeuge entwickelt. Durch den Einsatz unseren Me-thoden wird die Zeit, die zur Erstellung eines ferti-gen Kommunikationssystems benötigt wird, erheblichreduziert. Die Wiederverwendung von Code aus ei-ner Bibliothek (DREAMS) und die Offline-Überprüfungvor dem endgültigenTargeting sind wichtige Beiträ-ge zur Verbesserung derTime-to-MarketEigenschaft beider Produktentwicklung für verteilte eingebettete Syste-me.

Bei diesem Ansatz hat sich herausgestellt, dass durchKonfigurierung von Software-Komponenten widersprüch-liche Zielsetzungen (z.B. zwischen Performanz und Fle-xibilität) hochgradig justierbar werden [2]. Gleichzeitigkonnte durch die Anwendung von Entwurfsprinzipien desHardwareentwurfs auf die Konfigurierung und den Aufbauder Bibliotheksplattform gezeigt werden, dass Betriebs-systeme als Vermittler zwischen Software und Hardwarenicht als statisch fest angesehen werden müssen, sondernsich vielmehr den Gegebenheiten anpassen können.

2. Problemstellung

Bei verteilten eingebetteten Systemen laufen auf je-dem Knoten unterschiedliche Prozesse. Diese benöti-gen dann unterschiedlichste Betriebssystemfunktionenund Hardware-Geräte. Oft werden solche verteilten Sy-steme aber auf der gleichen Hardwareplattform basie-rend implementiert. Zudem wird deshalb auch auf allenKnoten das gleiche monolithische Betriebssystem ein-gesetzt. Hier besteht eine Lücke zwischen der flexiblenProgrammierung der Prozesse und den mehr oder weni-ger statischen Betriebssystemkernen. Diese Lücke wirdmeist dadurch geschlossen, das Betriebsystem so all-gemeingültig wie möglich zu implementieren (virtuel-le Maschine). Die Dienste, die diese Betriebssystemezur Verfügung stellen, unterstützen möglichst alle un-terschiedlichen Anwendungsszenarien. Hieraus folgertjedoch, dass ein nicht unwesentlicher Teil des Betrieb-systems ungenutzt bleibt oder zumindest für konkreteAnwendungsfälle sehr ineffektiv ist.

Aus diesem Grund werden gerade Betriebssysteme füreingebettete Anwendungen flexibel und konfigurierbar an-geboten. Viele Merkmale und Fähigkeiten können para-metrisiert, hinzugefügt oder entfernt werden. Aber gera-de dieser Vorgang der Konfigurierung muss sehr oft ma-nuell vom Anwendungsprogrammierer geschehen. Jedochist es häufig schwierig für diesen zu entscheiden, welcheOptionen die besten sind oder überhaupt zu seinem An-wendungsfall passen. Der Betriebssystemprogrammiererkennt als Experte die Anwendungsfälle, für die die konfi-gurierbaren Optionen entwickelt wurden. Es war eine Auf-gabe dieses Projekts, das “Expertenwissen” formal zu er-fassen und es für eine automatische Konfigurierung zu nut-zen. Die Flexibilität und Konfigurierbarkeit des Betriebs-

HW Abstraction Layer (HAL)

HW Abstraction Layer (HAL)

Hardware

ApplicationApplicationApplicationApplicationApplicationApplicationApplicationApplicationApplicationApplication

Run-Time Platform or

Operating System

HW Abstraction Layer (HAL)

Application

Run-Time

Platform

Communication

System

Hardware

Standard:

Many applications are

developed for a static

operating system

Goal:

Optimal adapted

run-time platform

for each application

Abbildung 3. Herausforderung: von statischenBetriebssystemen hin zu hochgradig flexiblenund konfigurierbaren Laufzeitplattformen für ver-teilte eingebettete Systeme

systems soll für den Anwendungsprogrammierer transpa-rent sein.

Dazu wurden einige Werkzeuge entwickelt, mit de-nen es möglich ist, konfigurierbare Laufzeitplattformenfür verteilte eingebettete Systeme zu beschreiben, auto-matisch zu konfigurieren und bezüglich ihrer Realzeit-Eigenschaften zu analysieren.

3. Lösung

In TEReCS wird streng zwischen dem Wissen über dieAnwendung und dem Expertenwissen über die Konfigu-rationsoptionen des Betriebssystems unterschieden. DasWissen über die Anwendung wird als Anforderungsspezi-fikation angesehen. Diese Anforderungsspezifikation dientals Eingabe für den Konfigurationsprozess. Die Anfor-derungsspezifikation besteht im wesentlichen aus einerabstrakten Beschreibung der Anwendung und bestimm-ten einzuhaltenden Eigenschaften (Deadlines). Die An-wenungsbeschreibung spezifiziert dabei welche Betrieb-systemdienste welcher Prozess auf welchem Knoten wannaufruft. Außerdem wird in der Anforderungsspezifikationauch die Hardware-Plattform (CPU-Typen, Kommunika-tionsgeräte) und -Topologie definiert. Es wird eine festeVerteilung von Prozessen auf die Knoten im System vor-ausgesetzt. Insbesondere werden auch die Kommunikati-onsverbindungen zwischen den einzelnen Prozessen mitihren Eigenschaften spezifiziert.

Der komplette gültige Entwurfsraum des konfigurier-baren Betriebssystems wird mit Hilfe eines sogenanntenUND/ODER-Dienstabhängigkeitsgraphen in einer Wis-sensbasis spezifiziert [5]. Der Konfigurationsprozessvervollständigt dieses domänenspezifische Wissen un-ter Zuhilfenahme der Anforderungsspezifikation. Dabeiwird dann eine Konfiguration einer Laufzeitplattform au-tomatisch für ein konkretes verteiltes System erstellt.Diese Integration der Wissensbasen kann als Wissen-stransfer von der Anwendung hin zum Betriebssysteminterpretiert werden.

2

Eine große Klasse eingebetteter HW/SW Syste-me steht nicht nur mit zeitdiskreten Systemen, sondernauch mit kontinuierlichen Prozessen in der Umge-bung in Wechselwirkung, oder enthält selbst konti-nuierliche Teile. Die systematische Entwicklung undinsbesondere das Erfassen von Anforderungen an sol-che diskret-kontinuierliche oderhybride eingebetteteSysteme erfordert Beschreibungstechniken, die es er-lauben, die Wechselwirkung der diskreten und kon-tinuierlichen Aspekte eines Systems unmittelbar zubeschreiben und zu validieren. Sicherheitskritische An-wendungen, wie z.B. das Bremssystem eines Zuges in derAbbildung, erfordern darüber hinaus mathematisch fun-dierte Systembeschreibungen, die als Grundlage fürformale Verifikationsverfahren geeignet sind und im Rah-men des SPP erarbeitet wurden.

Institut für Informatik (Prof. Dr. M. Broy), TechnischeUniversität München

Die Arbeit am Institut für Technik der Informationsver-arbeitung an der Universität Karlsruhe beschäftigte sich

mit der Entwicklung einer durchgängigen Entwurfsmetho-dik für eingebettete Systeme. Die Methodik wurde in ei-ner umfangreichen Fallstudie getestet, bei der der gesamteEntwurfsweg für einen automatischen Probennehmer (Au-tosampler, siehe folgende Abbildung) für ein chemischesAnalysegerät erfolgreich verifiziert werden konnte.

Institut für Technik der Informationsverarbeitung (Prof.Dr. K. D. Müller-Glaser) Universität Karlsruhe

Gegenstand der Arbeit an der Technischen Universi-tät Ilmenau war der modellbasierte Entwurf der Hard-und Software für eingebettete Systeme, die bei innovati-ven Mehrkoordinatenantrieben zur Anwendung kommen.Hier werden Funktionen, die in konventionellen Lösungendurch mechanische Baugruppen ausgeführt werden, durcheingebettete Systeme übernommen. Dabei wurde beson-ders Augenmerk auf Fragen der Validierung und Verifi-kation gelegt. Die folgende Abbildung zeigt die schema-tische Darstellung eines planaren Mehrkoordinatenantrie-bes.

Theoretische und Technische Informatik (Prof. Dr. W.Fengler), Technische Universität Ilmenau

Die Abbildung unten zeigt ein elektrohydrauli-

iv

sches Bremssystem von Continental-Teves, das alsAnwendungsbeispiel für die an der Johann Wolf-gang Goethe-Universität Frankfurt/Main entwickeltenBewertungs- und Analyseverfahren dient. Ziel der Ar-beiten im SPP Projekts waren Bewertungsverfahren, umbestimmte Realisierungsvarianten eines Systems mitein-ander zu vergleichen und mit vertretbarem Zeitaufwandzu einer nahezu optimalen Lösung zu gelangen. Für ei-ne dynamische Bewertung wurde eine Bibliothek zurSimulation gemischt analog/digitaler Schaltungen mit Sy-stemC und ein Konzept zur Modellierung von Toleranzenentwickelt. Diese Arbeit fließt derzeit in die Standardisie-rung von SystemC-AMS ein.

Technische Informatik (Prof. Dr. K. Waldschmidt) Jo-hann Wolfgang Goethe - Universität Frankfurt am Main

Aufgrund von Produktionsschwankungen erfül-len nicht alle gefertigten Systeme die an sie gestelltenAnforderungen. Deshalb muss im Anschluss an die Ferti-gung ein Test durchgeführt werden, um fehlerhafte Teilevor ihrer Auslieferung zu identifizieren und auszusortie-ren. In diesem Projekt wurden Verfahren erforscht, umsolche Tests für analoge Systemkomponenten zu ent-werfen. Ausgangspunkt war dabei die Simulierbarkeitdes Problems am Rechner, um bereits zu einem frü-hen Zeitpunkt des Systementwurfs den Test vorbereitenzu können. Als Ergebnis liegen Verfahren für den prakti-schen Einsatz bereit, die den besonderen Anforderungenbeim Test analoger Komponenten genügen. Insbesonde-re können nun für schwer zugängliche Schaltungen ge-eignete Testmessungen zum Einsatz kommen, die einenzuverlässigen Schluss auf die Funktionstüchtigkeit er-lauben. Die Abbildung unten zeigt die Layoutskizze desGSM-Basisband-Chips von Infineon Technologies im Sie-mens S45 Handy, der analoge (umrandet) und digitaleKomponenten enthält.

Lehrstuhl für Entwurfsautomatisierung (Prof. Dr. K.Antreich), Fakultät für Elektrotechnik und Informations-technik, Technische Universität München

analoges System

20% der Fläche

80% der Kosten

GSM Basisba

Infineon Technol

Der Entwurf von eingebetteten Systemen mit ei-nem Produktionsvolumen mittlerer Stückzahl umfasstin Deutschland einen sehr großen Markt, der internatio-nal steigendem Wettbewerb ausgesetzt ist. Die Arbeitenam Lehrstuhl für Realzeit-Computersysteme der Techni-sche Universität München beschäftigten sich mit der Fra-ge, wie das enorme Optimierungspotenzial, das in derEntwurfsphase dieser Systeme steckt, genutzt wer-den kann. Dazu wurde ein Meta-Modell basierendesFramework entwickelt, dass insbesondere die Explora-tionsphase mit einer strukturierten und differenziertenMethodik unterstützt. Die Abbildung zeigt den vorge-schlagenen Entwurfsablauf.

Lehrstuhl für Realzeit- Computersysteme (Prof. Dr. G.Färber), Technische Universität München

KundePflichtenheft

erzeugt

Ingenieur

Reuse Anforderungen

Lastenheft

erstellt

System Anforderungen

Einsetzbare Komponenten AbhängigkeitenATLAS

schlägt vor zeigt

initialisiert

Ausgewählte Komponenten

verarbeitet

System Entwickler

liest

leitet ab

interagiert

bestimmt

Erfahrung

Der an der TU Braunschweig entwickelte Lösungsan-satz zur Verifikation von Systemperformanz basiert auf derKombination verschiedener Systemmodelle und Verfahren

v

zur Performanzanalyse, so dass Performanzaussagen auchfür komplexe, heterogene Systeme ermöglicht werden, fürdie keine einheitliche Lösung zur Verfügung steht. Hier-zu entstanden im Rahmen des SPP das SPI-Modell sowiedas Werkzeug SymTA/S (Abbildung).

Institut für Datentechnik und Kommunikationsnet-ze (Prof. Dr. R. Ernst), TU Braunschweig

Komplexe eingebettete Systeme wie mobile Kommu-nikationsgeräte, Industriesteuerungen, Medizintechnik,etc. sind von Natur aus meist heterogen. Innerhalb ei-ner Kooperation zwischen der Universität Erlangen,der TU Braunschweig, der ETH Zürich und der Prince-ton University ist das SPI-Modell entstanden, das in derLage ist derartige Systeme zu beschreiben. Das folgen-de Bild zeigt ein Beispiel einer solchen Beschreibung mitihrer Abbildung auf eine reale Architektur.

Lehrstuhl für Hardware- Software-Co-Design (Prof.Dr. J. Teich), Universität Erlangen-Nürnberg

P1

1C

P2

C2

P3

a P1

C1d

P2a

dC2

P2a

sC2

C1s

C1r

r C2

lat P2, 2

lat P2, 1

lat C1, 2

lat C1, 1

lat P1, 1

lat C2, 2

lat P3, 2

lat C2, 1

lat P3, 1

lat P1, 2

Die an der Universität Oldenburg im Rahmen desSPP objektorientierte Co-Simulation für eingebette-te Steuerungssysteme (OOCOSIM) verfolgte das Zielder Entwicklung einer objektorientierten Entwurfsme-thodik für eingebettete Realzeitsysteme. Das Hauptzielwar die Konzeption einer objektorientierten Entwurfsme-thodik für eingebettete Realzeitsysteme, die von der ab-strakten Spezifikation bis zur Implementierung des zuentwickelnden Systems reicht. Von besonderer Bedeu-tung war dabei die Möglichkeit der abstrakten Spezi-fikation, um auch komplexe Systeme beherrschbar zumachen.Die OOCOSIM-Methodik beginnt mit der ab-strakten Modellierung auf Systemebene. Die Abbildungzeigt ein Modell einer Lüfterregelung in der Modellie-rungssprache HRT-HOOD+.

Department für Informatik, Eingebettete Hardware-Software-Systeme (Prof. Dr. W. Nebel) Universität Olden-burg

R Beispiel 1

Direction=hw_to_sw

Protected=off

Type=Temperatur_T

Type=Kommando_T

Protected=off

Direction=sw_to_hw

SY Prozessorlüftungsregelung

IRQ-Number = 12

AlarmS

Starte

Period = 40 ms

Priority = 5

WCET = 1 ms

Period = 20 ms

Priority = 4

WCET = 2 ms

MO

MO

C

AS

ASR_BY_I T

Lüfter_Defekt

C ÜberwachungTemperatur

Kommando

Min_Interval=100ms

hole_temp

setze_temp

setze_komm

hole_komm

Priority_min = 0

Priority_max = 15

Priority_min = 4

Priority_max = 6

Melde

KühlerH

H Messe_Temp

Prüfe_LüfterH

Rg_Lüfter_Geschw

vi

Projekte des Schwerpunktprogramms1. Einleitung

2. Versatile Digital Architecture, Institut für Informatik,Universität Leipzig (Prof. Dr. U. Kebschull)

3. Entwurf und Bewertung eingebetteter Systeme, Wilhelm Schickard Institut, Universität Tübingen (Prof. Dr. W. Rosenstiel)

4. Komponentenbasierte Entwicklung eingebetteter Systeme, Institut für Automatisierungs- und Softwaretechnik, Universität Stuttgart (Prof. Dr. P. Göhner)

5. Entwurf konfigurierbarer, echtzeitfähiger Kommunikationssysteme, Heinz Nixdorf Institut, Universität Paderborn (Prof. Dr. F. Rammig)

6. BeQuest: Beschreibung und formale Qualitätssicherung für eingebettete Systeme, Institut für Informatik, Technische Universität München (Prof. Dr. M. Broy)

7. Durchgängige Entwurfsmethodik dezentraler Steuerungselemente für mechatronischeSysteme in der Automatisierungstechnik (DESSY), Institut für Technik der Informationsverarbeitung, Universität Karlsruhe (Prof. Dr. K. D. Müller-Glaser)

8. Entwurf eingebetteter paralleler Steuerungssysteme für integrierte multi-axiale Antriebssysteme, Theoretische und Technische Informatik, Technische UniversitätIlmenau (Prof. Dr. W. Fengler)

9. Bewertung und Analyse hybrider Systeme, Technische Informatik, Johann Wolfgang Goethe - Universität Frankfurt am Main (Prof. Dr. K. Waldschmidt)

10. Simulationsbasierter Testentwurf analoger integrierter Systemkomponenten, Lehrstuhl für Entwurfsautomatisierung, Technische Universität München (Prof. Dr. K. Antreich)

11. Template-basierte Entwicklung von eingebetteten Systemen, Lehrstuhl für Realzeit-Computersysteme, Technische Universität München (Prof. Dr. G. Färber)

12. Kombination von Sprachen und Berechnungsmodellen für die Synthese eingebetteter Systeme, Institut für Datentechnik und Kommunikationsnetze, TU Braunschweig (Prof. Dr. R. Ernst)

13. SPI-Workbench: Modelle und Verfahren zur Analyse, Synthese und Optimierung von gemischt reaktiv/transformativen eingebetteten Systemen, Lehrstuhl für Hardware-Software-Co-Design, Universität Erlangen-Nürnberg (Prof. Dr. J. Teich)

14. Objektorientierte Cosimulation eingebetteter Steuerungssysteme, Department für Informatik, Eingebettete Hardware-Software-Systeme, Universität Oldenburg (Prof. Dr. W. Nebel)

2

5

9

13

17

21

25

29

33

37

41

45

49

53

1

Einleitung

Das hier zusammenfassend vorgestellte von der DFG geförderte Schwerpunktprogramm “Ent-wurf und Entwurfsmethodik eingebetteter Systeme” hat vor allem die Methodik für den System-entwurf eingebetteter Systeme erforscht und weiter entwickelt, sowie bei konkreten Anwendun-gen exemplarisch eingesetzt.

Als eingebettete Systeme(engl.: embedded systems)bezeichnet man im Allgemeinen elek-tronische Systeme, die in größere Systeme oder Umgebungen integriert sind. Sie werden fürspezielle Anwendungen entworfen und können sowohl aus Mikrocontrollern, als auch aus denfür die jeweilige Anwendung entworfenen Hard- und Software-Komponenten bestehen.

AutomobilindustrieUnterhaltungselektronik

Robotik und AutomatisierungLuft− und RaumfahrtTelekommunikation

Abbildung 1: Beispiele für eingebettete Systeme

Die Kombination von Methodenentwicklung mit exemplarischem Entwurf eingebetteter Sy-steme war ein besonderer Schwerpunkt dieses Schwerpunktprogramms. Der Entwurf eingebet-teter Systeme hat sich zu einem viel beachteten eigenständigen Forschungsgebiet entwickelt,dessen besondere Anforderungen sich aus der Optimierung des Zusammenwirkens heterogenerTeilsysteme ergeben. Dabei kam es in den durchgeführten Forschungsarbeiten nicht nur daraufan, dass das eingebettete System die gewünschte Funktion erfüllt, sondern dass darüber hinausvor allem Anforderungen bezüglich der gewünschten Leistung, der Kosten des Gesamtsystems,der Zuverlässigkeit, der Sicherheit, des Energieverbrauchs usw. erfüllt werden.

Ein wichtiger Punkt ist hierbei die Beherrschung der exponentiell wachsenden Komplexitätsolcher Systeme, deren Entwurf sich erheblich vom klassischen Software-Entwurf für Desktop-Anwendungen unterscheidet. Um derart komplexe eingebettete Systeme mit vertretbaren Kostenund in möglichst kurzer Zeit entwickeln zu können, werden neue Methoden entwickelt, die esdem Entwickler ermöglichen, Entwurfsanforderungen in einer möglichst frühen Phase des Ent-wurfs zu überprüfen, und die Entwurfskosten durch fortschrittliche Entwurfsmethodiken mög-lichst gering zu halten.

2

Neben der technischen Entwicklung eingebetteter Systeme sei auch auf die enorme wirt-schaftliche Bedeutung hingewiesen. Immer stärker entscheidet der Elektronik- und Software-Anteil (also das eingebettete System) über die gesamte Wertschöpfung neuer Produkte (vgl.Abbildung 2). Der Einsatz neuer Methoden im Entwurf komplexer Eingebetteter Systeme istsomit wettbewerbsentscheidend und kann für Betriebe in diesem Sektor überlebenswichtig sein.Typische Beispiele für eingebettete Systeme sind im Telekommunikationsbereich, der industriel-

Abbildung 2: Der relative Anteil der Wertschöpfung in der Automobiltechnik (Quelle: BMWAG)

len Automation und Robotik, der Unterhaltungselektronik, der Luft- und Raumfahrt und insbe-sondere der Automobilindustrie zu finden (Abbildung 1). Neben dem Trend zur Steigerung derKomplexität eingebetteter Systeme, ist auch der Trend zu steigender Kommunikation zwischenden heterogenen Komponenten eingebetteter Systeme und die durch die Mobilität hervorgerufenAnforderungen, wie Miniaturisierung und geringer Stromverbrauch zu beobachten.

Automobil−Industrie

Halbleiter

Automatisierung

ElektronikEntwicklungs−Werkzeuge

Messtechnik, Sensoren

Abbildung 3: Industriepartner im Schwerpunktprogramm

Im Schwerpunktprogramm “Eingebettete Systeme” sind 14 Projekte gefördert worden. Indiesem Zusammenhang entstanden mehr als 100 Publikationen und mehr als 20 Dissertationen.

3

• ETH Zürich (Prof. Thiele)

• EPFL Lausanne (Prof. Vachoux)

• FhG-IIS EAS Dresden (Prof. Schwarz)

• NTNU Trondheim (Prof. Ytterdal)

• Lehrstuhl für Prozessleittechnik PLT, RWTH Aachen (Prof. Epple)

• Universidade do Amazonas, Faculdade de Tecnologia, Manaus, Brasilien(Dr. Lucena)

• Lehrstuhl für Automatisierungstechnik / Prozessinformatik, Bergische Uni-versität Wuppertal (Prof. Vogel-Heuser)

• Federal University of Rio Grande do Sul, Porte Alegre, Brasilien (Prof.Pereira)

• Lehrstuhl für Automaten und Systemtheorie, HU Berlin (Prof. Grohe)

• Fachgebiet für Automatisierungsanlagen und Prozessleittechnik, TU Il-menau (Prof. Sawodny)

• C-Lab Paderborn

• FZI Karlsruhe

• Distributed Systems Technology Centre (DSTC), Australia

• ESO (European Southern Observatory)

Abbildung 4: Kooperationen zu Hochschulinstituten außerhalb des Schwerpunktprogramms

Erheblich zum Erfolg des SPP haben zahlreiche Kooperationen mit Industriepartnern bei-getragen. Dabei waren wichtige Branchen aus den Bereichen Automobilindustrie, Automatisie-rung, Messtechnik und Sensoren, Halbleiter, Elektronik und Entwicklungswerkzeuge vertreten(Abbildung 3). Kooperationen gab es zusätzlich zu deutschen und internationalen Hochschul-und Forschungsinstituten außerhalb des Schwerpunktprogramms (Abbildung 4).

Auf der beiliegenden CD stellen die einzelnen Teilnehmer des Schwerpunktprogramms ih-re Projekte und wichtigsten Ergebnisse zusammenfassend vor. Die Reihenfolge entspricht derReihenfolge der Vorträge beim Abschlusskolloquium des Schwerpunktprogramms, das im Rah-men eines Workshops bei der Robert Bosch GmbH in Leonberg im November 2003 veranstaltetwurde.

4

Versatile Digital Architecture

Carsten NitschInstitut für Informatik (Prof. Dr. U. Kebschull)

Universität Leipzig

1. Einleitung

Vor über 40 Jahren galten Computer noch als etwas Be-sonderes. Riesige Rechenmonster, wie die UNIVAC füll-ten ganze Häuser mit lärmenden Lochkartenlesern, Re-lais, Fernschreibern und ähnlichem Equipment. Wer zudieser Zeit eine Rechenmaschine betrieb, brauchte vielPlatz und eine leistungsfähige Energieversorgung. Kaumjemand glaubte ernsthaft daran, dass die Welt mehr als ei-nige wenige dieser Wunderwerke benötigen wird. Heutewissen wir, dass diese Prognose wahrscheinlich der größ-te Irrtum der Zukunftsforschung war.

Computer sind aus unserem Alltag nicht mehr wegzu-denken. Sie sind in der Arbeitswelt wie auch in Privathaus-halten weit verbreitet. Ein stetiger Preisverfall sorgt da-für, dass die Rechentechnik zum Alltagsgut wird. Im Ge-gensatz zu bekannten Desktopcomputern (Mac, Worksta-tion, PC) verlief die größte technische Revolution jedochweitgehend unbemerkt. Schauen wir uns einmal in unsererWohnung um. Wie viele Mikroprozessoren besitzen wir?Sind es fünf, zehn oder etwa doch viel mehr? Den we-nigsten Menschen ist bewusst, dass in Mobiltelefonen, Di-gitalkameras, Videorecordern und Autos Computer „ver-steckt“ sind. In der Fachliteratur hat sich für diese inte-grierten Systeme der Begriff „Eingebettetes System“ eta-bliert. Wenn wir moderne eingebettete Systeme betrach-ten, so werden folgende Dinge deutlich:

Denken wir einmal kurz darüber nach, welche Wün-sche wir selbst an unsere Geräte, z.B. Mobiltelefone, ha-ben. Diese haben mittlerweile eine eingebaute Kamera,Mikrofon, Kopfhörer und ein schönes farbiges Display, al-so im Prinzip alles, was der Rechner zu hause oder derLaptop auch besitzt. Warum sollte das kleine mobile Ge-rät nicht genauso leistungsfähig gemacht werden wie deroft unhandliche Laptop und trotzdem viele Stunden miteiner Akkuladung funktionieren? Wunschziel ist also einGerät, welches so leistungsfähig und flexibel ist wie „nor-male“ Rechner, welches wir aber problemlos ständig beiuns haben können.

Anderseits müssen wir aber auch die Probleme derHersteller betrachten, welche diese Geräte entwickeln,produzieren und verkaufen müssen. Aus deren Sicht mussein eingebettetes System vor allem ein Kriterium erfüllen– es muß preiswert zu entwickeln und zu fertigen sein. Da-

her ergibt sich die Notwendigkeit eines „Baukastenprin-zips“. Der Entwickler verfügt über eine Sammlung aus-getesteter Teilkomponenten für Video, Audio oder Telefo-nie Hardware. Aus diesen kombiniert er an seinem Ent-wicklungsrechner das fertige System, welches am Ende ineinen Spezialchip „gegossen“ und in die Geräte eingebautwird.

Ziel unserer Arbeiten war, wichtige Methoden zu er-forschen, die dazu beitragen können die beschriebenenWünsche in der Zukunft Wirklichkeit werden zu lassenund einmal Computer zu ermöglichen, welche

• klein, und leistungsfähig sind,

• wenig Strom verbrauchen,

• flexibel an neue Aufgaben anpassbar und letztlich,

• preiswert herzustellen sind.

Aufgrund der hohen Komplexität des Aufgabenfeldes wares natürlich nicht möglich, die Problematik allumfassendzu untersuchen. Wir haben uns daher auf die Untersuchungder allgemeinen Architektur von eingebetteten Systemenund deren Anbindung an ein Netzwerk beschränkt, wiedies im Abschnitt 3 detailierter beschrieben wird.

2. Situation am Anfang des Schwerpunkt-projektes

Zu Beginn des Projektes war die Welt der eingebettetenSysteme weit von den Visionen entfernt, wie sie in der Ein-leitung beschrieben wurden. Es gab schon damals Mobil-telefone, Video Set-Top Boxen, elektronische Übersetzerund vieles mehr. Die Geräte waren durchaus leistungsfä-hig, allerdings jeweils auf einen bestimmten Zweck ein-geschränkt. Das Telefon war nur zum Telefonieren zu ge-brauchen, das elektronische Wörterbuch nur zum Überset-zen usw. Wer viele Funktionen benötigte, musste auch ent-sprechend viele Geräte mit sich herumtragen. Warum wardies so? Um die Problematik zu verstehen, müssen wirkurz analysieren, wo die besonderen Probleme liegen eineingebettetes System zu entwickeln.

• Leistungsfähigkeit und Stromverbrauch: Aus Er-fahrung wissen wir, dass die Leistungsfähigkeit vonDesktopcomputern vor allem dadurch gestiegen ist,dass die Prozessoren immer schneller wurden. Waren

5

„früher“ Taktfrequenzen von 20MHz State–of–the–Art, so sind wir mittlerweile im Gigahertz–Bereichangelangt. Dafür können heute die Maschinen auchin Echtzeit Videos bearbeiten, was vorher undenkbarwar. Allerdings bringen schnelle Prozessoren ein Pro-blem mit sich. Der Stromverbrauch dieser Chips istsehr hoch und es passiert oft, dass das gerade gekauf-te tolle Multimedia Notebook nach nur einer Stun-de wegen des leer gelaufenen Akkus aufgibt. Wieman sieht, ist es also nicht möglich, einfach schnel-le Prozessoren in mobile Geräte zu bauen. Dies giltschon für Notebooks und verschärft sich für einge-bettete Systeme mit wenig Platz für den Akku nochmehr. Um dem Energieproblem zu entkommen, wer-den daher eingebettete Systeme schon immer oft mitSpezialchips ausgerüstet. Diese können im Gegensatzzum „normalen“ Prozessor oftmals nur wenige spe-zielle Aufgaben lösen, dies jedoch sehr schnell undmit geringem Energieverbrauch.

• Flexibilität und Kosten: Wie eben beschrieben,brauchen mobile eingebettete Systeme Spezialhard-ware, um leistungsfähig zu sein und dennoch we-nig Energie zu verbrauchen. Allerdings lassen sichauf diesen Bausteinen nur eine begrenzte Men-ge an Funktionen unterbringen. Dies schränkt na-türlich die Benutzbarkeit des Gerätes ein. Wennein MP3 Player einen Chip besitzt, der die Musik-stücke nur abspielen kann, so ist es nicht möglich dasGerät auch als Recorder zu benutzten. Dazu müss-ten nämlich auch die dazu notwendigen Funktionenauf den Chip „gebrannt“ werden, was ihn natür-lich teurer macht. Wie man leicht sehen kann, ist esaus Kostengründen erst einmal nicht praktikabel je-de gewünschte Funktion im Chip bereitzustellen.Ein weiteres Problem besteht darin, dass sich klas-sische Chips, so genannte ASICs, nur bei ihrer Her-stellung programmieren lassen und später nicht mehrveränderbar sind.

Zu Beginn des Schwerpunktprogramms wurden die meis-ten eingebetteten Geräte mit den eben beschriebenenASICs bestückt. Dennoch gab es schon damals eine Al-ternative zum fest verdrahteten Chip. VerschiedeneHersteller boten so genannte FPGA Chips (Field Pro-grammable Gate Array) an. Im Unterschied zu denASICs kann man FPGAs immer wieder neu programmie-ren. Je nach Programmierung kann solch ein Chip dannzur Wiedergabe von Musik oder auch von Videos die-nen. Trotz dieser Programmierbarkeit ist er dabei jedochfast genauso stromsparend und schnell wie die klassi-schen ASICs.

An dieser Stelle wird klar, dass sich ein flexibles undstromsparendes Gerät realisieren lässt, wenn man es mitFPGAs oder anderer programmierbarer Hardware ausstat-tet. Obwohl diese Technik schon vor dem Schwerpunkt-programm existierte, wurde sie zu diesem Zwecke kaum

eingesetzt. Der Grund dafür war, dass es kaum Untersu-chungen der Methoden gab, auf welche Weise man dieFPGAs im Gerät des Anwenders geeignet programmierenkann. Im obigen Abschnitt wurde gezeigt, dass es nichtmachbar ist, eine sehr große Anzahl von Funktionen „amStück“ in einen Chip zu giessen. Dies gilt natürlich fürFPGAs genau so wie für ASICs, da auch die program-mierbaren Schaltkreise nur eine begrenzte Kapazität ha-ben und sich die Preise mit steigender Kapazität sehr starkerhöhen.

Wir haben daher im Schwerpunktprogramm nach Lö-sungen gesucht, wie man FPGAs nach Bedarf program-mieren kann. Ziel war es, eine Architektur zu finden, dieselbständig erkennt, welche Funktion sie ausführen muss(z.B. Musik abspielen), selbständig einen dafür geeigne-ten Programmcode für das FPGA findet und diesen insFPGA lädt, damit er anschließend benutzt werden kann.Selbstverständlich soll dies für den Benutzer weitgehendunbemerkt geschehen. Selbst wenn er verschiedenste Pro-gramme aufruft, also telefoniert, fotografiert oder Brie-fe schreibt, soll sich der Spezialchip in Form des FPGAständig blitzschnell umprogrammieren und somit stets alsleistungsfähiger, energiesparender aber anpassungsfähigerSchaltkreis arbeiten.

3. Unsere Arbeiten: Die Versatile Digital Ar-chitecture

Um die Probleme zu lösen, haben wir Methoden und Mo-delle für eine neuartige Generation von eingebetteten Sys-temen entwickelt. Wir nennen diese Architektur „VersatileDigital Architecture“ (VDA).

Um die oben beschriebene Methoden bereitzustellen,mussten wir folgende Hauptprobleme lösen:

1. Wie muss das eingebettete System aufgebaut sein?

2. Wie findet das eingebettete System die jeweils benö-tigten Programmkomponenten? Wie lassen sich fürdiesen Zweck Internet Technologien verwenden?

Der erste Schwerpunkt wird im folgenden Abschnitt„VDA Client“ beschrieben und beschäftigt sich mit demeingebetteten System selbst, welches der Benutzer bei sichhat, z.B. sein Mobiltelefon. Der zweite Schwerpunkt be-schreibt die Methoden, diesen Client in ein Netzwerk wiedas Internet zu integrieren. Es werden Methoden vor-gestellt, die den Client mit einem Management Systemvernetzen. Dieses besteht aus einer Vielzahl von Ser-vern. Diese Server sind leistungsfähige Rechner, ähnlichwie Webserver. Im Gegensatz zum Webserver ermög-licht das Management System aber die automatischeSuche nach oben beschriebenen Programmkomponen-ten.

6

3.1. VDA Client – Das eingebettete System

Rekonfigurierbare Hardware

CPUFlash

RAM

Netzwerk Interface

In der Abbildung ist schematisch dargestellt, aus welchenKomponenten unser Client aufgebaut ist. Neben den „nor-malen“ Bestandteilen eines jeden Computers wie Spei-cher und Prozessor ist der bereits beschriebene FPGAChip (hier Rekonfigurierbare Hardware) zu erkennen. DasFPGA ist das Herzstück unseres eingebetteten Systemsund die Voraussetzung für Geschwindigkeit und sparsa-men Stromverbrauch. Es gibt jedoch noch eine weiterewichtige Baugruppe, die Netzwerkschnittstelle. Dies kanneine Infrarot Schnittstelle sein, wie sie bereits in vielenMobiltelefonen verwendet wird. Möglich ist aber auch,moderne Funkanbindungen wie Bluetooth oder schnel-les Wireless LAN zu verwenden. Welche Technik kon-kret verwendet wird hängt hauptsächlich damit zusam-men, welchen Preis das Gerät haben darf. Allen gemein-sam ist aber ihr Zweck, nämlich der Datenaustausch mitden Servern des Management Systems. Wie dies geschiehtund auf welche Weise die unterschiedlichen Netzschnitt-stellen unterstützt werden, wird im Abschnitt „Manage-ment System“ beschrieben.

Wie funktioniert unser Client? Stellen wir uns vor, derBenutzer hat z.B. einen Web Browser geöffnet und besuchteine Seite, die multimediale Dienste anbietet. Vorstellbarist hier z.B. eine News Webseite, auf der auch Audio-kommentare oder Videosequenzen angeboten werden. DerAnbieter möchte diese Daten natürlich so bereit stellen,dass sie sich so schnell wie möglich herunterladen lassen.Zu diesem Zwecke existiert eine große Vielfalt an Kom-primierungs Technologien, die ständig verbessert werden.Sinnvollerweise benutzt der Anbieter die neueste Versiondieser Kompressionsverfahren. Allerdings muss das Sys-tem des Benutzers, der VDA Client, diese Daten auch ver-stehen können, um sie darzustellen. Er benötigt also nebenden Multimedia Inhalten selbst auch noch Programmcodefür den Prozessor und das FPGA. Aufgrund der Vielfaltvon verschiedenen Prozessoren und FPGAs kann es nunnicht die Aufgabe der Nachrichten Webseite sein, auchnoch all diese Programme bereitzustellen. Vielmehr lie-gen diese auf den Servern des Management Systems. DerClient stellt also eine Anfrage an das System, in dem er be-schreibt, welchen Programmcode er benötigt (z.B. Versi-on 4.1 der Komprimierungs Software) und teilt weiterhin

mit, welchen Prozessor, welchen FPGA Typ usw. er ent-hält. Das System sucht dann nach geeignetem Code undschickt diesen an den Client. Dieser kann ihn von nunan benutzen und z.B. den Film darstellen. Um nicht je-des mal das Management System kontaktieren zu müssen,besteht die Möglichkeit, den Programmcode lokal im Ge-rät zu speichern.

3.2. Das Management System

Client

Rekonfigurierbare Hardware

CPUFlash RAM

Netzwerk Interface

(1) Auswahl der Anwendung (2) Was wird gebraucht?

<options>

<application> <spectype>external</spectype> <url><http://myserver.com/application.xml></url> </application>

<architecture> <id>123456789</id> <cpu> <family>SuperH</family> <type>SH3</type> <clock>130Mhz</clock> </cpu <os> <name>vxworks</name> </os> </architecture>

</options>

XML Dokument

Embedded Management

(3) Komponenten-Suche(4) Konfiguration & Start

Bean

DirectoryServices

Internet

Um den Aufbau des Management Systems zu verstehen,muss man sich zuerst einmal vergegenwärtigen, welcheAnforderungen auf ein solches System zukommen. Esexistiert eine sehr große Anzahl verschiedener eingebette-ter Systeme. Auch wenn wir in der Definition des VDAClient festgelegt haben, dass ein solches System übereinen Prozessor, programmierbare Hardware, ein Netz-werkinterface usw. verfügen muss, haben wir aus praxis-bezogenen Gründen bewusst offengelassen, von welchenHerstellern die Chips sein sollen und welche konkretenTypen verwendet werden. Das Management System mussdaher in der Lage sein, eine sehr große Versionsvielfalt zuverwalten. Ein weiteres Problem erkennt man, wenn mansich die große Anzahl von eingebetteten Systemen vor Au-gen hält. Allein Mobiltelefone existieren zu vielen Millio-nen.

Aus diesen Gründen kann kein zentraler Server al-lein die Management Aufgaben übernehmen. Selbst diebesten Hochleistungscomputer wären damit überfordert.Vielmehr muss die Aufgabenflut an viele einzelne Ser-ver verteilt werden. Wichtig ist dabei, dass diese Vertei-lung gleichmäßig erfolgt. Wir verwenden daher für un-ser Management System ein dezentrales Topologie Mo-dell. Neben den eben beschriebenen Lastproblemen galtes aber noch weitere Anforderungen zu erfüllen. So mussdas System in der Lage sein, Fehler während der Über-tragung erkennen und korrigieren zu können. Es muss si-chergestellt werden, dass z.B. nur vertrauenswürdige Ser-ver angesprochen werden und dass keine „Hackermaschi-nen“mit gefälschten Adressen Viren statt Programme ver-teilen. Glücklicherweise existierten bereits Lösungen, diezumindest einen Teil der beschriebenen Probleme schongelöst haben. Um das Rad nicht neu erfinden zu müssen,haben wir uns entschieden, auf solch einer Lösung aufzu-

7

bauen und sie so zu erweitern, dass sie unseren Ansprü-chen gerecht wird.Diese Technologie ist unter den Namen „Enterprise JavaBeans“ (EJB) bekannt. EJB baut auf der Java Technolo-gie der Firma SunTM auf. Java hat den Vorteil, dass einin dieser Sprache geschriebenes Programm auf den unter-schiedlichsten Systemen läuft, die Java unterstützen. Al-lerdings wird dieser Vorteil damit erkauft, dass man stetsetwas mehr an Prozessorleistung und Speicher benötigt.Für kleine eingebettete Systeme ist daher Java Unterstüt-zung aus Kostengründen nicht immer möglich. Wir habenallerdings eine Möglichkeit gefunden auch diese Gerätean unser System anzubinden. Dazu haben wir sogenann-te „Accesspoints“ in unser System integriert. Ein Access-point ist ein Computer, der sowohl Java beherrscht als auchmit dem einfachen Client kommunizieren kann. Beispiels-weise könnte der heimische Internet PC als Access Pointdienen. Das elektronische Notizbuch des Benutzers könn-te dann über eine einfache Infrarot Schnittstelle mit demPC kommunizieren und dieser reicht diese Anfragen dannzum Management System weiter. Access Points kann mansich also am besten als Vermittler zwischen eingebettetenSystem und Management Schicht vorstellen.

4. Ergebnisse/Erfahrungen

Wir haben mehrere einfache Prototypen entwickelt undmit ihnen unser System unter Laborbedingungen getestet.

Client Server

Thin Client(SH3 Board)

Access Point(Linux Box)

HTTPS Server

EJB Client EJB Server

opt.xmlres.xml

Eine Aufgabe der Tests war herauszufinden, wie das Sys-tem funktioniert, d.h. z.B. wie schnell es auf Anfragenreagiert. Als eingebettetes System diente dazu eine Expe-rimentierplatine mit einem Prozessor (SH3 von Hitachi)und einem FPGA (Virtex von Xilinx). Auf diesem Systemlief kein Java. Daher erfolgte die Kommunikation mit demManagement System über einen Access Point, in unseremFall einen PC. Die Kommunikation vom Experimentier-board zum PC erfolgte in HTTP, dem gleichen Protokoll,wie es auch im WWW verwendet wird. Der PC wieder-um reichte die Daten an das Management System weiter,welches durch einen EJB Server bereitgestellt wurde. Zieldes Experiments war, dass das eingebettete System Pro-grammcode anforderte, um das FPGA zu programmieren.Diese Anfrage erging an das Management System, wel-ches dann aus einer Datenbank die Code Komponente aus-wählte, die auf dem FPGA lauffähig war.

• Ergebnis: Die Zeit, die für Anfrage, Übertragung,verschiedene Initialisierungen und Datenbankabfra-gen benötigt wurde, lag bei ca. 1 Sekunde.

Ein anderes Experiment beschäftigte sich mit den Mög-lichkeiten der Energieeinsparung. Dazu programmiertenwir ein Testprogramm einmal für den Mikroprozessor undeinmal für das FPGA. Bei den anschließenden Probeläu-fen haben wir gemessen, wie groß die jeweiligen Rechen-zeiten sind und zum anderen den Stromverbrauch festge-stellt.

• Ergebnis: Im Experiment war das FPGA ca.2400mal schneller als der einfache Prozessor. Umden Stromverbrauch zu vergleichen haben wir er-rechnet, wieviel Energie (gemessen in Wattsekun-den) der Prozessor bzw. das FPGA pro „Rechen-schritt“ verbrauchen. Dabei mussten wir feststellen,dass das FPGA (1 × 10−8 Ws) trotz höherer Ge-schwindigkeit nur ca 1/1000 der Energie verbrauchtwie der Prozessor (1×10−5 Ws).

5. Fazit

Wir haben ein System aus Methoden entwickelt, die es er-möglichen können, zukünftige eingebettete Systeme ge-nau so leistungsfähig und flexibel zu gestalten wie es bis-her nur mit herkömmlicher Rechentechnik möglich ist.Unsere Labortests haben gezeigt, dass diese Metho-den prinzipiell funktionieren und daher erfolgverspre-chend sind. Zukünftige Arbeiten werden zum Ziel haben,dieses System weiter zu verbessern. Insbesondere wür-den wir uns auf Kooperationen mit Industriepartnernfreuen, um das System auch im praktischen Einsatz tes-ten zu können.

6. Weitere Informationen

Im Rahmen dieser Zusammenfassung konnte das Projektnatürlich nur kurz umrissen werden. Ausführliche Infor-mationen finden sich in unseren Veröffentlichungen:

Literatur

[1] NITSCH, LARA, KEBSCHULL: A Novel Design Technolo-gy for Next Generation Ubiquitous Computing Architectu-res. In: IPDPS RAW, Nice, 2003.

[2] LANGE, KEBSCHULL: Virtual Hardware Byte Code as aDesign Platform for Reconfigurable Embedded Systems. In:Proceedings of the Design Automation and Test in EuropeConference (DATE2003), München, 2003.

[3] NITSCH, KEBSCHULL: The Use of Runtime ConfigurationCapabilities for Networked Embedded Systems. In: Procee-dings of the Design Automation and Test in Europe Confe-rence (DATE2002), Paris, 2002.

[4] NITSCH, KEBSCHULL: Konzeption einer virtuellen, offe-nen, echtzeitfähigen Systemarchitektur. In: Workshop Mo-delltransformation und Werkzeugkopplung, Braunschweig,2001.

8

Entwurf und Bewertung eingebetteter Systeme

Axel Siebenborn, Stephen SchmittWilhelm-Schickard Institut für Informatik (Prof. Dr. W. Rosenstiel)

Universität Tübingen

Zusammenfassung

Beim Entwurf eingebetteter Systeme wird eine Evalu-ierung des Systems zu einem möglichst frühen Zeitpunktim Entwurfsprozess angestrebt. Im Folgenden werden un-terschiedliche Methodiken vorgestellt, die eine Überprü-fung der an das System gestellten Anforderungen zu ei-nem frühen Zeitpunkt im Entwurfsablauf erlauben. ZumEinen werden analytische Methoden besprochen, mit de-nen die zeitlichen Eigenschaften von Software in einge-betteten Systemen analysiert werden können. Insbesonde-re können hiermit Schranken für denWorst-Caseermitteltwerden. Eine andere Methodik ist die Validierung durchEmulation, wodurch die Funktionalität von Systemkompo-nenten unter realen Bedingungen getestet werden kann.Hierzu wurde eine Emulationsumgebung entwickelt.

1. Einleitung

Eingebettete Systeme unterscheiden sich in verschiede-nen Bereichen von sogenannten Desktop-Systemen. Siesind Teil eines größeren Systems, in das sieeingebet-tet sind und mit dem sie unter mehr oder weniger stren-gen Zeitbedingungen interagieren. Die Evaluierung einessolchen Systems zu einem möglichst frühen Zeitpunktim Entwurfsprozess ist ein wesentlicher Faktor hinsicht-lich der Wirtschaftlichkeit eines Entwurfs. Zum Einenkönnen teure Redesignzyklen vermieden, und die Zeitbis zur Markteinführung eines Produkts (time to mar-ked) verkürzt werden. Zum Anderen kann eine frühzeiti-ge Evaluierung die Auswahl geeigneter Systemkomponen-ten vereinfachen und eine Überdimensionierung einzelnerKomponenten vermeiden. Im Besonderen müssen hier-bei aber die Zeitbedingungen betrachtet werden, da derenVerletzung zu Fehlfunktionen und Systemausfällen führenkann, was in sicherheitsrelevanten Bereichen schwerwie-gende Folgen nach sich ziehen kann. Hierbei sind heuri-stische Verfahren, wie Simulation nicht ausreichend, danur schwer alle möglichen Situationen – Eingabedaten desSystems – betrachtet werden können. Durch analytischeVerfahren können Grenzen für denWorst-Caseangegebenwerden, die für alle möglichen Kombinationen der Einga-bedaten Bestand haben und somit das Einhalten der Zeit-schranken garantieren. Diese analytisch bestimmten Gren-zen helfen eine Überdimensionierung des Systems zu ver-meiden.

Durch Emulation kann die Funktionalität von System-komponenten im System überprüft werden, ohne dass die-se bereits vorhanden sind. Der Vorteil gegenüber der Si-mulation liegt hier darin, dass keine Testvektoren gene-riert werden müssen.

Im folgenden Abschnitt wird auf die analytische Be-stimmung der zeitlichen Eigenschaften von Software ineingebetteten Systemen eingegangen. Hierbei wird zuerstdie Bestimmung derWorst-Case Execution Time(WCET)von Softwareteilen, die ohne Unterbrechung ausgeführtwerden betrachtet. Darauf folgend wird die Untersuchungdes Einflusses blockierender Kommunikation durch Kom-munikationsanalyse erläutert. Abschnitt 3 behandelt dieEmulation mit dem im Förderzeitraum entstandenen Emu-lationssystemSpyder .

2. Analytische Bestimmung der zeitlichenEigenschaften von Software in eingebette-ten Systemen

2.1. Statische Laufzeitanalyse

Eingebettete Systeme sind oft reaktive Systeme, dieInformationen in einem bestimmten Zeitraster bearbeitenund Ergebnisse zur Verfügung stellen müssen. AnalytischeLeistungsbewertung von Softwareimplementierungen aufeingebetteten Mikrocontrollern sind deshalb von essenzi-eller Bedeutung. DieStatische LaufzeitanalyseverknüpftInformationen über den möglichen Programmfluss mitInformationen über die Prozessorarchitektur, um darausworst-case-Laufzeitabschätzungen zu generieren. Hierbeisind im Allgemeinen zwei Teilaspekte zu betrachten.

• Eine genaue Modellierung der Eigenschaften des ein-gebetteten Prozessors.

• Die Ermittlung des Pfades im Programm, der zurlängsten Ausführungszeit führt.

Eigenschaften moderner Prozessoren wie Caches, Pi-pelines und Sprungvorhersage, tragen in hohem Maßezur Erhöhung der Verarbeitungsgeschwindigkeit bei. Die-se Eigenschaften müssen jedoch auch bei der Analyse be-rücksichtigt werden, um ausreichend genaue Ergebnissezu erzielen. Werden Prozessorarchitekturen mit Befehls-und Daten-Caches eingesetzt, so variieren die Laufzeitendurch einzelne Programmteile, je nachdem ob sie schonim schnellen Cache-Speicher vorhanden sind (Cache-Hit),oder noch aus dem langsamen Haupt-Speicher geladen

9

werden müssen (Cache-Miss). Bei der Statischen Lauf-zeitanalyse muss dementsprechend die Anzahl an Hits undMisses möglichst genau bestimmt werden.

Durch Pipelines und parallele Ausführungseinheitenwird eine überlappende Befehlsabarbeitung, bzw. paralle-le Befehlsverarbeitung erreicht. Bei der Analyse muss die-se mögliche Parallelität betrachtet werden. Hierbei müs-sen jedoch Datenabhängigkeiten zwischen Befehlen be-rücksichtigt werden, z.B. wenn der Operand eines Be-fehls von dem Ergebnis eines vorherigen Befehls abhängt.Durch Verzweigungen (Sprünge) wird diese überlappen-de Befehlsverarbeitung unterbrochen, weshalb in moder-nen Prozessoren Verfahren zur Vorhersage des Sprung-ziels eingesetzt werden. Ziel dieser Sprungvorhersage istdie richtige Vorhersage des Sprungziels in möglichst vie-len Fällen, um eine Unterbrechung der Pipeline zu ver-meiden. Bei der Laufzeitanalyse muss deshalb bestimmtwerden, in wievielen Fällen die Vorhersage der Sprung-vorhersage richtige und falsche Ergebnisse liefert, da sichdies auf die Laufzeit eines Programms auswirkt. Bei derBerücksichtigung all dieser Eigenschaften ist jeweils derWorst-Case, also der Fall zu betrachten, der zur maxima-len Ausführungszeit führt.

Abbildung 1. Steuerflussgraph eines Beispiel-programms

Abbildung 1 zeigt einen Flussgraphen für eine einfa-che Funktion auf der Basis des Maschinencodes auf dereinen Seite und die bei der Analyse zu betrachtenden Ei-genschaften des eingebetteten Prozessors auf der anderenSeite. Die Knoten des Graphen stellen die Basisblöcke, dieKanten die möglichen Programmpfade dar. Die Ausfüh-rungszeiten der Basisblöcke wird durchci und die Anzahlder Durchläufe durch die einzelnen Basisblöcke durchxi gekennzeichnet. Die Worst-Case-Ausführungszeit er-rechnet sich durch Aufsummieren aller Ausführungszei-ten beim Durchlaufen des Worst-Case-Ablaufpfades. Die-ser Algorithmus widerspiegelt sich in der Zielfunktion desganzzahligen linearen Optimierungsproblems.

twcet = max∑i

cixi (1)

Die Nebenbedingungen des Optimierungsproblems wer-den aus der Struktur des Flussgraphen gewonnen. Im Fallvon Schleifen sind weitere Nebenbedingungen nötig, diedie Anzahl der Schleifeniterationen begrenzen.

Wie bereits erwähnt wurde, unterscheidet sich die Aus-führungszeit eines Basisblocks erheblich, je nachdem obdie Befehle aus dem Cache oder aus dem Hauptspeichergeladen werden müssen. Dementsprechend muss die Ziel-funktion des Optimierungsproblems dahingehend erwei-tert werden, dass die unterschiedlichen Ausführungszeitenberücksichtigt werden:

twcet = max∑i(chit

i xhiti +cmiss

i xmissi ) (2)

Zur Lösung des Optimierungsproblems werden nun zu-sätzliche Nebenbedingungen benötigt, um die Anzahlder Cache-Hitsxhit

i und die Anzahl der Cache-Missesxmiss

i zu bestimmen. Diese werden aus zusätzlichen Gra-phen, dem Cache-Konfliktgraph (CCG) und demCache-Zustandsübergangsgraph, gewonnen. Detailsüber das Verfahren können den entstandenen Publika-tionen [1, 2, 3, 4] und der Dissertation mit dem Titel“Analytische Modellierung und Bewertung von Prozes-soren in eingebetteten Systemen” [5] entnommen wer-den.

In Abbildung 2 sind die Ergebnisse von Laufzeitmes-sung und WCET-Analyse für den Infineon C167 undverschiedene Benchmarkprogramme vergleichend dar-gestellt. Die Abschätzung ist in allen Fällen konservativ(Worst-Case-Bedingung) und der Fehler verhältnismä-ßig klein. Zum Vergleich ist in Abbildung 3 das Analyse-ergebnis für den PowerPC MPC750 dargestellt. Mit denneuen Verfahren für die Architekturmodellierung konn-ten auch für diesen relativ komplexen Prozessor guteAnalyseergebnisse erzielt werden.

0

2000

4000

6000

8000

10000

12000

14000

16000

check_data circle jfdctint line

Zyk

len Messung

Analyse

Abbildung 2. Vergleich zwischen Messung undAnalyse für den Siemens C167

In diesem Zusammenhang ist das prototypische Werk-zeug GROMIT entstanden. Prozessoreinstellungen könnenhierbei sehr einfach über eine graphische Oberfläche ein-gestellt werden und Worst-Case-Laufzeiten für Program-me auf diesen Prozessoren berechnet werden.

2.2. Kommunikationsanalyse bei parallelen Pro-zessen

Oft sollen eingebettete Systeme mehrere parallele Auf-gaben erfüllen, die dabei dennoch zu einander in Bezie-

10

0

5

10

15

20

25

30

35

jfdctint

linelinpack

matcnt

matcnt2

motion

piksrtsort

cycl

es/in

stru

ctio

n

Messung

Analyse

Abbildung 3. Vergleich zwischen Messung undAnalyse für den Motorola MPC750

hung stehen. Es herrscht also ein hoher Grad an Neben-läufigkeit. Zur Analyse nebenläufiger Prozesse, die sichin ihrem Lauzeitverhalten durch blockierende Kommu-nikation gegenseitig beeinflussen, wird ein neuer Ansatzzur Kommunikationsanalyse, mit dem im vorherigen Ab-schnitt beschriebenen Ansatz zur Bestimmung von Worst-Case-Laufzeiten von Software-Tasks verknüpft. Das be-schriebene Verfahren zur Bestimmung von Worst-Case-Laufzeiten ist nur auf einzelne Tasks anwendbar, die unter-brechungsfrei ausgeführt werden. Kommunikationen, diedie Ausführung blockieren, können hierbei nicht berück-sichtigt werden. Der in [6] beschriebene Ansatz, erlaubtdie Analyse von Systemen, bestehend aus parallelen Pro-zessen, wobei Kommunikationen die Ausführung der ein-zelnen Prozesse blockieren können. Für die Analyse wer-den die Kommunikationspunkte in den einzelnen Prozes-sen, sowie die Latenzzeiten zwischen den einzelnen Kom-munikationspunkten berücksichtigt. Zur Ermittlung dieserLatenzzeiten wird das bereits beschrieben Verfahren zurWCET-Analyse herangezogen. Das im Folgenden vorge-stellte Verfahren stellt dementsprechend eine Kombinationaus zwei Verfahren dar, die in unterschiedlichen Problem-domänen angesiedelt sind: Mit der statischen Laufzeitana-lyse werden minimale und maximale Laufzeiten für Code-Sequenzen mit Kontrollstrukturen, einschließlich Schlei-fen mit bekannten Grenzen analysiert. Für die Kommuni-kationsanalyse hingegen sind nur die Kommunikationenund das Laufzeitverhalten zwischen diesen Kommunikati-onspunkten interessant. Aus diesem Grund wird das Pro-blem in einem ersten Schritt in Teilprobleme für die ein-zelnen Bereiche zerlegt (Abbildung 4). Die Kommunikati-onsstruktur des Systems wird durch den Kommunikations-Abhängigkeits-Graph (KAG) dargestellt, wobei die Kom-munikationen die Knoten dieses Graphen repräsentieren.Kanten zwischen zwei Knoten im Graph existieren, wennim Kontroll-Fluss-Graph des Prozesses ein Pfad existiert,der die entsprechenden Kommunikationen verbindet, oh-ne jedoch weitere Kommunikationen miteinzuschließen.Auf Grundlage des KAG kann eine Bedingung formu-liert werden, die bei einseitig blockierender Kommunika-tionen erfüllt sein muss, um die beteiligten Prozesse zusynchronisieren. Es ist leicht einsehbar, dass eine Syn-

Kommunikations-Analyse

WCET-Analyse

Worst-caseZeit-Verhalten

KontrollflussKontrollfluss

KommunikationsKommunikations--strukturstruktur

?

ParalleleParallele ProzesseProzesse

ExecutionUnits

Register Instructionset

Pipeline

µC Architecture

Problem-aufteilung

F1 F2 F3

F5 F4

F1 F2 F3

F5 F4

Abbildung 4. Problemaufteilung auf die zweiBereiche Kommunikationanalyse und WCET-Analyse

chronisation nur dann stattfindet, wenn der blockierendeKommunikationspartner früher erreicht wird, als der nicht-blockierende Kommunikationspartner, so daß der Kom-munikationspunkt von den beteiligten Prozessen gleich-zeitig verlassen wird. Diese Bedingung lässt sich durchEinführung einer Schlupfvariablen als Gleichung darstel-len. Ziel dieser Betrachtung ist die Anzahl an Wartezyklenin den Empfangsknoten zu bestimmen. Ein negatives Er-gebnis bedeutet eine Verletzung der Synchronisationsbe-dingung und die betrachtete Kommunikation ist dement-sprechend kein Synchronisationspunkt.

Synchronisationspunkte setzen parallele Prozesse zeit-lich zueinander in Beziehung und erlauben so eine Be-stimmung derWorst-Case Response Time(WCRT) einessolchen Systems. Zur Bestimmung der Synchronisations-punkte wird ein lineares Gleichungssystem mit positivemLösungsraum gesucht. Kommunikationen, bei denen dieSynchronisationsbedingung nicht erfüllt ist, werden ausdem Gleichungssystem entfernt.

In aktuellen Arbeiten wird aufbauend auf den ermittel-ten Kommunikationspunkten eine Analyse durchgeführt,um Konflikte beim gemeinsamen Zugriff auf gemeinsamgenutzte Ressourcen zu erkennen [7].

3. EmulationsumgebungSpyder -System

Emulation ist eine effektive Methode, die Funktiona-lität eines Systems in seiner realen Umgebung zu testen.Der Vorteil gegenüber einer Simulation ist, dass keineTestvektoren generiert werden müssen. Damit diese Emu-lation eine hohe Aussagekraft und Akzeptanz bei denEntwicklern erhält, sind leistungsstarke Werkzeuge – dieEmulationsumgebungSpyder– definiert und implemen-tiert worden. DasSpyder -Emulationssystem besteht dabeiaus zwei Werkzeugen, welche von einem gemeinsamenBetriebssoftware-Paket in eine PC-basierte Entwicklungs-umgebung eingebunden werden. Im wesentlichen greiftdie Spyder-Betriebssoftware die Ausgangsprodukte vonState-of-the-Art-Entwicklungswerkzeugen für FPGA und

11

• Virtex-FPGA (XCV400-2000E)

• Konfiguration und Kommunikation über PCI-Bus

• Erweiterungsstecker mit bis zu 168Verbindungsmöglichkeiten

• On-board Speicher:• 2 x SDRAM: 4Mx32• 2 x SSRAM: 256Kx32

• Debugging• Mictor Logikanalysator Stecker• Chipscope ILA Kerne• 2 LEDs

Abbildung 5. Blockschaltbild und Foto des Spy-der -Virtex-Boards

Mikrocontroller auf und überträgt sie auf eine gemeinsameEmulationsplattform. Das Werkzeug Spyder-Core-P2 istdie zentrale Basis-Platine und dient der Emulation von ein-zelnen ASIC-Komponenten, der Emulation von Software-Komponenten sowie der abschließenden Systemintegra-tion aller Teilkomponenten eines eingebetteten Systems.Das Werkzeug Spyder-Virtex-X2e ist ein Hilfswerkzeugfür Spyder-Core-P2, welches insbesondere den Mikrocon-troller durch den Mikroprozessor des Entwicklungsrech-ners ersetzt. Die in diesem Teilprojekt durchgeführten Ar-beiten, führten zu mehreren Publikationen, unter anderemin [8, 9, 10, 11]. Eine detaillierte Abhandlung dieser Ent-wurfsmethodik und der Entwurfswerkzeuge ist in der Dis-sertation, “Architekturentwurf und Emulation eingebette-ter Systeme” [12] zu finden. Eine aktuelle Arbeit behan-delt die optimale Ressourcenausnutzung der Emulations-umgebung zur Behandlung komplexerer Hardwarekompo-nenten am Beispiel eines Mikrocontrollerkerns[18].

Die Emulationsumgebung fand großen Anklang beiHochschulinstituten und in der Industrie. Mehr als 50Boards sind sowohl in Forschung und Entwicklung, alsauch in der Lehre im Einsatz. Dies führte zu zahlrei-chen Kooperationen mit Industriepartnern und Hochschul-instituten innerhalb und außerhalb des Schwerpunktpro-gramms “Eingebettete Systeme”. In diesem Zusammen-hang ist das Spin-Off-UnternehmenX2E entstanden, dasdie Weiterentwicklung des Emulationssystems übernom-men hat.

Literatur

[1] HERGENHAN, A. und W. ROSENSTIEL: Static TimingAnalysis of Embedded Software on Modern Processor Ar-chitectures. In: Proceedings of the Date 2000 Conference,März 2000.

[2] HERGENHAN, A., A. SIEBENBORNund W. ROSENSTIEL:Studies on Static Timing Analysis Techniques for Modern

Processor Architectures. In: WIP-Proceedings of the 20thIEEE Real-Time Systems Symposium, 1999.

[3] HERGENHAN, A., A. SIEBENBORNund W. ROSENSTIEL:Studies on Different Modeling Aspects for Tight Calculati-ons of Worst Case Execution Time. In: WIP-Proceedings ofthe 21th IEEE Real-Time Systems Symposium, 2000.

[4] HERGENHAN, A., S. HOFMANN, D. SCHRÖDER undW. ROSENSTIEL: Modellierung, Analyse und Bewertungvon Systemarchitekturen intelligenter eingebetteter Syste-me der Automobilindustrie. In: Workshop AES2000, Januar2000.

[5] HERGENHAN, A.: Analytische Modellierung und Bewer-tung von Prozessoren in eingebetteten Systemen. Disserta-tion, Universität Tübingen, 2001.

[6] SIEBENBORN, A., O. BRINGMANN und W. ROSENSTIEL:Worst-Case Performance Analysis of Parallel, Communica-ting Software Processes. In: Proceedings of CODES, 2002.

[7] SIEBENBORN, A., O. BRINGMANN und W. ROSENSTIEL:Communication Analysis for System on Chip Design. In:Proceedings of the Design Automation and Test in EuropeConference (DATE), Paris, Februar 2004.

[8] WEISS, K., T. STECKSTOR, C. NITSCH, U. KEBSCHULL

und W. ROSENSTIEL: Performance Analysis of Rael-TimeOperating Systems by Emulation of an Embedded System.In: RSP’99, Clearwater, Florida, USA, Juni 1999.

[9] WEISS, K., T. STECKSTOR, G. KOCH und W. ROSEN-STIEL: Exploiting FPGA-Features during the Emulation ofa Fast Reactive Embedded System.In: IEEE Symposium onField Programmable Gate Array, Monterey,USA, 1999.

[10] WEISS, K., C. OETKER, I. KATCHAN, T. STECKSTORundW. ROSENSTIEL: Power Estimation Approach for SRAM-based FPGAs. In: IEEE Symposium on Field Programma-ble Gate Array, Monterey USA, 2000.

[11] NITSCH, C., K. WEISS, T. STECKSTOR und W. RO-SENSTIEL: Embedded System Architecture Design Basedon Real-Time Emulation. In: Rapid System PrototypingRSP2000, Paris, France, Juni 2000.

[12] WEISS, K.: Architekturentwurf und Emulation eingebette-ter Systeme. Dissertation, Universität Tübingen, 2000.

[13] WEISS, K., T. STECKSTOR und W. ROSENSTIEL: Ent-wurf und Entwurfsmethodik einer auf SH3-7709A undVxWorks basierten Multimedia-Platform für Automotive-Anwendungen. In: Workshop AES 2000, Karlsruhe, Janu-ar 2000.

[14] WEISS, K., T. STECKSTORund W. ROSENSTIEL: Emula-tion of a Fast Reactive Embedded System using a Real Ti-me Operating System. In: DATE99, München, März 1999.

[15] WEISS, K., A. HERGENHAN und W. ROSENSTIEL: Syste-matischer Entwurf und Test eingebetteter Systeme am Bei-spiel eines ATM-Diagnosesystems. In: Workshop zur Archi-tektur von Rechnersystemen (ARCS), Rostock, 1997.

[16] HERGENHAN, A., C. WEILER, K. WEISSund W. ROSEN-STIEL: Value-Added Services in Industrial Automation. In:Lecture Notes in Computer Science ; Vol. 1385. Springer-Verlag Berlin-Heidelberg, 1998.

[17] HERGENHAN, A., C. WEILER, K. WEISSund W. ROSEN-STIEL: Internet-basierte eingebettete Systeme der industri-ellen Automation. Automatisierungstechnik, 7, 1999.

[18] SCHMITT, S. und W. ROSENSTIEL: Verifikation of a Mi-crocontroller IP Core for System-on-a-Chip Designs UsingLow-Cost Prototyping Environments. In: DATE Confe-rence, Paris, France, Februar 2004.

12

Komponentenbasierte Entwicklung eingebetteter Systeme

Nasser Jazdi Institut für Automatisierungs- und Softwaretechnik (Prof. Dr.-Ing. Dr. h. c. P. Göhner)

Universität Stuttgart

Zusammenfassung Gegenstand des Projekts war die komponentenba-

sierte Softwareentwicklung für eingebettete Systeme. Dabei lag der Schwerpunkt auf der Methodik und der Festschreibung geeigneter Verfahren. Die Werkzeug-unterstützung sowie der Aufbau einer spezifisch auf eingebettete Systeme angepassten Komponentenbiblio-thek waren weitere Ziele dieser Forschungstätigkeit.

1. Einleitung Durch den anhaltenden Preisverfall und die Leistungs-

steigerung der Hardwarekomponenten, insbesondere bei Mikroprozessoren und Speichern, eröffnen sich ständig neue Einsatzmöglichkeiten für eingebettete Systeme. Da zunehmend auch neuartige Funktionen in die eingebet-teten Systeme integriert werden, steigt ihre Komplexität an [1]. Viele komplexe Funktionen werden zunehmend in Software realisiert, um im Bereich der Hardware mög-lichst kostengünstige Standardkomponenten einsetzen zu können. Die Wertschöpfung bei der Neuentwicklung von Produkten verlagert sich damit immer mehr in Richtung Software.

Während man in der Hardware zum überwiegenden Teil bereits auf bestehende Standardkomponenten zu-rückgreifen kann, ist dies in der Software bisher kaum gelungen. Zum einen wird die spezifische Funktionalität der Systeme in Form spezifischer Software realisiert, zum anderen gibt es im Gegensatz zur Hardwareent-wicklung keine allgemein anwendbaren komponenten-basierten Entwicklungsmodelle und -methoden. Die Software wird individuell entwickelt und oft von Hand optimiert, um den Speicherplatz optimal auszunutzen und die Bauteilkosten niedrig zu halten, die sich bei hohen Stückzahlen zu beachtlichen Beträgen summie-ren. Mit dieser Vorgehensweise wird man jedoch der rasch ansteigenden Komplexität der Software schon bald nicht mehr gewachsen sein [2].

2. Zielsetzung Ziel des Forschungsvorhabens war die Entwicklung

neuer Methoden und Verfahren für die komponentenba-sierte Softwareentwicklung für eingebettete Systeme. Dabei waren die speziellen Randbedingungen von ein-

gebetteten Systemen zu berücksichtigen. Die Software-komponenten mussten auf einem hohen Abstraktionsni-veau zur Verfügung gestellt werden, um eine individu-elle Anpassung der Software an die beschränkten Sys-temressourcen, wie Speicherplatz und Rechenleistung, zu ermöglichen. Die Forschungsarbeiten konzentrierten sich dabei auf folgende vier Themenschwerpunkte: • Komponentenbasierte Entwicklungsmethoden für

eingebettete Systeme • Werkzeugunterstützung für einen möglichst stark

automatisierten Entwicklungsablauf beim Einsatz von vorgefertigten Softwarekomponenten

• Erstellung einer Komponentenbibliothek • Entwicklung von Komponenten für die Diagnose

und Wartung eingebetteter Systeme In der Analysephase wurden zunächst die Eigen-

schaften eingebetteter Systeme untersucht und diese in zeit- und ereignisgesteuerte Systeme unterteilt. Darauf aufbauend wurden im Laufe des Projekts drei Ent-wurfsmethoden entwickelt, die auf die besonderen Randbedingungen von eingebetteten Systemen zuge-schnitten sind. Diese Entwurfsmethoden wurden in unterschiedlichen Berichten an die DFG, sowie in zahl-reichen Veröffentlichungen detailliert dargestellt. Sie werden im Folgenden kurz zusammengefasst.

3. Komponentenbasierte Entwicklung ereignisgesteuerter eingebetteter Systeme

Für ereignisgesteuerte eingebettete Systeme wurde ein Java-basiertes Konzept entwickelt, das auf der Java-Komponententechnologie JavaBeans aufsetzt. Der Fo-kus lag dabei auf ereignisgesteuerten, nicht sicherheits-kritischen Systemen. Der Grund für diese Einschrän-kung waren die spezifischen Merkmale der Program-miersprache Java.

Im Rahmen der Untersuchungen wurde festgestellt, dass die von JavaBeans verwendeten Kommunikati-onsmechanismen zwar ein sehr durchdachtes System für die Entwicklung von grafischen Benutzungsoberflächen darstellen, für Software von eingebetteten Systemen jedoch kaum geeignet sind. Aus diesem Grund wurde das JavaBeans-Kommunikationskonzept modifiziert und an die Anforderungen eingebetteter Systeme ange-passt [3].

13

event queue

connection handler

OnEvent Event

connection table

source componentevent

target componentmethod

event queue

connection handler

OnEvent Event

connection table

source componentevent

target componentmethod

Abbildung 1: Modifiziertes JavaBeans-Kommunikationsmodell

Im modifizierten JavaBeans-Kommunikationskonzept werden der Aufbau der Komponenten sowie deren mögliche Ein- und Ausgänge festgeschrieben. Außer-dem gibt es eine Systematik zur Beschreibung der Komponenten, sowie ein Hierarchisierungsschema. Die Ein- und Ausgänge werden in zwei Kategorien einge-teilt, in Signal- und Datenein- bzw. -ausgänge. Beim Aufbau der Komponenten erreicht man durch die Ver-wendung der Interface-Klasse eine Trennung von Schnittstellendefinitionen und Implementierungen, wodurch eine wichtige Grundvoraussetzung der kom-ponentenbasierten Softwareentwicklung erfüllt wird.

Component

3

2A

1 1

3

2 A

signal input

active data input

passive data input

signal output

active data output

passive data output

Component

3

2A

1 1

3

2 A

signal input

active data input

passive data input

signal output

active data output

passive data output

Abbildung 2: Aufbau der modifizierten JavaBeans-Komponenten

Mit diesem modifizierten Kommunikationskonzept

hat man ein Java-basiertes Komponentenmodell, welches auf die Belange eingebetteter Systeme ausge-richtet ist.

4. Komponentenbasierte Entwicklung zeitgesteuerter eingebetteter Systeme

Bei zeitgesteuerten Echtzeitsystemen werden alle Ak-tivitäten zu definierten Zeitpunkten angestoßen. Die Zustandsgrößen des technischen Systems werden zu festgelegten Zeitpunkten erfasst, alle Teilprogramme werden periodisch ausgeführt. Das Zeitverhalten des Systems ist daher deterministisch. Aus diesem Grund werden sicherheitskritische eingebettete Systeme zeitge-steuert realisiert.

In einem ersten Schritt wurden die Eigenschaften die-ser Systeme untersucht. Daraus wurden Anforderungen an die komponentenbasierte Softwareentwicklung ver-teilter eingebetteter Systeme, wie Determinismus, Kor-rektheit, Kompatibilität zwischen Komponenten und Werkzeugunterstützung, abgeleitet. Synchrone, zeitge-steuerte Ausführungsmodelle sind sehr gut geeignet, um diese Anforderungen zu erfüllen. Daher wurden die Realisierung von Software für eingebettete Systeme auf synchroner Basis, sowie zeitgesteuerte Architekturen für verteilte Systeme näher untersucht. Auf Grundlage des synchronen Ansatzes wurde ein Komponentenmodell für synchrone Softwarekomponenten definiert. Dieses besteht aus einem reaktiven Teil und einem Datenverar-beitungsteil. Das Verhalten der Komponente wird durch den reaktiven Teil bestimmt, der die Datenverarbeitung steuert und ein deterministisches Verhalten aufweist [4].

Verarbeitungs-Teil (C)

Datentyp-Definitionen

Datentyp-Definitionen

Datentyp-Definitionen

Datenverarbeitungs-Funktionen

Synchrone Softwarekomponente

Reaktiver Teil (ESTEREL)

Kontroll- undDatenvariablen

signal Input Signal output

Verarbeitungs-Teil (C)

Datentyp-Definitionen

Datentyp-Definitionen

Datentyp-Definitionen