Echtzeitfähige Berechnung der Modellgleichungen von Huber...

Transcript of Echtzeitfähige Berechnung der Modellgleichungen von Huber...

Juni 2009

1

Echtzeitfähige Berechnung der Modellgleichungen von Huber-Braun-Neuronen auf einem Virtex-4-FPGA

Marcel Beuler, Werner Bonath Fachhochschule Gießen-Friedberg, Fachbereich EI

Wiesenstraße 14, D-35390 Gießen, Germany [email protected], [email protected]

Abstract – Das in der Physiologie zum Einsatz kommende Huber-Braun-Neuronenmodell erfordert pro Iterationsschritt die Berechnung von 64 arithmetischen Operationen einschließlich mathe-matischer Funktionen. Da die Schrittweite des Modells auf 100µs festgelegt ist, müssen somit für ein Neuron pro Sekunde 640000 Operationen zur Bestimmung der Modellgleichungen ausgeführt werden. Dieser Rechenaufwand wird durch die Implementierung des synaptischen Prozesses sowie einer Netztopologie noch weiter erhöht, so dass für die Berechnung “größerer“ leitfähigkeitsbasierter neuronaler Netze (> 100 Neuronen) zur Erfüllung der Echtzeitanforderung die Entwicklung einer dedizierten Hardware, d.h. eines applikations-spezifischen Prozessors (ASP), unumgänglich ist. Auf diese Weise kann man sich von dem klassischen Von-Neumann-Konzept lösen und durch massive Parallelisierung und Pipelining eine an die Modellgleichungen des Neurons angepasste Architektur herausarbeiten, die einen drastischen Performancegewinn ermöglicht. Das hier vorge-stellte Architekturkonzept berechnet auf einem Virtex-4-FPGA bei 100MHz alle relevanten Modell-gleichungen für 400 Neuronen in Echtzeit und ist als Grundlage für die ASIC-basierte Entwicklung eines digitalen Neuroprozessor für das gewünschte Modell anzusehen.

I. Einleitung Viele Neuronen innerhalb des zentralen Nervensys-tems zeigen ein elektrisches Verhalten, das durch unterschwellige Membranpotential-Oszillationen und der Generierung von Aktionspotentialen (Spikes), falls die Oszillationen den Schwellwert erreichen, charakterisiert werden kann [2]. Solche Oszillation-en stellen eine Erweiterung des klassischen Hodgkin-Huxley-Modells zum sog. Huber-Braun-Modell dar und sind eine inhärente Eigenschaft des Neurons. Zusätzlich unterliegt jedes biologische System einem Rauschen, welches sich in der zufälligen Schwankung des Membranpotentials äußert. Wenn sich Oszillationen in der Nähe des Schwellwerts bewegen, hat dieser Rauschanteil maßgeblichen Einfluss darauf, ob ein Aktions-potential generiert wird oder nicht.

Im Modell wird der Rauschanteil mittels Box-Mueller-Algorithmus nachgebildet, was die Berechnung der elementaren Funktionen cos, ln und sqrt erfordert. Für die Hodgkin-Huxley-typische

Spike-Generierung muss zusätzlich noch die exp-Funktion bestimmt werden. Bei einer gewählten Schrittweite von 100µs sind alle relevanten Modell-gleichungen 10000 Mal pro Sekunde zu durch-laufen, d.h. das Huber-Braun-Modell ist sehr rechenintensiv. Selbst auf aktuellen Rechnern bei 2,5 bis 3 GHz Taktrate kann man weniger als 100 Neuronen in Echtzeit berechnen. Weiterhin muss berücksichtigt werden, dass ein Neuronenverbund charakterisiert wird durch eine Netztopologie, d.h. die Verbindung der einzelnen Neuronen unter-einander.

Der synaptische Prozess, d.h. die Ausbreitung des postsynaptischen Potentials (PSP) entlang des Dendriten, sowie die Aufintegration der einzelnen PSPs am Soma wird zunächst ersetzt durch einen Injektionsstrom Iinj, der das Membranpotential depolarisieren kann. Für die spätere Signalweiter-leitung innerhalb eines Neuronenverbundes ist die digital-diskrete Nachbildung der Ausbreitung der PSPs zwingend erforderlich, was den Rechenauf-wand weiter ansteigen lässt.

Die hier vorgestellte Architektur wird in VHDL programmiert, auf einem Virtex-4-FPGA syntheti-siert und funktional verifiziert. Dadurch können Änderungen innerhalb des Entwurfsprozesses nicht nur per Simulation, sondern auch auf einer Hardwareplattform überprüft werden.

II. Das Huber-Braun-Neuronenmodell Das Huber-Braun-Modell ist ein leitfähigkeitsbasier-tes Neuronenmodell, welches sich aus zwei Teilen mit jeweils einem Natrium- und einem Kaliumkanal zusammensetzt [1,2]:

• Hodgkin-Huxley-typische Komponente mit einem schnellen, unmittelbar aktiven, depolari-sierenden Natriumkanal (Index d) und einem schnellen repolarisierenden Kaliumkanal (Index r) mit den Leitfähigkeiten gd bzw. gr;

• Komponente für unterschwellige Oszillationen, bestehend aus einem langsamen depolarisie-renden Natriumkanal (Index sd) und einem langsamen repolarisierenden Kaliumkanal (Index sr) mit den Leitfähigkeiten gsd bzw. gsr;

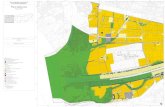

Abb. 1 zeigt das Ersatzschaltbild des Huber-Braun-Neuronenmodells mit den insgesamt fünf Ionen-kanälen, wobei Il den schon vom Hodgkin-Huxley-

2

Modell her bekannten Leckstrom symbolisiert und die übrigen Ströme mit den oben beschriebenen Ionenkanälen korrespondieren. Der synaptische Prozess, d.h. die Reizung der Zelle, wird über eine Stromquelle mit dem Injektionsstrom Iinj nachgebil-det. Für die in Abb. 1 eingezeichnete Richtung bewirkt Iinj > 0 eine Depolarisation der Membran.

dV

dg

rV

rg

dI− rI

iV

eV

lV

lg

lI

mC

CI

srV

srg

srI

sdV

sdg

sdI− injI

(intracellular)

(extracellular)

action potential oscillation

dV

dg

rV

rg

dI− rI

iV

eV

lV

lg

lI

mC

CI

srV

srg

srI

sdV

sdg

sdI− injI

(intracellular)

(extracellular)

action potential oscillation

Abb. 1: ESB des Huber-Braun-Neuronenmodells

Über die Strom-Spannungs-Beziehung der Membrankapazität sowie dem Knotenpunktsatz erhält man Gl. (1). Der Leckstrom und die spannungsabhängigen Ströme werden mittels Gln. (2) und (3) modelliert, wobei gi die max. Leitfähigkeit (Index i steht für d, r, sd, sr), ai die spannungsab-hängige Gating-Variable und Vi das zugehörige Nernst-Potential darstellt.

( ) M l d r sd sr injdV

f V C I I I I I Idt

= ⋅ = − − − − − + (1)

( )l l lI g V V= ⋅ − (2)

( )i i i iI g a V Vρ= ⋅ ⋅ ⋅ − (3)

Analog zu Hodgkin-Huxley wird der Gating-Mecha-nismus, also die Öffnungswahrscheinlichkeit eines Kanals, über eine DGL 1. Ordnung beschrieben:

( )ϕτ∞⋅ −

=i i i

i

da a a

dt (4)

[ ]0

1

1 exp ( )∞ =+ − ⋅ −i

i i

as V V

(5)

Speziell für den unmittelbar aktiven, depolarisieren-den Natriumkanal gilt ad = ad∞. Die temperatur-abhängigen Faktoren ϕ und ρ sind 1.0 bei der Referenztemperatur von 25°C [1]. Die Differential-quotienten werden numerisch über die Euler-Integration mit einer Schrittweite von ∆t = 100µs = 0.1ms gelöst [2]:

1

( )+∆ = + ⋅ ⋅ ∆t t t tM

V V f V tC

(6)

, , , ,( )ϕ τ+∆ ∞= + ⋅∆ ⋅ −i t t i t i i t i ta a t a a (7)

Der dem Membranpotential überlagerte Rausch-anteil als inhärente Eigenschaft biologischer Systeme wird über ein mathematisches Modell beschrieben, dessen Signalamplituden (in mV) eine Gaußverteilung aufweisen. Ausgangspunkt für diesen weißen gaußschen Rauschprozess sind zwei gleichverteilte Zufallszahlen im Intervall [0,1].

Daraus erhält man über die Box-Mueller-Methode nach folgender Transformationsvorschrift eine normalverteilte Zufallszahl [2]:

4 ln( ) cos(2 ) ; [ ] mVπ= − ⋅ ∆ ⋅ ⋅ ⋅ =w wg d t a b g (8)

1

( )+∆ = + ⋅ ⋅∆ +t t t t wM

V V f V t gC

(9)

A Numerische Parameter und Simulation Die numerischen Parameter für das Huber-Braun-Modell werden aus [2] entnommen und die Betriebstemperatur des Neurons auf 25°C festgelegt. Die Konstanten sind in Appendix A zusammengefasst.

Der Rauschparameter noise_D und der Injektions-strom I_inj sind die Größen, die für die Simulation variiert werden können. In Abb. 2 betragen die Startwerte noise_D = 0.1 und I_inj = 1.0. Das oberste Teilbild zeigt das zugehörige Mem-branpotential mit den unterschwelligen Oszillation-en. Der Injektionsstrom ist so gering, dass auch der überlagerte Rauschanteil keine Spike-Generierung zur Folge hat. Im nächsten Teilbild wird I_inj auf 1.2 erhöht, so dass sich die Oszillationen in der Nähe des Schwellwerts bewegen. Im vorletzten Teilbild beträgt I_Inj = 1.4, d.h. die Amplituden der Oszillationen sind größer und die Wahrscheinlichkeit einer Spike-Generierung steigt drastisch an. Das letzte Teilbild zeigt schließlich den Ausgangs-Injek-tionsstrom mit deutlich höherem Rauschanteil, so dass auch hier Aktionspotentiale auftreten.

Abb. 2: Membranpotential in Abhängigkeit von noise_D und I_inj

3

B Analyse der Modellgleichungen In Tab. 1 sind alle notwendigen Operationen zur Berechnung des Membranpotentials eines Neurons in einem Iterationsschritt (Neuronenzyklus) zusam-mengefasst, um den späteren Berechnungsaufwand abschätzen zu können. Die jeweiligen Operationen werden durch den Buchstaben A für das erste Neuron gekennzeichnet, Buchstabe B würde das zweite Neuron kennzeichnen usw. Als Vorgriff auf den Einsatz des CORDIC-Algorithmus sei erwähnt, dass die Umsetzung der mathematischen Funktionen sowie der Divisionen in A13, A22, A35 und A48 über diesen Algorithmus erfolgt. Weiterhin sollten die folgenden Terme zur Reduktion der Rechenzeit in ROMs abgelegt werden:

• -4dּ∆t (abgelegt für d = {0.0,0.1,0.2,…,0.5}) • ∆t/τr , ∆t/τsd und ∆t/τsr • ∆t/CM • 2π

Insgesamt sind pro Neuron ohne synaptischen Prozess in einem Neuronenzyklus 64 Arithmetik-operationen auszuführen, in einer Sekunde entsprechend 640000. Im Einzelnen sind 11 CORDIC-Operationen, 26 kombinierte Additionen / Subtraktionen und 27 Multiplikationen erforderlich.

Abk. Operation Abk. Operation A01 log(a) A33 exp(A32) A02 2π*b A34 A33+1 A03 cos(A02) A35 1/A34 A04 A01*(-4dּ∆t) A36 A35-asd_old A05 sqrt(A04) A37 A36*ϕ A06 A05*A03 A38 A37*(∆t/τsd) A07 V-Vl A39 A38+asd_old A08 gl*A07 → Il A40 V-Vsd A09 V-V0d A41 A40*asd_old A10 A09*(-sd) A42 ρ*gsd A11 exp(A10) A43 A41*A42 → Isd A12 A11+1 A44 V-V0sr A13 1/A12 A45 A44*(-ssr) A14 V-Vd A46 exp(A45) A15 A14*A13 A47 A46+1 A16 ρ*gd A48 1/A47 A17 A16*A15 → Id A49 A48-asr_old A18 V-V0r A50 A49*ϕ A19 A18*(-sr) A51 A50*(∆t/τsr) A20 exp(A19) A52 A51+asr_old A21 A20+1 A53 V-Vsr A22 1/A21 A54 A53*asr_old A23 A22-ar_old A55 ρ*gsr A24 A23*ϕ A56 A54*A55 → Isr A25 A24*(∆t/τr) A57 A30+A08 → Ir+Il A26 A25+ar_old A58 A43+A56 → Isd+Isr A27 V-Vr A59 A57+A58 A28 A27*ar_old A60 A59+A17 A29 ρ*gr A61 A60-Iinj A30 A28*A29 → Ir A62 A61*(∆t/CM) A31 V-V0sd A63 V-A62 A32 A31*(-ssd) A64 A63+A06

Tab. 1: Operationen während eines Neuronenzyklus

Der Rechenaufwand ist also nicht ganz unerheblich und bringt handelsübliche PCs mit Blick auf die Echtzeitanforderung recht schnell an die Grenzen

ihrer Leistungsfähigkeit. Eine Möglichkeit, das Echtzeit-Kriterium zu erfüllen, stellt der Einsatz eines Großrechners dar. Die andere besteht in der Entwicklung einer dedizierten Hardware mit einer möglichst effektiven Implementierung der Modell-gleichungen.

III. Generierung der Pseudo-Zufallszahlen Die beiden zur Ermittlung des Rauschanteils notwendigen gleichverteilten Zufallszahlen im Intervall [0,1] sollen in einer digitalen Architektur über ein rückgekoppeltes Schieberegister (LFSR = Linear Feedback Shift Register) bestimmt werden, da sich hier der Hardwareaufbau sehr einfach gestaltet. Abb. 3 zeigt beispielhaft ein 16-Bit-LFSR.

Abb. 3: 16-Bit-LFSR [3]

In jedem Takt wird das frei werdende Bit am Eingang des Schieberegisters mit dem Ergebnis der EXOR-Verknüpfung der Abzweig-Positionen 11, 13, 14 und 16 gefüllt (Zählung beginnt links mit 1). Bei geeigneter Wahl dieser Abzweigungen wiederholt sich die ursprüngliche Bitkombination erst nach einer max. Periodenlänge von 2n-1, wobei n die Anzahl der Bits des LFSRs ist. Zur Initialisierung kann das Schieberegister mit beliebigen Werten gefüllt werden, nicht jedoch nur mit Nullen.

Der Zustand des Schieberegisters ist nicht als Pseudo-Zufallszahl zu betrachten, sondern lediglich das Eingangsbit [3]. Kennt man das zum aktuellen Zeitpunkt in den Flipflops gespeicherte Bitmuster, so wird dieses Muster im nächsten Takt lediglich um eine Position weiter geschoben. Die Hardware generiert zur Berechnung einer gleichverteilten Zufallszahl 16 Zufallsbits, was bzgl. der Genauigkeit ausreichend ist. Da die Zahl im Intervall [0,1] liegen soll, entspricht das zuletzt ermittelte, höchstwertige Bit dem Stellenwert 2-1 und das zuerst ermittelte, niederwertigste Bit dem Stellenwert 2-16.

Als Länge des LFSRs werden n=32 Bit angesetzt. Um max. Periodizität zu erhalten, können die Abzweig-Positionen der Rückkopplung aus [4] entnommen werden, wobei die dort gewählte EXNOR-Verknüpfung durch EXOR zu ersetzen ist (alle generierten Bits werden invertiert). Das LFSR kann somit nicht den Nullzustand durchlaufen, wohl aber die 16 Zufallsbits. Tritt dieser Zustand ein, dann wird die Wertigkeit der Zufallszahl auf 2-17 gesetzt. Auf diese Weise kann der Fall = −∞ln(0) in Gl. (8) nicht auftreten.

4

Die Rückkopplung eines LFSRs kann allgemein durch ein Polynom P beschrieben werden, wobei die dort auftretende ’1’ die Rückkopplung auf das 1. Bit kennzeichnet (x0) und nicht als Abzweigung gerechnet wird [3]. Mit [4] ergibt sich für n=32:

32 22 2 1 1= + + + +P x x x x (10)

Um Matlab-, C- und VHDL-Ergebnisse miteinander vergleichen zu können, werden die Zufallszahlen generell nach diesem Verfahren bestimmt.

A VHDL-Implementierung Als Vorgriff sei erwähnt, dass in 200 Taktzyklen die blockorientierte Berechnung von 10 Neuronen erfolgt, d.h. es sind 20 Zufallszahlen in diesem zeitlichen Rahmen zu bestimmen. Für jede Zufallszahl werden 16 Bits über ein nach Gl. (10) rückgekoppeltes, 32-Bit-Schieberegister generiert.

016 Bit0 0 0 0 0 0 0016 Bit0 0 0 0 0 0 0

Abb. 4: Zufallszahl als denormalisierte Mantisse

Diese 16 Bits werden linksseitig um eine 0 (hidden bit) und rechtsseitig um 7 Nullen ergänzt, so dass eine um das Hidden-Bit erweiterte, denormalisierte 24-Bit-Mantisse entsteht. Alle zum Einsatz kommen-den Arithmetikeinheiten arbeiten intern mit einem 32-Bit-Gleitkommaformat, d.h. das Format nach Abb. 4 muss vor der Weiterverarbeitung noch in eine normalisierte 32-Bit-Gleitkommazahl umgewan-delt werden. Die Anzahl der führenden Nullen wird über einen 16-Bit Barrel-Shifter ermittelt. Beinhaltet die 24-Bit-Mantisse nur Nullen, dann wird der zugehörige Exponent der Gleitkommazahl auf 0x6E für 2-17 gesetzt. Die Generierung einer Zufallszahl nimmt 20 Taktzyklen in Anspruch, so dass insgesamt drei parallel arbeitende LFSRs vorgesehen sind.

Abb. 5 zeigt den prinzipiellen Aufbau des PRN-Moduls (PRN = Pseudo Random Number) mit den drei 32-Bit-Registern QLFSR_X und den drei 16-Bit-Registern QPseudo_X. Der Inhalt von QPseudo_X wird in Man_X auf 24 Bit erweitert und über einen Multiplexer an den Barrelshifter zur Normalisierung angelegt. Die ermittelten Ergebnisse werden schließlich in einem FIFO abgelegt.

QLFSR_0

feedback

QPseudo_0

QLFSR_1

feedback

QPseudo_1

QLFSR_2

feedback

QPseudo_2

MU

X

16-B

it B

arre

l Shi

fter

32-B

it F

P-N

umbe

r

FIFO_7

Man_0

Man_1

Man_2

031

0

0

0

0

0

31

31

15

15

15

appropriate taps are 1, 2, 22 and 32

QLFSR_0

feedback

QPseudo_0

QLFSR_1

feedback

QPseudo_1

QLFSR_2

feedback

QPseudo_2

MU

X

16-B

it B

arre

l Shi

fter

32-B

it F

P-N

umbe

r

FIFO_7

Man_0

Man_1

Man_2

031

0

0

0

0

0

31

31

15

15

15

appropriate taps are 1, 2, 22 and 32

Abb. 5: Prinzipieller Aufbau des PRN-Moduls (ohne Steuerwerk)

Der FIFO ist zu Beginn mit 20 Zufallszahlen initialisiert, die in den ersten 200 Taktzyklen (1. Block) benötigt werden. In dieser Zeit generiert das PRN-Modul die 20 Zufallszahlen für den nächsten Block usw.

Zu diesem Zweck ist für das PRN-Modul ein eigener Befehlsspeicher vorgesehen, wobei pro Befehl nur eines der drei QLFSRs gestartet werden kann. Jeder dieser Zweige verfügt über einen Zähler für die 16 zu generierenden Bits. Ist ein QLFSR gestartet, dann ist jeder weitere Befehl, der dieses Register betrifft, unwirksam. Der 4-stellige OP-Code ist in Tab. 2 zusammengefasst.

Code Befehl 00xx NOP 0100 QLFSR_0 0101 QLFSR_1 0110 QLFSR_2

Tab. 2: Befehlssatz des PRN-Moduls

In Appendix B sind die Initialwerte der ersten 20 FIFO-Einträge sowie der Register QLFSR_0 bis QLFSR_2 aufgeführt.

IV. Architektur Zu Beginn muss festgelegt werden, ob als Datenformat ein Fest- oder Gleitkommaformat zum Einsatz kommt.

Aufgrund der in [1] aufgeführten numerischen Probleme einer VHDL-AMS-Simulation des Huber-Braun-Modells fällt die Wahl auf das 32-Bit-Gleitkommaformat, um Bereichsüberschreitungen vorzubeugen. Das 32-Bit-Format (float) stellt einen Kompromiss zwischen einer einfacher zu implemen-tierenden Festkommaarithmetik und dem wesentlich genaueren, aber auch aufwändigeren 64-Bit-Gleit-kommaformat (double) dar.

Die geringere Genauigkeit von float hat natürlich zur Folge, dass sich die numerisch bedingten Fehler in den einzelnen Neuronenzyklen schneller aufad-dieren und zu Abweichungen bzgl. der Matlab-Simulation führen, da diese standardmäßig mit double arbeitet. Somit ist nicht damit zu rechnen, dass der Virtex-4-FPGA und Matlab den gleichen Membranpotentialverlauf liefern. Weiterhin sehen bei einer Änderung der Pseudo-Zufallszahlen-sequenz auch die Matlab-Ergebnisse nach Abb. 2 völlig anders aus. Daher ist es von entscheidender Bedeutung, dass trotz der geringeren Genauigkeit der FPGA-Lösung die grundsätzlichen Eigenschaf-ten des Neuronenmodells nicht verloren gehen.

Das Huber-Braun-Modell weist eine Schrittweite von ∆t = 100µs auf. Um Echtzeitfähigkeit zu garantieren, müssen alle für dieses Modell relevanten Berech-nungen nach Tab. 1 in max. 100µs ausgeführt werden. Wir gehen zunächst von 10MHz Taktrate aus, d.h. bei der angegebenen Schrittweite und einer Periodendauer von 100ns stehen pro Neuronenzyklus 1000 Taktzyklen für die Berech-nung der Modellgleichungen zur Verfügung. Da an

5

dieser Stelle die Netztopologie und die zur Depolari-sation der Membran beitragenden postsynaptischen Potentiale (PSPs) noch nicht in den Entwicklungs-prozess einfließen, sollen von diesen 1000 Taktzyklen zunächst max. 800 für die Berechnung der Modellgleichungen möglichst vieler Neuronen verwendet werden.

A Aufbau eines Neuronenkerns In Anlehnung an die Computertechnik wird eine vollständige Einheit zur Berechnung der Modell-gleichungen als Neuronenkern bezeichnet. Ein digitaler Neuroprozessor setzt sich dann aus mehreren (10…40) solcher Kerne zusammen.

Abb. 6 zeigt den prinzipiellen Aufbau eines Neuronenkerns, bestehend aus 6 Arithmetikeinhei-ten (AE) und dem PRN-Modul zur Erzeugung der gleichverteilten Zufallszahlen:

• 2 Addierer/Subtrahierer (9 Taktzyklen, 2 ROMs 1 Dualport-RAM, 1 FIFO)

• 3 Multiplizierer (8 Taktzyklen, 2 ROMs, 1 FIFO) • 1 CORDIC (42 Taktzyklen, 1 ROM, 1 FIFO) • 1 PRN-Modul (20 Taktzyklen, drei parallele

LFSRs, 1 FIFO)

Jede Arithmetikeinheit verfügt über einen eigenen Befehlsspeicher, einen FIFO zum Ablegen des berechneten Ergebnisses und eigene ROMs bzw. RAMs für den Zugriff auf Konstanten bzw. Variablen gemäß den Modellgleichungen. Hier ist bewusst etwas Redundanz eingebaut, beispielsweise benötigen die AEs keinen zweiten ROM.

Cod

eC

ode

Cod

eC

ode

Cod

e

RA

MR

AM

RO

M

FIFO_1ADD_SUB_MODULE_A

RO

M

ADD_SUB_MODULE_B

RO

M

MULT_MODULE_A

RO

M

MULT_MODULE_B

RO

M

CORDIC_MODULE

RO

MR

OM

RO

MR

OM

FIFO_2

FIFO_3

FIFO_4

FIFO_6

FIFO_8

Cod

e

RO

M

MULT_MODULE_C

RO

M

FIFO_5

PRN_MODULE

Cod

e

FIFO_7

Cod

eC

ode

Cod

eC

ode

Cod

e

RA

MR

AM

RO

M

FIFO_1ADD_SUB_MODULE_A

RO

M

ADD_SUB_MODULE_B

RO

M

MULT_MODULE_A

RO

M

MULT_MODULE_B

RO

M

CORDIC_MODULE

RO

MR

OM

RO

MR

OM

FIFO_2

FIFO_3

FIFO_4

FIFO_6

FIFO_8

Cod

e

RO

M

MULT_MODULE_C

RO

M

FIFO_5

PRN_MODULE

Cod

e

FIFO_7

Abb. 6: Architektur eines Neuronenkerns

Im Befehlscode werden neben der eigentlichen Operation die Adressen der beiden Operanden angegeben. Hierbei kann es sich um die eigenen ROMs, den eigenen Dualport-RAM (falls vorhanden) oder einen der Ergebnisspeicher FIFO_1 bis FIFO_6 handeln (der Zugriff auf FIFO_7 und FIFO_8 erfolgt etwas anders und soll später erläu-tert werden). Wichtig ist, dass grundsätzlich jede AE auf alle Ergebnisspeicher über ein globales Bus-System mit zunächst 6 32 192⋅ = Busleitungen zugreifen kann. Da jede AE ihr Ergebnis auf dem eigenen FIFO ablegt, kann hier die Adressangabe entfallen. Eine Analyse der Datenabhängigkeit der Modellgleichungen zeigt, dass gelegentlich der Zugriff auf 2 FIFO-Einträge desselben Speichers in einem Taktzyklus notwendig ist. Daher verfügen alle auf dem Virtex-4-FPGA synthetisierten Ergebnis-speicher über einen Schreib- und zwei Leseports, mit der Konsequenz, dass sich die Anzahl der globalen Busleitungen verdoppelt auf jetzt insgesamt 384.

Um die mathematischen Funktionen ln, sqrt, exp und cos in einer einheitlichen Architektur realisieren zu können, kommt der CORDIC-Algorithmus zur Anwendung. Eine umfassende Beschreibung der mathematischen Grundlagen dieses Hardware-Algorithmus ist beispielsweise in [6,7] zu finden. In [6] ist auch der vollständige VHDL-Quellcode der bitparallelen iterativen CORDIC-Struktur in einer 32-Bit-Gleitkommaumgebung angegeben und per Simulation verifiziert. Damit ein Neuronenkern einen möglichst hohen Durchsatz erzielen kann, ist eine Fließbandarchitektur für jede AE unumgänglich.

Im Gegensatz zur klassischen Von-Neumann-Architektur ist bei einem Fließband-Konzept kein Steuerwerk vorhanden. Die einzelnen Befehle einer AE benötigen für einen Fließbanddurchlauf genauso viele Taktschritte wie sie ohne Fließbandtechnik, d.h. mikroprogrammiert, benötigen würden. Die Mikroprogrammteile der Befehle erscheinen sozusagen aufgerollt auf dem Fließband, die Zustandsfolgen dieser Teile finden sich praktisch in den Stufenfolgen der einzelnen Fließbandregister wieder [8].

Die bei der Bestimmung der ai∝-Werte auftretenden Divisionen haben alle die gleiche Struktur nach Gl. (5). Die Exponentialfunktion kann nicht negativ werden, somit beträgt der Quotient max. 1. Daher lässt sich nach [6] auch hier der CORDIC-Algorithmus anwenden, was zwei Vorteile hat:

• Für die Implementierung der Modellgleichungen ist kein Dividierer notwendig;

• Bessere Ausnutzung der CORDIC-Pipeline.

Zunächst wird die exp-Funktion berechnet, anschlie-ßend erfolgt nach der Addition von 1 die Division. Das zweimalige Durchlaufen der CORDIC-Pipeline stellt kein Problem dar, weil dies zur Bestimmung des Rauschanteils ohnehin notwendig ist, da in Gl. (8) der Logarithmus unter der Wurzel steht.

6

B Blockweise Berechnung der Neuronen Nach Abb. 6 ist für jede AE ein eigener OP-Code vorgesehen, der jeweils von einem eigenen Programmzähler adressiert wird, vgl. Abb. 7. Diese Architektur hat Vor- und Nachteile.

Vorteile:

• Alle AEs arbeiten parallel, so dass bei entspre-chender Programmierung eine hohe Auslastung der Hardware erreichbar ist.

• Durch Austausch der OP-Codes können Modell-gleichungen geändert bzw. in gewissem Umfang neue Modelle implementiert werden (keine starre Datenflussarchitektur).

Nachteile:

• Aufgrund der parallelen Berechnung der Modell-gleichungen mehrerer Neuronen ist ein einzel-nes Neuron nicht lokalisierbar, daher ist eine Fehlersuche während des Entwicklungspro-zesses schwieriger.

• Für die Berechnung möglichst vieler Neuronen innerhalb eines Neuronenzyklus (zunächst 800 von 1000 Taktschritten vorgesehen) ist die Programmierung durch Maschinenbefehle ent-sprechend unübersichtlich.

Um mit Blick auf den letzten Punkt die Komplexität der Programmierung in Grenzen zu halten, werden die zur Verfügung stehenden 800 Taktzyklen in 4 Blöcke mit jeweils 200 Taktzyklen aufgeteilt. Für jede AE müssen 200 Maschinenbefehle angegeben werden, insgesamt also 6 200 1200⋅ = Befehle. Jeder der 6 Befehlsspeicher wird dann pro Neuronen-zyklus viermal durchlaufen (bei 10MHz), wodurch es notwendig ist, auf Variablen über einen Offset zugreifen zu können. Hierzu werden Index-Adressregister eingeführt, die innerhalb des struk-turellen VHDL-Entwurfs zentral über das Top-Level-Modul beeinflusst werden, siehe Abb. 7.

Im RAM von ADD_SUB_MODULE_A werden die Membranpotentiale V nach Gl. (6) und im RAM von ADD_SUB_MODULE_B die a_i_new-Werte nach Gl. (7) für alle Neuronen eines Kerns gespeichert, d.h. in jedem Block müssen die beiden zugehörigen Index-Adressregister angepasst werden. Die Adressierung der RAMs ist generell nur register-indirekt möglich. Pro Neuron sind ein V- und drei a_i_new-Werte abzulegen, so dass der RAM in MODULE_A die Organisation 512*32-Bit und in MODULE_B 2048*32-Bit aufweist. Damit ließen sich bzgl. des zur Verfügung stehenden Speichers die Modellgleichungen von max. 512 Neuronen pro Kern berechnen. Die restlichen 512 Speicherzellen des RAMs in MODULE_B blieben ungenutzt.

Weiterhin sind die temperaturabhängigen Faktoren ρ und ϕ (siehe [1,2]) als Konstanten in den ROMs der MULT-Module für den Temperaturbereich 23° bis 27°C in 0,5°-Schritten abgelegt. Im ersten Systementwurf soll jedes Neuron die gleiche

Temperatur aufweisen, die Faktoren ρ und ϕ sind daher innerhalb eines Neuronenzyklus konstant.

INDEX_ADDR_ADD_SUB_A_RAM

Top-Level-Module PCs Neuron Core

INDEX_ADDR_ADD_SUB_A_ROM

INDEX_ADDR_MULT_B_ROM

INDEX_ADDR_MULT_A_ROM

INDEX_ADDR_ADD_SUB_B_RAM

INDEX_ADDR_ADD_SUB_B_ROM

INDEX_ADDR_MULT_C_ROM

INDEX_ADDR_ADD_SUB_A_RAM

Top-Level-Module PCs Neuron Core

INDEX_ADDR_ADD_SUB_A_ROM

INDEX_ADDR_MULT_B_ROM

INDEX_ADDR_MULT_A_ROM

INDEX_ADDR_ADD_SUB_B_RAM

INDEX_ADDR_ADD_SUB_B_ROM

INDEX_ADDR_MULT_C_ROM

Abb. 7: Index-Adressregister

Für die ROMs der ADD/SUB- und MULT-Module ist neben der direkten auch die registerindirekte Adressierung implementiert, wobei hier der Index für beide ROMs jeweils identisch ist. Im CORDIC-Modul hingegen ist nur die direkte Adressierung möglich.

C Befehlsformat und Befehlssatz Das für alle AEs identische 28-Bit-Befehlsformat nach Abb. 8 setzt sich zusammen aus 4 Bit für die Codierung des Maschinenbefehls und jeweils 12 Bit für die beiden Operanden OPA und OPB. Jede Operandenangabe wiederum teilt sich auf in 4 Bit für den Speichertyp und 8 Bit für die Adressbildung (letztere wird intern auf 11 Bit erweitert). Da jedes berechnete Ergebnis auf dem eigenen FIFO abge-legt wird, kann hier die Adressangabe entfallen.

827 07111219202324

Code Memory type Address Memory type Address

Operand A Operand B

827 07111219202324

Code Memory type Address Memory type Address

Operand A Operand B Abb. 8: 28-Bit-Befehlsformat für alle AEs

Bei den Speichern wird zwischen dem eigenen ROM, dem eigenen RAM (falls vorhanden) und den Ergebnis-Speichern FIFO_1 bis FIFO_6 (F1 – F6) unterschieden. Hinzu kommen noch FIFO_8 für den nur über MULT_MODULE_A möglichen Zugriff auf RAM-Inhalte von ADD_SUB_MODULE_B und FIFO_7 für den Zugriff des CORDIC-Moduls bzw. der MULT-Module auf die generierten, gleichverteil-ten Zufallszahlen. Die 4-Bit-Speichertypcodierung ist in Tab. 3 zusammengefasst.

Codierung Sp-typ Adress. Modul 0000 ROM direkt alle AEs 0001 FIFO_1 - alle AEs 0010 FIFO_2 - alle AEs 0011 FIFO_3 - alle AEs 0100 FIFO_4 - alle AEs 0101 FIFO_5 - alle AEs 0110 FIFO_6 - alle AEs 0111 FIFO_7 - MULT; CORDIC 1000 FIFO_8 - MULT_A 1110 ROM reg-indirekt MULT; ADD_SUB 1111 RAM reg-indirekt ADD_SUB

Tab. 3: Speichertyp-Codierung

7

Ein Maschinenbefehl wird in mnemonischer Schreibweise wie folgt dargestellt:

<Operation>{_<Operand A>}{,<Operand B>}

Bei der direkten Adressierung eines RAMs wird die Adresse in rechteckige Klammern gesetzt, bei direkter ROM-Adressierung entfällt die Klammer. Handelt es sich um eine registerindirekte ROM-Adressierung, so wird dies durch runde Klammern kenntlich gemacht. Tab. 4 zeigt alle Maschinenbe-fehle einschließlich Codierung, möglicher Operan-den und ihrer Modul-Implementierung.

Befehl Code OPA OPB Modul NOP 0000 - - alle AEs ADD 0001 ROM; RAM;

F1-F6 ROM; RAM;

F1-F6 ADD_SUB

SUB 0010 ROM; RAM; F1-F6

ROM; RAM; F1-F6

ADD_SUB

ADDS 0101 ROM; RAM; F1-F6

ROM;F1-F6 ADD_SUB

SUBS 0110 ROM; RAM; F1-F6

ROM;F1-F6 ADD_SUB

SAV 0011 F1-F6 RAM ADD_SUB SEND 1111 ROM; RAM;

F1-F6 - ADD_SUB_A

MULT 0100 ROM;F1-F7 ROM;F1-F7 MULT COS 0001 ROM;F1-F7 - CORDIC EXP 0011 ROM;F1-F7 - CORDIC LN 0100 ROM;F1-F7 - CORDIC

SQRT 0101 ROM;F1-F7 - CORDIC DIVC 0110 ROM;F1-F7 ROM;F1-F7 CORDIC

Tab. 4: Befehlssatz eines Neuronenkerns

NOP (No Operation) ist ein Wait-Befehl für einen Takt und legt kein Ergebnis auf dem zugehörigen FIFO ab. Der Befehl ist in jeder AE implementiert. Die ADD/SUB-Befehle führen in 8 Taktzyklen eine Gleitkommaaddition bzw. –subtraktion aus (ein-schließlich Laden der Operanden) und legen das Ergebnis im 9. Takt auf dem zugehörigen FIFO F1 oder F2 ab.

Auch ADDS/SUBS führen in 8 Taktzyklen eine Gleit-kommaaddition bzw. –subtraktion aus. Im 9. Takt wird das Ergebnis jedoch nicht auf dem FIFO abgelegt, sondern im zugehörigen RAM gespei-chert. Hierbei muss man beachten, dass die Adresse von OPB auch gleichzeitig die Ergebnis-adresse des RAMs darstellt (registerindirekt adressiert), auch wenn als Speichertyp beispiels-weise ein FIFO ausgewählt ist. Durch diese Ein-schränkung kann im Befehlsformat auf die explizite Angabe einer Ergebnisadresse verzichtet werden.

Der SAV-Befehl legt ein FIFO-Ergebnis F1 bis F6 auf dem zugehörigen RAM ab, der SEND-Befehl in ADD_SUB_A ist zur Übertragung der berechneten Membranpotentiale an einen Host-Rechner vorge-sehen. Als Schnittstelle kommt hier zunächst RS232 zum Einsatz, da diese sehr leicht in VHDL programmierbar ist. Um das Echtzeitkriterium auch bzgl. der Datenübertragung sicherzustellen, soll im nächsten Schritt USB 2.0 (mit Ausblick auf USB 3.0) implementiert werden. Die übrigen Befehle sind selbsterklärend, wobei der Quotient der CORDIC-

Division (DIVC) nach [6] max. 2 betragen darf, da dies der Grenzwert der aufakkumulierten Teilwinkel in der Betriebsart Vectoring im linearen Modus darstellt. Ist der Quotient größer, sind die berech-neten Ergebnisse fehlerhaft! Dieser Fall kann allerdings nach Gl. (5) für das Huber-Braun-Modell nicht auftreten.

D FIFO-Konzept Jede AE legt ihr berechnetes Ergebnis auf einem Pufferspeicher der Organisation 64*32-Bit ab. Hierbei handelt es sich um Speicher mit sequen-tiellem Zugriffsalgorithmus „first in first out“, kurz FIFO. Aufgrund der Datenabhängigkeit bei einigen Operationen ist der gleichzeitige Lesezugriff auf 2 FIFO-Einträge erforderlich. Beispielsweise werden die Operationen A43 und A56 hintereinander auf dem gleichen MULT-Modul berechnet (vgl. Appendix C), was wiederum zwei gleichzeitige Lesezugriffe der Operation A58 zur Ermittlung von Isd + Isr nach Tab. 1 bedingt. Ein FIFO setzt sich daher aus einem Schreib- und zwei Leseports zusammen.

Weiterhin verfügt jeder FIFO über einen Schreib- und Lesepointer zur Adressierung und ist als Umlaufspeicher ausgeführt. Somit werden beim Überlauf des Schreibpointers wieder die Spei-cherzellen mit den Anfangsadressen beschrieben, d.h. die Ergebnisse an diesen Positionen müssen zuvor gelesen (weiterverarbeitet) worden sein.

Im VHDL-Entwurf kommen pro Ergebnisspeicher 2 Dualport-RAMs mit jeweils einem Schreib- und Leseport zum Einsatz. Nachfolgend ist der Quell-code eines 64*32-Bit-Dualport-RAMs sowie stell-vertretend für alle AEs die zugehörige Kompo-nenten-Instanziierung für das ADD_SUB_A-Modul angegeben. Die Synchronität der Leseoperation ergibt sich aus der Abspeicherung der Leseadresse für den Port B im internen Adressregister QADDRB[5:0] mit der steigenden Flanke des CLK-Signals in der Prozessanweisung portB [9]. entity DPR_FIFO is port (CLK,WEA: in std_logic; ADDRA,ADDRB: in std_logic_vector(5 downto 0); DIA: in std_logic_vector(31 downto 0); DOB: out std_logic_vector(31 downto 0) ); end DPR_FIFO; architecture Behavioral of DPR_FIFO is type MMX64_32 is array(63 downto 0) of std_logic_ve ctor(31 downto 0); signal QRAM64_32: MMX64_32 := (others => (others => '0')); signal QADDRB: std_logic_vector(5 downto 0); --inte rnal Address- --Regi ster begin portA: process(CLK) begin if rising_edge(CLK) then if WEA = '1' then QRAM64_32(conv_integer(ADDRA)) <= DIA; end if; end if; end process; portB: process(CLK) begin if rising_edge(CLK) then QADDRB <= ADDRB; end if; end process; DOB <= QRAM64_32(conv_integer(QADDRB)); end Behavioral;

8

-- ADD_SUB_MODULE_A -- Component-Instantiation FIFO_1A: DPR_FIFO port map (CLK=>CLK,WEA=>ADD_SUB_A_BUSY(0), ADDRA=>FIFO_1_W_POINTER,ADDRB=>FIFO_1_R_P OINTER, DIA=>L8_QS,DOB=>QBUS_FIFO_1A ); FIFO_1B: DPR_FIFO port map (CLK=>CLK,WEA=>ADD_SUB_A_BUSY(0), ADDRA=>FIFO_1_W_POINTER,ADDRB=>FIFO_1_R_P OINTER_plus1, DIA=>L8_QS,DOB=>QBUS_FIFO_1B );

Die Schreibpointer sind jeweils identisch, d.h. beide RAMs weisen den gleichen Dateninhalt auf. Der Wert des Lesepointers von FIFO_1B ist stets um 1 höher als der von FIFO_1A. Auf diese Weise ist der gleichzeitige Lesezugriff auf zwei Speicherzellen möglich (nur für FIFO_1 bis FIFO_6 implementiert). In einem solchen Fall müssen natürlich beide Lesepointer um 2 inkrementiert werden.

Für den Schreib- und Lesezugriff ist jeweils eine eigene Prozessanweisung vorgesehen. Der Vektor ADD_SUB_A_BUSY[7:0] speichert die aktuelle Auslastung der Pipeline. Hierbei handelt es sich um ein Schieberegister, dessen höchstwertiges Bit beim Start einer Arithmetikoperation auf 1 gesetzt und dann in jedem Takt um eine Stelle nach rechts geshiftet wird. Ist das niederwertigste Bit eine 1, dann ist die Berechnung abgeschlossen und das Ergebnis wird im nächsten Takt auf dem FIFO abgelegt. ADD_SUB_A_BUSY(0) dient hierbei als Write-Enable-Signal, siehe Komponenten-Instanzi-ierung. Zusätzlich wird der Schreibpointer um 1 inkrementiert.

Der Lesezugriff einer beliebigen AE auf einen FIFO wird über den Vektor GLOBAL_FIFO_READ[7:0] gesteuert. Bit 0 entspricht FIFO_1 und Bit 5 entsprechend FIFO_6. Bei einem zweifachen Lese-zugriff ist zusätzlich das korrespondierende Bit im Vektor GLOBAL_FIFO_READ_DOUBLE[5:0] ge-setzt. -- ADD_SUB_MODULE_A FIFO_1_WR: process(CLK) begin if rising_edge(CLK) then if (ADD_SUB_A_BUSY(0) = '1') then FIFO_1_W_POINTER <= FIFO_1_W_POINTER + 1; end if; end if; end process; FIFO_1_RD: process(CLK) begin if rising_edge(CLK) then if ((GLOBAL_FIFO_READ(0) = '1') and GLOBAL_FIFO_READ_DOUBLE(0 ) = '0') then FIFO_1_R_POINTER <= FIFO_1_R_POINTER + 1; FIFO_1_R_POINTER_plus1 <= FIFO_1_R_POINTER_ plus1 + 1; elsif ((GLOBAL_FIFO_READ(0) = '1') and GLOBAL_FIFO_READ_DOUBLE(0 ) = '1') then FIFO_1_R_POINTER <= FIFO_1_R_POINTER + 2; FIFO_1_R_POINTER_plus1 <= FIFO_1_R_POINTER_ plus1 + 2; end if; end if; end process;

Die o. g. globalen Vektoren werden im Top-Level-Modul durch die lokalen FIFO-Read-Signale aller AEs bestimmt. Für GLOBAL_FIFO_READ(0) gilt beispielsweise: GLOBAL_FIFO_READ(0) <= ADD_SUB_A_FIFO_READ(0) or ADD_SUB_B_FIFO_READ(0) or MULT_A_FIFO_READ(0) or MULT_B_FIFO_READ(0) or MULT_C_FIFO_READ(0) or CORDIC_FIFO_READ(0);

Die lokalen FIFO-Read-Signale wiederum werden aus den beiden Speichertyp-Angaben im Befehl gebildet. Steht z.B. in einem Befehl des Moduls ADD_SUB_A als OPA- oder OPB-Speichertyp “0011“, dann werden ADD_SUB_A_FIFO_READ(2) und damit auch GLOBAL_FIFO_READ(2) auf 1 gesetzt. Sind hingegen beide OP-Speichertypen “0011“, dann wird zusätzlich noch das Bit ADD_SUB_A_FIFO_READ_DOUBLE(2) und somit auch GLOBAL_FIFO_READ_DOUBLE(2) für zwei-fachen Lesezugriff gesetzt. Greifen pro Taktzyklus mehrere AEs auf den gleichen FIFO zu, dann wird jeder Einheit der gleiche Speicherinhalt als Operand zur Verfügung gestellt.

Für FIFO_7 und FIFO_8 ist kein zweifacher Lese-zugriff implementiert, weil die Abbildung der Modell-gleichungen auf die hier vorgestellte Architektur dies nicht erfordert. Zur weiteren Reduzierung des Hardwareaufwands können die in FIFO_7 abgeleg-ten Pseudo-Zufallszahlen des PRN-Moduls nur von den drei Multiplizierern und dem CORDIC geladen werden.

Nach Tab. 1 erfordern die MULT-Operationen A28, A41 und A54 als Operand einen der drei ai_old-Werte der vorherigen Iteration (ar_old, asd_old, asr_old). Diese wiederum sind im RAM des ADD_SUB_B-Moduls abgelegt. Da die Multiplizierer auf diesen Dualport-RAM keinen Zugriff haben, ist als zusätzlicher Puffer zur Aufnahme der ai_old-Werte bei jeder Speicher-operation FIFO_8 vorgesehen. Gemäß Abb. 6 hat nur das MULT_A-Modul Zugriff auf diesen FIFO, d.h. die MULT-Operationen A28, A41 und A54 lassen sich nur von diesem Modul ausführen.

V. Aufbau der AEs Wie bereits erwähnt, weist jede AE zur Erhöhung des Durchsatzes eine Pipeline-Struktur auf. Neben der eigentlichen Arithmetikoperation müssen zusätz-lich noch 1 bis 2 Operanden geladen und das Ergebnis auf dem FIFO abgelegt werden. Die Auslastung jeder Pipeline wird pro Takt in einem als Schieberegister ausgeführten BUSY-Signal ge-speichert. Hierüber wird am Ende einer Arithmetik-operation die Übernahme des Ergebnisses auf den FIFO gesteuert, siehe letzten Abschnitt. Die Länge dieses Signalvektors entspricht immer der um 1 reduzierten Anzahl an Pipelinestufen einer AE.

A ADD_SUB-Modul Ein ADD_SUB-Modul ist ein kombinierter Addierer/Subtrahierer für das 32-Bit-Gleitkomma-format, ausgeführt als 9-stufige Pipeline:

1. Zyklus: Befehl holen 2./3. Zyklus: OPA und OPB laden 4.-8. Zyklus: Befehl ausführen 9. Zyklus: Ergebnis auf FIFO ablegen

Die um das Hidden-Bit erweiterte Mantisse jedes Operanden wird noch um drei Zusatzbits (Guard-Bit g, Round-Bit r und Sticky-Bit s) zur Rundung auf

9

jetzt insgesamt 27 Bits ergänzt. Hierbei entsprechen g und r den beiden Stellen hinter der Stelle, auf die gerundet werden soll und das Sticky-Bit stellt eine ODER-Verknüpfung aller Stellen hinter dem Round-Bit dar [11]. Zur Anpassung des kleineren Exponenten an den größeren wird ein Barrelshifter eingesetzt. Dieser schiebt die Mantisse, die zum kleineren Exponenten gehört, um so viele Stellen nach rechts wie die Differenz der Exponenten beträgt [10]. Das Sticky-Bit als niederwertigste Stelle wird durch die ODER-Verknüpfung gesondert bestimmt.

Die Vorzeichenbits der beiden Operanden werden separat gespeichert. Liegt ein SUB- bzw. SUBS-Befehl vor, dann wird das Vorzeichen von OPB invertiert. Sollte ein Operand negativ sein, erfolgt vor der eigentlichen Mantissen-Addition noch dessen Komplementbildung. Ein möglicher Übertrag bei der Addition wird in einem weiteren Bit aufgefangen. Abb. 9 zeigt die expandierte 28-Bit Mantissen-Darstellung.

23-Bit-Mantissa

2 027 25 13

g r s

26

p0 r‘ s‘

23-Bit-Mantissa

2 027 25 13

g r s

26

p0 r‘ s‘ Abb. 9: Expandierte Mantissen-Darstellung

Nach der Mantissen-Addition werden wieder beide Vorzeichenbits analysiert. Sind sie identisch (positiv oder negativ), dann wird bei einem evtl. aufgetre-tenen Mantissenübertrag eine Korrektur durchge-führt. Eine solche Korrektur beinhaltet nach [10] eine zusätzliche Rechtsverschiebung der Ergebnis-Mantisse um eine Bitstelle und die Erhöhung des Ergebnis-Exponenten um den Wert 1. Sind die Vorzeichenbits ungleich und tritt kein Mantissen-übertrag auf, dann ist das Ergebnis nach [10] negativ, und es muss eine Komplementbildung erfolgen. Tritt hingegen ein Übertrag bei ungleichen Vorzeichen auf, ist das Ergebnis positiv (der Übertrag bleibt in diesem Fall für die weitere Berechnung unberücksichtigt).

Durch die vorzeichenbehaftete Addition kann die Ergebnis-Mantisse führende Nullen aufweisen. Damit das Hidden-Bit in Abb. 9 wieder an Position 26 steht, ist ein Linksshift um NLZ Stellen notwendig (NLZ = Number of Leading Zeros). Im Rundungs-modus “Round to Even“ wird genau dann eine 1 hinzuaddiert, wenn folgende Bedingung erfüllt ist:

0 01 ' ( ' ) ' ' '= ⋅ + = ⋅ + ⋅r s p r s r p (11)

Nach Abb. 9 ist p0 die letzte Stelle, die stehen bleibt. Die Bitstellen p0, r’ und s’ werden nach Tab. 5 in Abhängigkeit von NLZ über das Guard-, Round- und Sticky-Bit generiert. Innerhalb des strukturellen VHDL-Entwurfs sind diese Operationen im Modul LINKSSHIFT_ADD_SUB implementiert.

NLZ 0 1 2 3 Linksshift r’=g

s’=(r+s) p0=g r’=r s’=s

p0=r r’=s s’=0

p0=s r’=0 s’=0

Tab. 5: Operationen in Abhängigkeit von NLZ

B MULT-Modul Ein MULT-Modul führt eine 32-Bit-Gleitkomma-multiplikation in einer 8-stufigen Pipeline aus:

1. Zyklus: Befehl holen 2./3. Zyklus: OPA und OPB laden 4.-7. Zyklus: Befehl ausführen

8. Zyklus: Ergebnis auf FIFO ablegen

Der in [10] angegebene serielle Gleitkommamultipli-zierer ist mit 24 Verarbeitungstakten zu langsam und scheidet daher für eine Hardware-Umsetzung aus. Allerdings verfügt der zum Einsatz kommende XC4VLX60-FPGA der Virtex-4-Serie nach [12] über 64 18×18 Multiplizierer auf dem Chip. Deren Kaska-dierung zu 24×24-Bit Multiplizierer führt jedoch zu höheren Verzögerungszeiten und damit niedrigerer maximaler Taktrate.

Mit Blick auf die Pipeline-Stufen ist es günstiger, die 24×24-Bit Multiplikation der beiden um das Hidden-Bit erweiterten 24-Bit-Mantissen in Teilmultiplika-tionen zu gliedern. Abb. 10 zeigt die Aufteilung in vier Teilmultiplikationen zu je 12×12 Bit.

Aus diesen 24-Bit-Teilprodukten bildet man nun zwei 36-Bit-Teilsummen SUM_L und SUM_H, wobei die von 24 auf 36 Bit zu ergänzenden Stellen der Teilprodukte links- bzw. rechtsseitig mit Nullen aufgefüllt werden. Schließlich wird aus den beiden 36-Bit-Teilsummen durch stellenverschobene Addition das 48-stellige Produkt AB×CD gebildet.

A ×B C D

ManA ManB

×B D = B×D

×A D = A×D

×B C = B×C

×A C = A×C

0 0

0

0

0

0

0

0

0

0

0

0

11

11

11

11

11

11

11

11

23

23

23

23

0……………00

0……………0

2335

B×DA×D

∑ SUM_L

0……………00

0……………0

2335

B×CA×C

∑ SUM_H

0……………03547

SUM_LSUM_H 0……………0

∑ SUM = AB×CD

11

11

11

23 0 023

A ×B C D

ManA ManB

×B D = B×D

×A D = A×D

×B C = B×C

×A C = A×C

0 0

0

0

0

0

0

0

0

0

0

0

11

11

11

11

11

11

11

11

23

23

23

23

0……………00

0……………0

2335

B×DA×D

∑ SUM_L

0……………00

0……………0

2335

B×CA×C

∑ SUM_H

0……………03547

SUM_LSUM_H 0……………0

∑ SUM = AB×CD

11

11

11

23 0 023

Abb. 10: Umsetzung der Multiplikation durch Teil-produktbildung mit anschließender Addition

Das Hidden-Bit der in SUM[47:0] stehenden 48-Bit-Produktmantisse ist auf Position 46 zu finden. Nach [10] liegt dieses Produkt mit der Stellenzahl r = 23 in den Grenzen 1 4≤ <mp , d.h. das Produkt ist nicht

10

notwendigerweise normalisiert. Für SUM(47) = 0 liegt eine normalisierte Mantisse vor. Da zur wei-teren Verarbeitung das Hidden-Bit an der höchst-wertigen Position stehen soll, erfolgt ein Linksshift um eine Stelle. Ist hingegen SUM(47) = 1, dann liegt eine denormalisierte Mantisse vor und der Ergebnis-Exponent wird um 1 inkrementiert. In diesem Fall steht das Hidden-Bit bereits an der höchstwertigen Position, so dass keine Shiftoperation notwendig ist.

SUM[47:24]

SUM[23:0]

24

0

47

23

'r

's

0p1 SUM[47:24]

SUM[23:0]

24

0

47

23

'r

's

0p1

Abb. 11: Normalisierte 48-Bit-Produktmantisse

Abb. 11 zeigt die Verhältnisse für eine in SUM[47:0] stehende, normalisierte Mantisse. Die Rundung des Ergebnisses kann nun wieder mittels Gl. (11) erfol-gen. Hierbei stellt s’ die ODER-Verknüpfung von SUM[22:0] dar.

C CORDIC-Modul Im CORDIC-Modul sind ausschließlich die gemäß den Modellgleichungen erforderlichen mathemati-schen Funktionen ln, sqrt, exp und cos sowie die Division im linearen Modus (Betriebsart Vectoring) implementiert. Das in [6,7] angegebene Blockdia-gramm der Hardware-Umsetzung mit der Aufteilung in eine Vorstufe, den eigentlichen CORDIC-Iterationen und eine die Skalierung einschließenden Endstufe wird grundsätzlich beibehalten, allerdings jetzt in einer bitparallelen CORDIC-Struktur mit 28 Iterationen, siehe Abb. 12. Die in [6] verwendeten Barrelshifter für die Schiebeoperationen im X- und Y-Zweig können nun durch eine fest verdrahtete Logik ersetzt werden. In jeder Iterationsstufe ist neben dem zirkularen auch der hyperbolische Modus mit einer geänderten Shiftfolge zu berück-sichtigen.

Instructions / Data

Preliminary Stage

X_INT[31:0] Y_INT[31:0] Z_INT[31:0]

CORDIC-Pipelinewith 28 Stages

QX_INT[31:0] QY_INT[31:0] QZ_INT[31:0]

Final Stage including scale operations

ES_L7_CORDIC[31:0]

± ±

hard-wired shift

Register Register

ControlUnit

,i im σRegister

X_INTi Y_INTi Instructioni ; mi ; σi

±

Register

αm,i Z_INTi

X_INTi+1 Y_INTi+1 Instructioni+1 ; σi+1 Z_INTi+1

floating-point

fixed-point

fixed-point

floating-point

FIFO_6

Instructions / Data

Preliminary Stage

X_INT[31:0] Y_INT[31:0] Z_INT[31:0]

CORDIC-Pipelinewith 28 Stages

QX_INT[31:0] QY_INT[31:0] QZ_INT[31:0]

Final Stage including scale operations

ES_L7_CORDIC[31:0]

± ±

hard-wired shift

Register Register

ControlUnit

,i im σRegister

X_INTi Y_INTi Instructioni ; mi ; σi

±

Register

αm,i Z_INTi

X_INTi+1 Y_INTi+1 Instructioni+1 ; σi+1 Z_INTi+1

floating-point

fixed-point

fixed-point

floating-point

FIFO_6 Abb. 12: Blockdiagramm der CORDIC-Pipeline

Die Vorstufe beinhaltet neben der Umwandlung des externen 32-Bit-Gleitkommaformats in das interne 32-Bit-Festkommaformat nach Abb. 13 auch das Laden der Befehle/Operanden aus den Speichern. Hierfür werden 6 Taktzyklen benötigt. Die Endstufe für die Skalierung des Ergebnisses sowie die

Umwandlung des internen Festkomma- in das externe Gleitkommaformat erfordert weitere 7 Taktzyklen, so dass mit Speicherung des Ergeb-nisses auf dem FIFO insgesamt 42 Pipeline-Stufen notwendig sind.

S OV H 23-Bit-Mantissa Addition-Bits

31 30 28 27 05 4

S OV H 23-Bit-Mantissa Addition-Bits

31 30 28 27 05 4

Abb. 13: Internes 32-Bit-Festkommaformat [5,6]

Zur Skalierung der x- und y-Werte innerhalb der Endstufe kommen ebenfalls die Konstantenmulti-plizierer aus [6] zum Einsatz. Bedingt durch die Pipeline-Struktur sind insgesamt 5 K1_ROM-Speicher mit je zwei Leseports zur Skalierung im zirkularen Modus und 5 K2_ROM-Speicher mit je einem Leseport zur Skalierung im hyperbolischen Modus erforderlich.

VI. Programmierung Die Gleichungen des Huber-Braun-Neuronenmo-dells aus Abschnitt II müssen nun mit der Architektur des Neuronenkerns nach Abb. 6 berech-net werden. Nach Abschnitt IV B stehen im ersten Systementwurf 200 Taktzyklen für jede AE zur Verfügung, in denen die Modellgleichungen möglichst vieler Neuronen zu implementieren sind. Es zeigt sich, dass pro Block bis zu 10 Neuronen parallel berechnet werden können, d.h. 64 10 640⋅ = Gleitkommaoperationen in diesem Zeitraum. Die einzelnen Operationen lassen sich durch die Groß-buchstaben A bis J für das jeweilige Neuron sowie der jeweiligen Operationsnummer (01 bis 64) nach Tab. 1 unterscheiden.

Nach [13] werden zur Darstellung der zeitlichen Abläufe in einer Pipeline sog. Time-Space-Diagram-me benutzt. Hier sind auf der Ordinaten- bzw. Space-Achse die einzelnen Pipeline-Stufen und auf der Abszissen- bzw. Time-Achse die einzelnen Operationsaufträge eingetragen. Um den Darstel-lungsaufwand in Grenzen zu halten, sollen hier für die einzelnen AEs nur “reduzierte“ Time-Space-Diagramme angegeben werden, bei denen auf die explizite Angabe der Space-Achse verzichtet wird. Stattdessen erfolgt nach m Verarbeitungstakten in der Pipeline die Kennzeichnung eines auf dem FIFO abgelegten Ergebnisses durch einen Pfeil mit Angabe des zugehörigen Operationsauftrags. Abb. 14 zeigt einen Ausschnitt des reduzierten Time-Space-Diagramms für das ADD_SUB_A-, MULT_B- und CORDIC-Modul.

NOP

NOP

000

ADD_SUB_MODUL_A m=9

A09

001

B09

002

C09

003

D09

004

E09

005

F09

006

---

G09

007

---

H09

008

---

I09

009

A09*

J09

010

B09*

A18

011

C09*

A31

012

D09*

A44

013

E09*

B18

014

F09*

B31

015

G09*

B44

016

H09*

C18

017

I09*

C31

018

J09*

C44

019

A18*

000

MULT_MODUL_B m=8

NOP

001

NOP

002

NOP

003

NOP

004

NOP

005

NOP

006

---

NOP

007

---

NOP

008

---

A10

009

---

B10

010

---

C10

011

---

D10

012

---

E10

013

---

F10

014

---

G10

015

---

H10

016

A10*

I10

017

B10*

J10

018

C10*

A19

019

D10*

NOP

000

CORDIC_MODUL m=42

NOP

001

NOP

002

NOP

003

NOP

004

NOP

005

NOP

006

---

NOP

007

---

NOP

008

---

NOP

009

---

NOP

010

---

NOP

011

---

NOP

012

---

NOP

013

---

NOP

014

---

NOP

015

---

A11

016

---

B11

017

---

C11

018

---

D11

019

---

NOP

NOP

000

ADD_SUB_MODUL_A m=9

A09

001

B09

002

C09

003

D09

004

E09

005

F09

006

---

G09

007

---

H09

008

---

I09

009

A09*

J09

010

B09*

A18

011

C09*

A31

012

D09*

A44

013

E09*

B18

014

F09*

B31

015

G09*

B44

016

H09*

C18

017

I09*

C31

018

J09*

C44

019

A18*

000

MULT_MODUL_B m=8

NOP

001

NOP

002

NOP

003

NOP

004

NOP

005

NOP

006

---

NOP

007

---

NOP

008

---

A10

009

---

B10

010

---

C10

011

---

D10

012

---

E10

013

---

F10

014

---

G10

015

---

H10

016

A10*

I10

017

B10*

J10

018

C10*

A19

019

D10*

NOP

000

CORDIC_MODUL m=42

NOP

001

NOP

002

NOP

003

NOP

004

NOP

005

NOP

006

---

NOP

007

---

NOP

008

---

NOP

009

---

NOP

010

---

NOP

011

---

NOP

012

---

NOP

013

---

NOP

014

---

NOP

015

---

A11

016

---

B11

017

---

C11

018

---

D11

019

---

Abb. 14: Reduziertes Time-Space-Diagramm

11

Bei der Programmierung erweist es sich als günstig, mit der Gating-Variablen ad = ad∞ für den unmittelbar aktiven, depolarisierenden Natriumkanal zu starten, d.h. zunächst V-V0d (Operationsauftrag A09) zu be-rechnen. Weiterhin ist es zweckmäßig, Gruppen von Operationsaufträgen zu bilden, die jeweils ein bis drei gleiche Operationen für alle Neuronen beinhalten. Auf diese Weise erhält man innerhalb eines Blocks für alle Neuronen den gleichen Berechnungsfortschritt.

In Abb. 14 wird im ADD_SUB_A-Modul zunächst die Gruppe [A09:J09] berechnet, anschließend die Gruppe [(A18,A31,A44):(J18,J31,J44)] als erste Arithmetikoperation zur Bestimmung der übrigen 3 Gating-Variablen pro Neuron. Das Ergebnis von A09 wird in Takt 009 auf dem zugehörigen FIFO abgelegt (FIFO_1 bzw. F1) und stellt einen Operanden für den Operationsauftrag A10 des MULT_B-Moduls dar, siehe Tab. 1. In Abb. 14 ist diese Datenabhängigkeit durch zwei über einen Pfeil verbundene Kreise kenntlich gemacht (rot für den Beginn und blau für das Ende einer Gruppe). In den grau hinterlegten Teilflächen werden NOPs zur Erzeugung von Wartezyklen ausgeführt. Nachfol-gend ist der Quellcodeausschnitt für die ersten 50 (von 200) Befehle des ADD_SUB_A- und MULT_B-Moduls angegeben. Die Speicherinhalte der ROMs sowie das reduzierte Time-Space-Diagramm für alle 6 AEs stehen in Appendix C bzw. D. // Source-Code ADD_SUB_A_MODULE // Source-Code M ULT_B_MODULE 000: NOP 000: NOP 001: SUB [0x00], 0x08 // A09 001: NOP 002: SUB [0x01], 0x08 // B09 002: NOP 003: SUB [0x02], 0x08 // C09 003: NOP 004: SUB [0x03], 0x08 // D09 004: NOP 005: SUB [0x04], 0x08 // E09 005: NOP 006: SUB [0x05], 0x08 // F09 006: NOP 007: SUB [0x06], 0x08 // G09 007: NOP 008: SUB [0x07], 0x08 // H09 008: NOP 009: SUB [0x08], 0x08 // I09 009: MULT F1, 0x 0A // A10 010: SUB [0x09], 0x08 // J09 010: MULT F1, 0x 0A // B10 011: SUB [0x00], 0x09 // A18 011: MULT F1, 0x 0A // C10 012: SUB [0x00], 0x0A // A31 012: MULT F1, 0x 0A // D10 013: SUB [0x00], 0x0B // A44 013: MULT F1, 0x 0A // E10 014: SUB [0x01], 0x09 // B18 014: MULT F1, 0x 0A // F10 015: SUB [0x01], 0x0A // B31 015: MULT F1, 0x 0A // G10 016: SUB [0x01], 0x0B // B44 016: MULT F1, 0x 0A // H10 017: SUB [0x02], 0x09 // C18 017: MULT F1, 0x 0A // I10 018: SUB [0x02], 0x0A // C31 018: MULT F1, 0x 0A // J10 019: SUB [0x02], 0x0B // C44 019: MULT F1, 0x 09 // A19 020: SUB [0x03], 0x09 // D18 020: MULT F1, 0x 0A // A32 021: SUB [0x03], 0x0A // D31 021: MULT F1, 0x 0B // A45 022: SUB [0x03], 0x0B // D44 022: MULT F1, 0x 09 // B19 023: SUB [0x04], 0x09 // E18 023: MULT F1, 0x 0A // B32 024: SUB [0x04], 0x0A // E31 024: MULT F1, 0x 0B // B45 025: SUB [0x04], 0x0B // E44 025: MULT F1, 0x 09 // C19 026: SUB [0x05], 0x09 // F18 026: MULT F1, 0x 0A // C32 027: SUB [0x05], 0x0A // F31 027: MULT F1, 0x 0B // C45 028: SUB [0x05], 0x0B // F44 028: MULT F1, 0x 09 // D19 029: SUB [0x06], 0x09 // G18 029: MULT F1, 0x 0A // D32 030: SUB [0x06], 0x0A // G31 030: MULT F1, 0x 0B // D45 031: SUB [0x06], 0x0B // G44 031: MULT F1, 0x 09 // E19 032: SUB [0x07], 0x09 // H18 032: MULT F1, 0x 0A // E32 033: SUB [0x07], 0x0A // H31 033: MULT F1, 0x 0B // E45 034: SUB [0x07], 0x0B // H44 034: MULT F1, 0x 09 // F19 035: SUB [0x08], 0x09 // I18 035: MULT F1, 0x 0A // F32 036: SUB [0x08], 0x0A // I31 036: MULT F1, 0x 0B // F45 037: SUB [0x08], 0x0B // I44 037: MULT F1, 0x 09 // G19 038: SUB [0x09], 0x09 // J18 038: MULT F1, 0x 0A // G32 039: SUB [0x09], 0x0A // J31 039: MULT F1, 0x 0B // G45 040: SUB [0x09], 0x0B // J44 040: MULT F1, 0x 09 // H19 041: SUB [0x00], 0x05 // A27 041: MULT F1, 0x 0A // H32 042: SUB [0x00], 0x06 // A40 042: MULT F1, 0x 0B // H45 043: SUB [0x00], 0x07 // A53 043: MULT F1, 0x 09 // I19 044: SUB [0x01], 0x05 // B27 044: MULT F1, 0x 0A // I32 045: SUB [0x01], 0x06 // B40 045: MULT F1, 0x 0B // I45 046: SUB [0x01], 0x07 // B53 046: MULT F1, 0x 09 // J19 047: SUB [0x02], 0x05 // C27 047: MULT F1, 0x 0A // J32 048: SUB [0x02], 0x06 // C40 048: MULT F1, 0x 0B // J45 049: SUB [0x02], 0x07 // C53 049: MULT (0x20) , 0x05 // A29 050: SUB [0x03], 0x05 // D27 050: MULT (0x20) , 0x06 // A42 … …

A Bewertung der Pipeline-Struktur Nach [13] kann man zur Bewertung der Leistung einer Pipeline verschiedene Bewertungsmaße defi-nieren, von denen hier die Effizienz herausgegriffen werden soll.

Bei der Effizienz η handelt es sich um ein Maß für die Auslastung der einzelnen Pipeline-Stufen. Diese ist umso besser, je mehr Teilflächen im Time-Space-Diagramm belegt sind. Da die Pipeline zwangsläufig aufgefüllt und geleert werden muss, sind immer nicht belegte Teilflächen vorhanden. Bezieht man diese auf die insgesamt vorhandenen Teilflächen im Time-Space-Diagramm, erhält man für die Effizienz (m = Anzahl der Pipeline-Stufen; M = Anzahl der aufeinander folgenden Operations-aufträge):

max ( 1) 1

m M M

m m M m Mη ⋅= =

⋅ + − + − (12)

Wenn die Operationsaufträge lückenlos aufeinander folgen, erhält man mit Gl. (12) die max. mögliche Effizienz. Für M >> m strebt ηmax gegen 1, d.h. das Füllen und Leeren der Pipeline fällt nicht mehr ins Gewicht. Gl. (12) kann für die einzelnen AEs nicht unmittelbar angewandt werden, da hier nicht die Anzahl M an Operationsaufträgen der Ausgangs-punkt ist, sondern die Anzahl an Taktzyklen TAnz:

max1

1Anz

m

Tη −= − (13)

Die max. Effizienz ist ein theoretischer Wert, der in der Praxis aufgrund der Datenabhängigkeit der einzelnen Module auf jeden Fall kleiner ist. Mit Gl. (14) erhält man die Effizienz einer AE unter Berück-sichtigung von Wartezyklen zwischen den einzelnen Operationsaufträgen:

Anz

M

Tη = (14)

Tab. 6 fasst die Werte für alle AEs zusammen, wobei für η die Anzahl der Operationsaufträge M aus dem reduzierten Time-Space-Diagramm nach Appendix D ermittelt wird. Man erkennt, dass bis auf das ADD_SUB_A-Modul alle AEs eine gegenüber dem theoretischen Maximalwert deutlich schlechtere Auslastung aufweisen. Die Effizienz der CORDIC-Pipeline ließe sich bei gegebener Architektur evtl. durch Erhöhung der Anzahl an Taktzyklen pro Block steigern, z.B. von 4 Blöcken mit je 200 Zyklen auf 2 Blöcke mit je 400 Zyklen. Damit verbunden wäre jedoch ein doppelt so hoher Programmieraufwand!

MODULE TAnz m M ηmax η ADD_SUB_A 200 9 160 96,0% 80,0% ADD_SUB_B 200 9 100 96,0% 50,0%

MULT_A 200 8 70 96,5% 35,0% MULT_B 200 8 120 96,5% 60,0% MULT_C 200 8 80 96,5% 40,0% CORDIC 200 42 110 79,5% 55,0%

Tab. 6: Effizienz der AEs

12

Generell dürfen die AEs aufgrund der Daten-abhängigkeit nicht isoliert betrachtet werden. Beispielsweise wurde versucht, die Operationen des MULT_A-Moduls auf die beiden übrigen MULT-Module zu verteilen. Damit konnte dann allerdings die Obergrenze von 200 Taktzyklen für die Berechnung von 10 Neuronen nicht mehr eingehalten werden, was sich wiederum negativ auf die Effizienz der verbleibenden 5 AEs auswirkte.

VII. Ergebnisse Abb. 15 zeigt einen Ausschnitt der VHDL-Simulation mit ModelSim für eine Simulationsdauer von 0.1ms, also einem Iterationszyklus des Modells. Das CLK-Signal der Stimuli-Datei weist eine Periodendauer von 10ns auf, was einer FPGA-Clockfrequenz von 100MHz entspricht. Dadurch können die 4 Blöcke eines Neuronenzyklus pro Schrittweite 10 Mal durchlaufen bzw. die Modellgleichungen von insge-samt 4 10 10 400⋅ ⋅ = Neuronen in Echtzeit berechnet werden.

Abb. 15: VHDL-Simulationsausschnitt für ∆t = 0.1ms

Mit der gewählten Skalierung der Zeitachse von Abb. 15 sind diese 10 Durchläufe der 4 Blöcke gut zu erkennen.

Der zur Hardware-Verifikation eingesetzte FPGA XC4VLX60 der Virtex-4-Serie stellt ca. 53000 LUTs zur Verfügung, von denen etwa 16700 LUTs für die Synthese benötigt werden. Das entspricht ca. 31% der Hardware-Ressourcen des Chips. Die max. Taktrate wird vom Synthesetool mit knapp 120MHz angegeben.

Um die Auswirkungen von Rundungsfehlern zu vergleichen, sollen für eine Simulationsdauer von 10s die mittels einer C-Konsolenanwendung berech-neten Membranpotentiale eines Neurons sowohl für den Datentyp double als auch für float in hexadezi-maler Form jeweils in einem Texteditor abgelegt werden. Hierbei ist ein double-Ergebnis vor der Speicherung auf float zu runden, ein float-Ergebnis wird direkt übernommen. Schließlich sind die von der RS232-Schnittstelle eingelesenen FPGA-Werte in einem dritten Editor abzulegen, siehe Abb. 16.

Die abhängig vom gewählten Rauschparameter und dem Injektionsstrom ermittelten Ergebnisse in den Editoren können nun mit Matlab eingelesen und grafisch dargestellt werden. Auf diese Weise kann für die ersten Tests die Entwicklung einer grafischen Benutzeroberfläche entfallen. Abb. 17 zeigt den Verlauf der einzelnen Membranpotentiale für eine Simulationsdauer von 10s (Oben: C-Code (double); Mitte: C-Code (float); Unten: FPGA (float)), wobei noise_D, I_inj und die Pseudo-Zufallszahlen-sequenz jeweils identisch sind zu Abb. 2.

Abb. 16: Ausschnitt der drei Ergebnis-Editoren

Abb. 17a: Membranpotentiale; n_D = 0.1, I_inj = 1.0

13

Abb. 17b: Membranpotentiale; n_D = 0.1, I_inj = 1.2

Abb. 17c: Membranpotentiale; n_D = 0.1, I_inj = 1.4

Abb. 17d: Membranpotentiale; n_D = 0.4, I_inj = 1.0

Man erkennt, dass aufgrund der Rundung die ein-zelnen Membranpotentiale zwar nicht identisch, aber doch ähnlich sind. Mit steigendem Injektions-strom nimmt auch die Anzahl der generierten Spikes zu. Für das letzte Teilbild mit dem Ausgangs-Injek-tionsstrom und deutlich höherem Rauschanteil stimmen sogar alle drei Verläufe überein. Die grund-legenden Eigenschaften des Huber-Braun-Modells gehen somit trotz der geringeren Genauigkeit der FPGA-Lösung nicht verloren.

VIII. Zusammenfassung Mit der vorgestellten Architektur eines digitalen Neu-ronenkerns können auf einem XC4VLX60-FPGA der Virtex-4-Serie bei einer Taktfrequenz von 100MHz die Huber-Braun-Modellgleichungen von 400 Neuro-nen in Echtzeit berechnet werden. Hierbei handelt es sich um 256 Mio. 32-Bit-Gleitkommaoperationen

pro Sekunde. Die in den Modellgleichungen auf-tretenden mathematischen Funktionen werden über den CORDIC-Algorithmus in einer einheitlichen Architektur bestimmt. Dieser gestattet auch die Durchführung der Division, so dass kein expliziter Dividierer erforderlich ist. Insgesamt ist der FPGA etwa 10-mal schneller als ein PC mit 2,5GHz Taktrate. Trotz der geringeren Genauigkeit gegen-über double aus Matlab bzw. C und den damit ver-bundenen Rundungseffekten bleiben die prinzipi-ellen Eigenschaften des Neuronenmodells erhalten.

Aktuell wird jedes Neuron isoliert betrachtet und über einen konstanten Injektionsstrom depolarisiert. Der nächste Schritt ist die Implementierung der postsynaptischen Potentiale und der Netztopologie. Weiterhin soll zur schnelleren Datenübertragung zwischen FPGA und Host-Rechner USB 2.0 zum Einsatz kommen.

IX. Literatur [1] Jarzab, M.: Hardware Architecture of a Neuron

Model; Overseas Work Experience Program – Report, University of Applied Sciences Giessen-Friedberg, March 2008.

[2] Huber, M.T.; Braun, H.A.: Stimulus – response curves of a neuronal model for noisy subthreshold oscillations and related spike generation; University of Marburg, 2005.

[3] Rabe, D.: Versuchsanleitung Praktikum Digital-technik; Fachhochschule OOW, 2008.

[4] Alfke, P.: Efficient Shift Registers, LFSR Counters, and Long Pseudo-Random Sequence Generators; Xilinx, 1996.

[5] Timmermann, D.; Rix, B.; Hahn, H.; Hosticka, B.J.: 24 Bit CMOS Gleitkomma Vektorarithme-tik Chip; Fraunhofer-Institut für mikroelektroni-sche Schaltungen und Systeme, 1993.

[6] Beuler, M.: CORDIC-Algorithmus zur Auswer-tung elementarer Funktionen in Hardware; FH-Report, Juni 2008.

http://dok.bib.fh-giessen.de/opus/volltexte/2009/4148/ [7] Beuler, M.; Bonath, W.: Berechnung elemen-

tarer Funktionen für das Huber/Braun-Neuronenmodell in digitaler Architektur; MPC-Workshop Konstanz, Juli 2008.

http://dok.bib.fh-giessen.de/opus/volltexte/2009/4149/ [8] Liebig, H.; Thome, S.: Logischer Entwurf digita-

ler Systeme; 3. Auflage, Springer-Verlag, 1996. [9] Jorke, G.: Rechnergestützter Entwurf digitaler

Schaltungen; 1. Auflage, Carl Hanser Verlag, 2004.

[10] Beuler, M.: Realisierung von Arithmetik-Baugruppen für das 32-Bit-Gleitkommaformat der Norm ANSI/IEEE 754 mittels VHDL; FH-Report, April 2008.

http://dok.bib.fh-giessen.de/opus/volltexte/2009/4146/ [11] Wunderlich, H.-J.: Rechnerorganisation; Vorle-

sungsskript, Universität Stuttgart, WS02/03. [12] Xilinx: Virtex-4 Family Overview; Sept. 2007. [13] Schiffmann, W.; Schmitz, W.: Technische Infor-

matik 2; 3. Auflage, Springer-Verlag, 1999.

14

Appendix A Zusammenfassung der aus [2] entnommenen numerischen Parameter für das Huber-Braun-Neuronenmodell: delta_t = 0.1; % Schrittweite in ms C_M = 1; g_l = 0.1; V_l = -60; % schneller depolarisierender Natriumkanal für Spik e-Generierung g_d = 2.0; V_0d = -25; s_d = 0.25; V_d = 50; % schneller repolarisierender Kaliumkanal für Spike -Generierung g_r = 2.0; V_0r = -25; s_r = 0.25; V_r = -90; tau_r = 2; % langsamer depolarisierender Natriumkanal für Oszi llationen g_sd = 0.4; V_sd = 50; V_0sd = -40; s_sd = 0.25; tau_sd = 10; % langsamer repolarisierender Kaliumkanal für Oszil lationen g_sr = 2.0; V_sr = -90; V_0sr = -40; s_sr = 0.25; tau_sr = 50;

Appendix B Nachfolgend sind die Initialwerte der ersten 20 Einträge von FIFO_7 sowie der Register QLFSR_0 bis QLFSR_2 zur Generierung der Pseudo-Zufalls-zahlen aufgeführt. In einem Matlab-m-File bzw. in C-Quellcode sind für die QLFSRs andere Startwerte vorzusehen, um die oben angegebenen 20 Zufallszahlen berechnen zu können. Nach dem Durchlaufen des ersten Blocks sind diese Registerinhalte dann identisch zu den Initialwerten des VHDL-Quellcodes. type MMX64_32 is array(63 downto 0) of std_logic_ve ctor(31 downto 0); signal QRAM64_32: MMX64_32 := ("00000000000000000000000000000000", "00000000000000000000000000000000", ... ... "00000000000000000000000000000000", "00000000000000000000000000000000", "00111111000010101011101100000000", -- 0x3F0ABB00 "00111111011100101101000100000000", -- 0x3F72D100 "00111111000101101101011000000000", -- 0x3F16D600 "00111110101000100000101000000000", -- 0x3EA20A00 "00111110010000110101110000000000", -- 0x3E435C00 "00111101010001010011000000000000", -- 0x3D453000 "00111111011101000101110100000000", -- 0x3F745D00 "00111111011010011100110100000000", -- 0x3F69CD00 "00111111011101001101111100000000", -- 0x3F74DF00 "00111111001000000111000100000000", -- 0x3F207100 "00111111011000010101111100000000", -- 0x3F615F00 "00111101100100111111100000000000", -- 0x3D93F800 "00111111010100011110010000000000", -- 0x3F51E400 "00111111010010101001001100000000", -- 0x3F4A9300 "00111110101000111001001000000000", -- 0x3EA39200 "00111101110000101001100000000000", -- 0x3DC29800 "00111100000101111100000000000000", -- 0x3C17C000 "00111101010100111111000000000000", -- 0x3D53F000 "00111110000001011101000000000000", -- 0x3E05D000 "00111111011000100000000100000000"); -- 0x3F620100 -- initial values of QLFSR_X in PRN_MODULE signal QLFSR_0 : std_logic_vector(31 downto 0) := X "FFB9EC33"; signal QLFSR_1 : std_logic_vector(31 downto 0) := X "B3DE9246"; signal QLFSR_2 : std_logic_vector(31 downto 0) := X "0B3D3E9D"; -- in Matlab- or C-Code QLFSR_0 = X"025FE201"; QLFSR_1 = X"18532174"; QLFSR_2 = X"51C90D3F";

Appendix C Die Tabellen A1 und A2 zeigen die Inhalte der ROMs der ADD_SUB- und MULT-Module. Aus Tab. A1 geht hervor, dass die Injektionsströme für 40 Neuronen (10 Neuronen mal 4 Blöcke) abgelegt sind, jeweils mit dem Wert 1.2. Im experimentellen Stadium können diese Werte individuell angepasst werden. Eine Erweiterung des Speichers auf insgesamt 400 Injektionsströme ist hier nicht vorgesehen, d.h. für jeden der 10 Blockdurchläufe pro Schrittweite gelten die gleichen Ströme.

Adr. (hex)

Bedeu-tung

Wert (dez)

Adr. (hex)

Bedeu- tung

Wert (dez)

00 Null 0 20 I_inj_B2 1.2 01 Eins 1 21 I_inj_C2 1.2 02 -Eins -1 22 I_inj_D2 1.2 03 V_l -60 23 I_inj_E2 1.2 04 V_d 50 24 I_inj_F2 1.2 05 V_r -90 25 I_inj_G2 1.2 06 V_sd 50 26 I_inj_H2 1.2 07 V_sr -90 27 I_inj_I2 1.2 08 V_0d -25 28 I_inj_J2 1.2 09 V_0r -25 29 I_inj_A3 1.2 0A V_0sd -40 2A I_inj_B3 1.2 0B V_0sr -40 2B I_inj_C3 1.2 0C --- --- 2C I_inj_D3 1.2 0D --- --- 2D I_inj_E3 1.2 0E --- --- 2E I_inj_F3 1.2 0F --- --- 2F I_inj_G3 1.2 10 --- --- 30 I_inj_H3 1.2 11 --- --- 31 I_inj_I3 1.2 12 --- --- 32 I_inj_J3 1.2 13 --- --- 33 I_inj_A4 1.2 14 --- --- 34 I_inj_B4 1.2 15 I_inj_A1 1.2 35 I_inj_C4 1.2 16 I_inj_B1 1.2 36 I_inj_D4 1.2 17 I_inj_C1 1.2 37 I_inj_E4 1.2 18 I_inj_D1 1.2 38 I_inj_F4 1.2 19 I_inj_E1 1.2 39 I_inj_G4 1.2 1A I_inj_F1 1.2 3A I_inj_H4 1.2 1B I_inj_G1 1.2 3B I_inj_I4 1.2 1C I_inj_H1 1.2 3C I_inj_J4 1.2 1D I_inj_I1 1.2 3D --- --- 1E I_inj_J1 1.2 3E --- --- 1F I_inj_A2 1.2 3F --- ---

Tab. A1: ROM-Inhalt der ADD_SUB-Module

Adr. (hex)

Bedeu- tung

Wert (dez)

Adr. (hex)

Bedeu-tung

Wert (dez)

00 Null 0 20 ρ(25.0°) 1

01 Eins 1 21 ϕ(25.5°) 1.05647

02 -Eins -1 22 ρ(25.5°) 1.0132047

03 g_l 0.1 23 ϕ(26.0°) 1.11612

04 g_d 2 24 ρ(26.0°) 1.0265837

05 g_r 2 25 ϕ(26.5°) 1.17915

06 g_sd 0.4 26 ρ(26.5°) 1.0401393

07 g_sr 2 27 ϕ(27.0°) 1.24573

08 -s_d -0.25 28 ρ(27.0°) 1.0538739

09 -s_r -0.25 29 --- --- 0A -s_sd -0.25 2A --- --- 0B -s_sr -0.25 2B --- --- 0C dt/tau_r 0.05 2C --- --- 0D dt/tau_sd 0.01 2D --- --- 0E dt/tau_sr 0.002 2E --- --- 0F dt/C_M 0.1 2F --- --- 10 2π 6.2831855 30 --- ---

11 -4*0.0*dt 0 31 --- --- 12 -4*0.1*dt -0.04 32 --- --- 13 -4*0.2*dt -0.08 33 --- --- 14 -4*0.3*dt -0.12 34 --- --- 15 -4*0.4*dt -0.16 35 --- --- 16 -4*0.5*dt -0.2 36 --- --- 17 ϕ(23.0°) 0.802742 37 --- ---

18 ρ(23.0°) 0.94888 38 --- ---

19 ϕ(23.5°) 0.84807 39 --- ---

1A ρ(23.5°) 0.9614097 3A --- ---

1B ϕ(24.0°) 0.895958 3B --- ---

1C ρ(24.0°) 0.97410476 3C --- ---

1D ϕ(24.5°) 0.946551 3D --- ---

1E ρ(24.5°) 0.98696744 3E --- ---

1F ϕ(25.0°) 1 3F --- ---

Tab. A2: ROM-Inhalt der MULT-Module

15

Appendix D E

44

02

5

C1

8 *F

18

02

6

C3

1 *F

31

02

7

C4

4 *F

44

028

D1

8 *G

18

02

9

D31 *

G3

1

03

0

D4

4 *G

44

031

E1

8 *H

18

03

2

E3

1 *H

31

03

3

E4

4 *H

44

03

4

F1

8 *I1

8

03

5

F3

1 *I3

1

03

6

F4

4 *I4

4

03

7

G1

8 *J1

8

03

8

G3

1 *J3

1

03

9

G4

4 *J4

4

04

0

H1

8 *A

27

04

1

H3

1 *A

40

04

2

H4

4 *A

53

04

3

I18 *

B2

7

04

4

I31 *

B4

0

04

5

I44 *

B5

3

04

6

J18 *

C2

7

04

7

J31 *

C4

0

04

8

J44 *

C53

04

9

A2

7 *

NO

P

02

5

---

NO

P

026

---

NO

P

02

7

---

NO

P

02

8

---

NO

P

02

9

---

NO

P

030

---

NO

P

03

1

---

NO

P

032

---

NO

P

033

---

NO

P

03

4

---

NO

P

03

5

---

NO

P

036

---

NO

P

037

---

NO

P

038

---

NO

P

03

9

---

NO

P

04

0

---

NO

P

04

1

---

NO

P

042

---

NO

P

043

---

NO

P

04

4

---

NO

P

045

---

NO

P

04

6

---

NO

P

04

7

---

NO

P

04

8

---

NO

P

04

9

---

NO

P

02

5

---

NO

P

02

6

---

NO

P

02

7

---

NO

P

02

8

---

NO

P

02

9

---

NO

P

03

0

---

NO

P

03

1

---

NO

P

032

---

NO

P

03

3

---

NO

P

034

---

NO

P

035

---

NO

P

03

6

---

NO

P

03

7

---

NO

P

038

---

NO

P

039

---

NO

P

04

0

---

NO

P

04

1

---

NO

P

04

2

---

NO

P

04

3

---

NO

P

04

4

---

NO

P

04

5

---

NO

P

04

6

---

NO

P

04

7

---

NO

P

048

---

A2

8

049

---

C1

9

02

5

J10 *

C3

2

02

6

A1

9 *C

45

02

7

A3

2 *D

19

028

A4

5 *D

32

02

9

B1

9 *D

45

030

B32 *

E1

9

03

1

B4

5 *E

32

03

2

C1

9 *E

45

03

3

C3

2 *F

19

03

4

C4

5 *F

32

03

5

D1

9 *F

45

03

6

D3

2 *G

19

03

7

D4

5 *G

32

03

8

E1

9 *G

45

03

9

E3

2 *H

19

04

0

E4

5 *H

32

04

1

F1

9 *H

45

04

2

F3

2 *I1

9

04

3

F4

5 *I3

2

04

4

G1

9 *I4

5

04

5

G3

2 *J1

9

04

6

G4

5 *J3

2

04

7

H1

9 *J4

5

04

8

H3

2 *A

29

04

9

H4

5 *

NO

P

025

---

NO

P

026

---

NO

P

02

7

---

NO

P

02

8

---

NO

P

02

9

---

NO

P

03

0

---

NO

P

03

1

---

NO

P

03

2

---

NO

P

03

3

---

NO

P

034

---

NO

P

03

5

---

NO

P

036

---

NO

P

03

7

---

NO

P

03

8

---

NO

P

03

9

---

NO

P

04

0

---

NO

P

041

---

NO

P

042

---

NO

P

04

3

---

NO

P

04

4

---

NO

P

045

---

NO

P

046

---

NO

P

04

7

---

NO

P

04

8

---

NO

P

04

9

---

J11

025

---

A2

0

026

---

A3

3

02

7

---

A4

6

02

8

---

B2

0

02

9

---

B33

030

---

B4

6

031

---

C2

0

03

2

---

C3

3

03

3

---

C4

6

034

---

D2

0

03

5

---

D3

3

036

---

D4

6

03

7

---

E2

0

03

8

---

E3

3

03

9

---

E4

6

04

0

---

F2

0

041

---

F3

3

042

---

F4

6

04

3

---

G2

0

04

4

---

G3

3

045

---

G46

046

---

H20

04

7

---

H3

3

04

8

---

H4

6

04

9

---

E4

4

02

5

C1

8 *F

18

02

6

C3

1 *F

31

02

7

C4

4 *F

44

028

D1

8 *G

18

02

9

D31 *

G3

1

03

0

D4

4 *G

44

031

E1

8 *H

18

03

2

E3

1 *H

31

03

3

E4

4 *H

44

03

4

F1

8 *I1

8

03

5

F3

1 *I3

1

03

6

F4

4 *I4

4

03

7

G1

8 *J1

8

03

8

G3

1 *J3

1

03

9

G4

4 *J4

4

04

0

H1

8 *A

27

04

1

H3

1 *A

40

04

2

H4

4 *A

53

04

3

I18 *

B2

7

04

4

I31 *

B4

0

04

5

I44 *

B5

3

04

6

J18 *

C2

7

04

7

J31 *

C4

0

04

8

J44 *

C53

04

9

A2

7 *

NO

P

02

5

---

NO

P

026

---

NO

P

02

7

---

NO

P

02

8

---

NO

P

02

9

---

NO

P