Grundlagen der Rechnerarchitektur - userpages.uni-koblenz.deunikorn/lehre/gdra/ss19/04...

Transcript of Grundlagen der Rechnerarchitektur - userpages.uni-koblenz.deunikorn/lehre/gdra/ss19/04...

Grundlagen der Rechnerarchitektur

Prozessor

Übersicht• Datenpfad• Control• Pipelining• Data‐Hazards• Control‐Hazards• Multiple‐Issue

2Grundlagen der Rechnerarchitektur ‐ Prozessor

Datenpfad einer einfachen MIPS‐CPU

Grundlagen der Rechnerarchitektur ‐ Prozessor 3

Ziel

Grundlagen der Rechnerarchitektur ‐ Prozessor 4

Konstruktion des Datenpfads einer einfachen MIPS‐CPU als Blockschaltbild. Die CPU hat 32 Register und soll folgende MIPS‐Instruktionen realisieren:

Instruktionen für Speicherzugriff: lw, swlw $s1, 4($s2) # $s1 = Memory[$s2+4]sw $s1, 4($s2) # Memory[$s2+4] = $s1

Arithmetisch‐logische Instruktionen: add, sub, and, or, sltadd $s0, $s1, $s2 # $s0 = $s1 + $s2slt $s0, $s1, $s2 # $s0 = ($s1<$s2)? 1 : 0

Branch‐ Instruktion: beqbeq $s1, $s2, 4096 # $pc = $pc + 4 + 4096<<2, wenn $s1=$s2

Datenpfad einer einfachen MIPS‐CPUErster Abschnitt des Datenpfades

Grundlagen der Rechnerarchitektur ‐ Prozessor 5

Benötigte Bausteine

Grundlagen der Rechnerarchitektur ‐ Logik und Arithmetik 6Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Speicherbaustein in dem die abzuarbeitenden Instruktionen stehen. „Instruction Address“ ist 32‐Bit groß. Wenn an den Leitungen „Instruction Address“ eine Adresse anliegt, liegt im nächsten Taktzyklus eine 32‐Bit lange Instruktion auf den „Instruction“ Leitungen.

Register in dem der Programm‐Counter steht. Hier steht die Adresse der nächsten abzuarbeitenden Instruktion.

Eine ALU, die fest auf die Funktion Addieren verdrahtet ist. Mit dieser ALU wird der Program‐Counter in 4er Schritten erhöht, um auf die nächste folgende Instruktion zu zeigen.

Erster Schritt der Instruktionsausführung

Grundlagen der Rechnerarchitektur ‐ Prozessor 7

Mit dem neuen Clock‐Signal passiert folgendes:

Instruction‐Fetch:Lag der Program‐Counter‐Wert seit dem letzten Clock‐Signal am Instruction‐Memory an, erscheint mit dem nächsten Clock‐Signal die nächste auszuführende Instruktion an der Instruction‐Leitung.

Program‐Counter erhöhen:Damit der Speicher schon mit dem Bereitstellen der nächsten Instruktion beginnen kann, wird der Program‐Counter direkt zu Beginn der Instruktionsabarbeitung auf die nächste abzuarbeitende Instruktion gesetzt.

Das Blockschaltbild dazu

Grundlagen der Rechnerarchitektur ‐ Prozessor 8

Datenpfad einer einfachen MIPS‐CPUArithmetische‐Logische Operationen

Grundlagen der Rechnerarchitektur ‐ Prozessor 9

Erinnerung, Instruktionen vom R‐Typ‐Format:

Solche Instruktionen machen immer folgendes:• Lese zwei Register (src1 und src2)• Führe eine ALU‐Operation darauf aus• Schreibe Ergebnis zurück in ein Register (dest)

Alle hier zu realisierenden arithmetisch‐logischen Instruktionen (d.h. add, sub, and, or, slt) sind R‐Typ‐Instruktionen.

Zum Speichern der Registerinhalte und zur Durchführung der Rechenoperationen benötigen wir zwei weitere Bausteine.

Betrachten zunächst R‐Typ‐Instruktionen

Grundlagen der Rechnerarchitektur ‐ Prozessor 10

opcode src1 src2 dest shamt funct6 Bit 5 Bit 5 Bit 5 Bit 5 Bit 6 Bit

R‐Typ(Register‐Typ)

31 26 25 21 20 16 15 11 10 6 5 0

Register‐File und ALU

Grundlagen der Rechnerarchitektur ‐ Prozessor 11

Auf den Read‐Data‐Leitungen liegen die 32‐Bit‐Inhalte der Register, die den 5‐Bit‐Read‐Register‐Inputs entsprechen. Ein Register‐File ist wesentlich schneller als der Speicher. Daten liegen in einem Instruktionszyklus unmittelbar auf den Read‐Data‐Leitungen vor. In einem Taktzyklus überschriebener Registerinhalt ist erst im darauf folgenden auf den Read‐Data‐Leitungen sichtbar.Zum Schreiben in ein Register müssen die Daten auf den Write‐Data‐Leitungen vorliegen und die RegWrite‐Leitung muss aktiv sein.

Die ALU rechnet auf 32‐Bit‐Werten. Die ALU‐Operation wird über die 4‐Bit ALU‐Operation‐Leitungen gewählt; hierzu später mehr. Die Zero‐Leitung ist 0, wenn das ALU‐Ergebnis 0 ergab.

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Erweiterung des Blockschaltbilds

Grundlagen der Rechnerarchitektur ‐ Prozessor 12

Datenpfad einer einfachen MIPS‐CPUDie Branch‐Instruktion beq

Grundlagen der Rechnerarchitektur ‐ Prozessor 13

Betrachten nun Branch‐Instruktion beq

Grundlagen der Rechnerarchitektur ‐ Prozessor 14

Erinnerung, Branch‐Instruktionen beq ist vom I‐Typ‐Format:

beq‐Instruktion macht immer folgendes:• Ziehe zwei Register voneinander ab (reg1 und reg2)• Wenn das Ergebnis ungleich 0: nächste Instruktion ist bei PC+4• Wenn das Ergebnis gleich 0 :

• Sign‐Extension von 16‐Bit‐Offset auf 32‐Bit Zahl x• x = 4*x (lässt sich durch ein Links‐Shift von 2 erreichen)• nächste Instruktion ist bei PC+4+x

Berechnung reg1 ‐ reg2 ist durch den Datenpfad schon realisiert.Für den Rest brauchen wir noch zwei neue Bausteine:

31 26 25 21 20 16 15 0opcode reg1 reg2 Offset6 Bit 5 Bit 5 Bit 16 Bit

I‐Typ(Immediate‐Typ)

Sign‐Extend und Shift‐Left 2

Grundlagen der Rechnerarchitektur ‐ Logik und Arithmetik 15

Sign‐Extend

Vorzeichenbehaftetes Ausweiten von k auf n

Leitungen (z.B. 16 auf 32).

Shift‐Left 2

Links oder Rechts‐Shift von Leitungen (z.B. Shift‐Left 2)

k n

Wir müssen außerdem eine Auswahl treffen• Wenn die aktuelle Instruktion ein beq ist, dann berechne den PC nach vorhin beschriebener Vorschrift.

• Wenn die Instruktion kein beq ist, dann bestimme den PC wie bisher gehabt; also PC=PC+4.

• Zum Treffen von Auswahlen brauchen wir eine weiteren Bausteintyp:

Grundlagen der Rechnerarchitektur ‐ Prozessor 16

Multiplexer

Grundlagen der Rechnerarchitektur ‐ Logik und Arithmetik 17

0 Mux 1Select

A B

C

Für ein Bit Für n Bit(z.B. 32 Bit)

0 Mux 1Select

A B

C

3232

32

C = A, wenn Select = 0C = B, wenn Select = 1

Für n‐Bit‐Select(z.B. 2 Bit)

MuxSelect

A1 A4

C

A2 A3

C = A0, wenn Select = 00C = A1, wenn Select = 01C = A2, wenn Select = 10C = A3, wenn Select = 11

Erweiterung des Blockschaltbilds

Grundlagen der Rechnerarchitektur ‐ Prozessor 18

Datenpfad einer einfachen MIPS‐CPUZugriff auf den Datenspeicher

Grundlagen der Rechnerarchitektur ‐ Prozessor 19

Betrachten nun Load‐ und Store‐Word

Grundlagen der Rechnerarchitektur ‐ Prozessor 20

Erinnerung, Instruktionen lw und sw sind vom I‐Typ‐Format:

Die Adresse des Speicherzugriffs berechnet sich wie folgt:• Sign‐Extension von 16‐Bit‐Offset auf 32‐Bit Zahl x• Adresse ist Inhalt von reg1 + xHierzu werden wir vorhandene ALU und Sign‐Extend mitbenutzen

Der Speicherinhalt wird dann• bei lw in Register reg2 geschrieben• bei sw mit Registerinhalt von reg2 überschrieben

Zur Vereinfachung trennen wir im Folgenden den Speicher der Instruktionen vom Speicher der Daten. Letzterer ist wie folgt:

31 26 25 21 20 16 15 0opcode reg1 reg2 Offset6 Bit 5 Bit 5 Bit 16 Bit

I‐Typ(Immediate‐Typ)

Datenspeicher

Grundlagen der Rechnerarchitektur ‐ Prozessor 21

Speicherbaustein in dem die Daten liegen. „Address“, „Write‐Data“ und „Read‐Data“ sind 32‐Bit groß. In keinem Taktzyklus wird gleichzeitig gelesen und geschrieben. Schreiben oder lesen wird über Signale an MemWrite und MemRead durchgeführt. Der Grund für ein MemRead ist, dass sicher gestellt sein muss, dass die anliegende Adresse gültig ist (mehr dazu im Kapitel Speicher).

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Erweiterung des Blockschaltbilds

Grundlagen der Rechnerarchitektur ‐ Prozessor 22

Eine Übung zum Abschluss

Grundlagen der Rechnerarchitektur ‐ Prozessor 23

Wie lässt sich das Blockschaltbild des Datenpfads erweitern, sodass auch die MIPS‐Instruktion j unterstützt wird?

Zur Erinnerung:

j 4096 # $pc = 4096<<2 + oberste vier# Bit von $pc

Control einer einfachen MIPS‐CPU

Grundlagen der Rechnerarchitektur ‐ Prozessor 24

Ziel

Grundlagen der Rechnerarchitektur ‐ Prozessor 25

Bisher haben wir lediglich den Datenpfad einer einfachen MIPS‐CPU entworfen.

Die Steuerleitungen der einzelnen Bausteine zeigen noch ins Leere.

Jetzt wollen wir festlegen, wann zur Abarbeitung unserer Instruktionen (d.h. lw, sw,add, sub, and, or, slt,beq ) welche Steuerleitungen an oder aus sein sollen. Den Baustein der das macht, nennt man „Control“.

Wir trennen die Control in zwei Teile:ALU‐Control: Legt für jeden Befehl die ALU‐Operation fest.Main‐Unit‐Control: Legt für jeden Befehl die übrigen Steuerleitungen fest.

Wir verwenden auf den nächsten Folien die folgende Terminologie:Steuerleitung an: assertedSteuerleitung aus: deasserted

Control einer einfachen MIPS‐CPUALU‐Control

Grundlagen der Rechnerarchitektur ‐ Prozessor 26

Vorüberlegung: Die passenden ALU‐Funktionen

Grundlagen der Rechnerarchitektur ‐ Prozessor 27Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Control‐Eingänge der betrachteten ALU

• Für Load‐ und Store‐Instruktionen lw, sw brauchen wir die ALU‐Funktion add.

• Für die arithmetisch‐logischen Instruktionen add, sub, and, or,slt brauchen wir die entsprechende passende ALU‐Funktion.

• Für die Branch‐Instruktion beq brauchen wir die ALU‐Funktion sub.

Vorüberlegung: die Instruktionsformate

Grundlagen der Rechnerarchitektur ‐ Prozessor 28Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Wenn der Wert von Bit 31 bis 26 in der gefetchten Instruktion gleich• 0: arithmetisch‐logische Instruktion (d.h. add,sub,and,or,slt).Die Funktion ist mit dem Wert von Bit 5 bis 0 festgelegt.

• 35 oder 43: Load‐ bzw. Store‐Instruktion (d.h. lw, sw).

• 4: Branch‐Instruktion (d.h. beq).

(I-type)

(I-type)

ALU‐Control

Grundlagen der Rechnerarchitektur ‐ Prozessor 29

ALU‐Control

Belegung der ALU‐Steuerleitungen, so dass die ALU die richtigen ALU‐Operation ausführt.

Ausgabe Eingabe

5‐Bit‐Funct‐Field der Instruktion

ALUOp in Abhängigkeit des Instruktionstyps

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

In einer Wahrheitstabelle zusammengefasst

Grundlagen der Rechnerarchitektur ‐ Prozessor 30

Eingabe Ausgabe

Daraus lässt sich mechanisch eine kombinatorische Schaltung generieren, die wir im Folgenden mit dem ALU‐Control‐Symbol abstrakt darstellen.

ALU‐Control

ALUOp

Instruction[5:0]

(also das Funct‐Field der Instruktion)

ALU‐Operation

0

0

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Erweiterung des Blockschaltbilds

Grundlagen der Rechnerarchitektur ‐ Prozessor 31

Control einer einfachen MIPS‐CPUMain‐Unit‐Control

Grundlagen der Rechnerarchitektur ‐ Prozessor 32

Opcode bestimmt Steuerleitungsbelegungen

Grundlagen der Rechnerarchitektur ‐ Prozessor 33

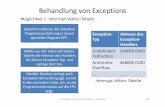

Instruction RegDst ALUSrcMemto‐Reg

Reg‐Write

Mem‐Read

Mem‐Write Branch

ALU‐Op1

ALU‐Op0

R‐format (0)

lw (35)

sw (43)

beq (4)Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Eingabe:Instruction [31‐26] Ausgabe

Auch hier wieder

Grundlagen der Rechnerarchitektur ‐ Prozessor 34

Aus voriger Wahrheitstabelle lässt sich mechanisch eine kombinatorische Schaltung generieren, die wir im Folgenden mit dem Control‐Symbol abstrakt darstellen.

ControlInstruction[31—26](also: das Opcode‐Field der Instruktion)

RegDstBranchMemReadMemtoRegALUOpMemWriteALUSrcRegWrite

Erweiterung des Blockschaltbilds

Grundlagen der Rechnerarchitektur ‐ Prozessor 35

Beispiel für eine R‐Typ‐Instruktion

• Instruktion wird gefetched und PC um 4 erhöht.• Die Register $t2 (Instruction [25‐21]) und $t3 (Instruction [20‐16]) werden aus dem Register‐File geladen.

• Die ALU führt die in dem Function‐Field (Instruction[5‐0]) codierte Operation auf den gelesenen Register‐Daten aus.

• Das Ergebnis der ALU wird in Register $t1 (Instruction[15‐11]) zurück geschrieben.

Grundlagen der Rechnerarchitektur ‐ Prozessor 36

add $t1, $t2, $t3

Beispiel für eine Load/Save‐Instruktion

• Instruktion wird gefetched und PC um 4 erhöht.• Das Register $t2 (Instruction [25‐21]) wird aus dem Register‐File geladen.

• Die ALU addiert das Register‐Datum und den 32‐Bit Sign‐exteded 16‐Bit‐Immediate‐Wert 8 (Instruction [15‐0]).

• Die Summe aus der ALU wird als Adresse für den Datenspeicher verwendet.

• Das Datum aus dem Datenspeicher wird in das Register‐File geschrieben. Das Register in das geschrieben wird ist $t1 (Instruction [20‐16]).

Grundlagen der Rechnerarchitektur ‐ Prozessor 37

lw $t1, 8($t2)

Beispiel für eine Branch‐Instruktion

• Instruktion wird gefetched und PC um 4 erhöht.• Die Register $t1 (Instruction [25‐21]) und $t2 (Instruction[20‐16]) werden aus dem Register‐File geladen.

• Die Haupt‐ALU subtrahiert die ausgelesenen Register‐Daten voneinander.Die zusätzliche ALU addiert PC+4 auf den 32‐Bit Sign‐exteded und um 2 nach links geshifteten 16‐Bit‐Immediate‐Wert 42 (Instruction [15‐0]).

• Das Zero‐Ergebins der Haupt‐ALU entscheidet ob der PC auf PC+4 oder auf das Ergebnis der zusätzlichen ALU gesetzt wird.

Grundlagen der Rechnerarchitektur ‐ Prozessor 38

beq $t1, $t2, 42

Eine Übung zum Abschluss

Grundlagen der Rechnerarchitektur ‐ Prozessor 39

In der vorigen „Übung zum Abschluss“ wurde das Blockschaltbild des Datenpfads so erweitert, sodass auch die MIPS‐Instruktion junterstützt wird.

Wie müssen Control und Alu‐Control modifiziert werden (wenn überhaupt), damit die MIPS‐Instruktion j auch von Seiten des Control unterstützt wird?

Erinnerung:j addr # Springe pseudo-direkt nach addr

000010 addressOpcodeBits 31‐26

AdresseBits 25‐0

J‐Typ

Pipelining

Grundlagen der Rechnerarchitektur ‐ Prozessor 40

PipeliningInstruktionszyklen

Grundlagen der Rechnerarchitektur ‐ Prozessor 41

MIPS‐Instruktionszyklus

Grundlagen der Rechnerarchitektur ‐ Prozessor 42

Ein MIPS‐Instruktionszklus besteht aus:

1. Instruktion aus dem Speicher holen(IF: Instruction‐Fetch)

2. Instruktion decodieren und Operanden aus Register lesen(ID: Instruction‐Decode/Register‐File‐Read)

3. Ausführen der Instruktion oder Adresse berechnen(EX: Execute/Address‐Calculation)

4. Datenspeicherzugriff(MEM: Memory‐Access)

5. Resultat in Register abspeichern(WB: Write‐Back)

Instruktionszyklen in unserem Blockschaltbild

Grundlagen der Rechnerarchitektur ‐ Prozessor 43

Instruktionszyklen generell• Instruktionszyklen anderer moderner CPUs haben diese oder eine sehr ähnliche Form von Instruktionszyklen.

• Unterschiede sind z.B.:– Instruktion decodieren und Operanden lesen sind zwei getrennte Schritte. Dies ist z.B. notwendig,

• wenn Instruktionen sehr komplex codiert sind (z.B. x86 Instruktionen der Länge 1 bis 17 Byte)

• wenn Instruktionen Operanden im Speicher anstatt Register haben (z.B. einige Instruktionen bei x86)

Grundlagen der Rechnerarchitektur ‐ Prozessor 44

PipeliningDie Pipelining‐Idee

Grundlagen der Rechnerarchitektur ‐ Prozessor 45

Annahme die einzelnen Abschnitte des MIPS‐Instruktionszyklus benötigen folgende Ausführungszeiten:Instruction‐Fetch 200ps, Register‐Read 100ps, ALU‐Operation 200ps, Data‐Access 200ps, Register‐Write 100ps.

Wie hoch dürfen wir unseren Prozessor (ungefähr) Takten?

Die längste Instruktion benötigt 800ps. Also gilt für den Clock‐Cycle c:

Single‐Cycle‐Performance

Grundlagen der Rechnerarchitektur ‐ Prozessor 46Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Die Pipelining‐Idee am Beispiel Wäsche waschen

Grundlagen der Rechnerarchitektur ‐ Prozessor 47Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Waschen

Trocknen

Falten

Einräumen

Bearbeitungszeit pro Wäscheladung bleibt dieselbe (Delay).Gesamtzeit für alle Wäscheladungen sinkt (Throughput).

Was ist die Performance‐Ratio?

Grundlagen der Rechnerarchitektur ‐ Prozessor 48

Annahme jeder Arbeitsgang beansprucht dieselbe Zeit. Was ist die Performance‐Ratio für n Wäscheladungen?

Generell für k „Pipeline‐Stufen“, d.h. k Arbeitsgänge und gleiche Anzahl Zeiteinheiten t pro Arbeitsgang?

Im Folgenden betrachten wir zunächst ein ganz einfaches Programm:lw $1, 100($0)lw $2, 200($0)lw $3, 300($0)lw $4, 400($0)lw $5, 500($0)

Bemerkung: Da die MIPS‐Registernamen im Folgenden nicht von Bedeutung sind, geben wir in den Programmbeispielen häufig nur noch die Registernummern (z.B. wie oben $0 und $1) an. Außerdem betrachten wir das spezielle Zero‐Register momentan nicht.

Wie kann man die Pipelining‐Idee im Falle unseres MIPS‐Prozessors anwenden?

Pipelining für unseren MIPS‐Prozessor

Grundlagen der Rechnerarchitektur ‐ Prozessor 49

Die Pipeline nach den ersten drei Instruktionen

Grundlagen der Rechnerarchitektur ‐ Prozessor 50Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Annahme:IF = 200psID = 100psEX = 200psMEM = 200psWB = 100ps

Was ist die Performance‐Ratio?

Grundlagen der Rechnerarchitektur ‐ Prozessor 51

Wie eben gezeigt wäre für k Pipeline‐Stufen und eine große Zahl an ausgeführten Instruktionen die Performance‐Ratio gleich k, wenn jede Pipeline‐Stufe dieselbe Zeit beanspruchen würde.

Allerdings brauchen die einzelnen Stufen s1,...,sk unterschiedliche Zeiteinheiten: t1,..., tk. Somit ist die Performance‐Ratio für n Instruktionen:

Mit den Zeiten aus dem vorigen Beispiel für n also:

Die Performance‐Ratio wird durch die langsamste Stufe bestimmt.

Taktung

Grundlagen der Rechnerarchitektur ‐ Prozessor 52

Annahme die einzelnen Abschnitte des MIPS‐Instruktionszyklus benötigen die bisher betrachteten Ausführungszeiten:Instruction‐Fetch 200ps, Register‐Read 100ps, ALU‐Operation 200ps, Data‐Access 200ps, Register‐Write 100ps.

Wie hoch dürfen wir unseren Prozessor (ungefähr) Takten? Die längste Stufe benötigt 200ps. Also gilt für den Clock‐Cycle c:

Achtung: Maximal mögliche Taktung hängt aber auch von anderen Faktoren ab. (Erinnerung: Power‐Wall).

Quiz

Grundlagen der Rechnerarchitektur ‐ Prozessor 53

Welchen CPI‐Wert suggeriert das MIPS‐Pipelining‐Beispiel?

Achtung: der CPI‐Wert ist in der Regel höher, wie wir noch sehen.

Der Ansatz ist noch zu naiv

Grundlagen der Rechnerarchitektur ‐ Prozessor 54

lw $1, 100($0)lw $2, 200($0)lw $3, 300($0)lw $4, 400($0)lw $5, 500($0)Beispiel:

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

IF ID EX MEM WB

PipeliningPipeline‐Register

Grundlagen der Rechnerarchitektur ‐ Prozessor 55

Pipeline‐Stufen brauchen Pipeline‐Register

Grundlagen der Rechnerarchitektur ‐ Prozessor 56Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Pipeline‐Stufen brauchen Pipeline‐Register

Grundlagen der Rechnerarchitektur ‐ Prozessor 57Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Control

…Änderungim Tafelbild

Write‐Register darf erst in der WB‐Stufe gesetzt werden.

RegDst steht mit der Entscheidung von Control erst in der EX‐Stufe fest.

Wird durchgereicht

Was speichern die Pipeline‐Register?

Grundlagen der Rechnerarchitektur ‐ Prozessor 58

Wir schauen uns den Weg einer einzigen Instruktion durch die Pipeline an; und zwar den der Load‐Word‐Instruktion lw.

Auf dem Weg durch die Pipeline überlegen wir, was alles in den Pipeline‐Registern IF/ID, ID/EX, EX/MEM und MEM/WB stehen muss.

In der Darstellung verwenden wir folgende Konvention.

Bedeutet: Register/Speicher wird gelesen Bedeutet: Register/Speicher wird beschrieben

Was speichern die Pipeline‐Register?

Grundlagen der Rechnerarchitektur ‐ Prozessor 59

IF/ID:• Instruktion• PC+4 (z.B. für beq)

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Grundlagen der Rechnerarchitektur ‐ Prozessor 60

Was speichern die Pipeline‐Register?

ID/EX:• PC+4 (z.B. für beq)• Inhalt Register 1• Inhalt Register 2• Sign‐ext. Immediate (z.B. für beq)• Das Write‐Register(wird im Letzten Zyklus von lw gebraucht)

Generell: Alles was in einem späteren Clock‐Cycle noch verwendet werden könnte, muss durchgereicht werden.

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Grundlagen der Rechnerarchitektur ‐ Prozessor 61

Was speichern die Pipeline‐Register?

EX/MEM:• Ergebnis von PC+4+Offset (z.B. für beq)

• Zero der ALU(z.B. für beq)

• Result der ALU

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

• Register 2 Daten (z.B. für sw)• Das Write‐Register (wird im letzten Zyklus von lw gebraucht)

Was speichern die Pipeline‐Register?

Grundlagen der Rechnerarchitektur ‐ Prozessor 62

MEM/WB:• Das geleseneDatum aus demSpeicher (wird dann vonlw im nächsten Zyklus ins Write‐Register geschrieben)

• Das Ergebnis der ALU‐Operation (für diearithmetisch‐logischen Instruktionen)

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Grundlagen der Rechnerarchitektur ‐ Prozessor 63

Was speichern die Pipeline‐Register?

Für die letzte Pipeline‐Stufe braucht man kein Pipeline‐Register.

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Zusätzlich wird noch Control‐Info gespeichert

Grundlagen der Rechnerarchitektur ‐ Prozessor 64Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Control

…

Zusätzlich wird noch Control‐Info gespeichert

Grundlagen der Rechnerarchitektur ‐ Prozessor 65Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Control hängt von der Instruktion ab. Damit muss Control‐Info erst ab ID/EX‐Register gespeichert werden.

Das ID/EX‐Register muss bereitstellen:• RegDst• ALUOp (2)• ALUSrc

Das EX/MEM‐Register muss bereit stellen:• Branch•MemRead•MemWrite

Werden durch‐gereicht.

Das MEM/WB‐Register muss bereit stellen:• MemtoReg• RegWrite

PipeliningPipelining‐Visualisierung

Grundlagen der Rechnerarchitektur ‐ Prozessor 66

Pipelining‐Visualisierung

Grundlagen der Rechnerarchitektur ‐ Prozessor 67

Zusammenfassung der vorhin implizit eingeführten Visualisierungen und Einführung einer neuen Visualisierung.

Wir betrachten folgenden Beispiel‐Code:

lw $10, 20($1)sub $11, $2, $3add $12, $3, $4lw $13, 24($1)add $14, $5, $6

Wir unterscheiden generell zwischen zwei Visualisierungsarten:Single‐Clock‐Cylce‐Pipeline‐Diagramm undMultiple‐Clock‐Cycle‐Pipeline‐Diagramm

Single‐Clock‐Cycle‐Pipeline‐Diagramm

Grundlagen der Rechnerarchitektur ‐ Prozessor 68Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Einfaches Multiple‐Clock‐Cycle‐Pipeline‐Diagramm

Grundlagen der Rechnerarchitektur ‐ Prozessor 69Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Detaillierteres Multiple‐Clock‐Cycle‐Pipeline‐Diagramm

Grundlagen der Rechnerarchitektur ‐ Prozessor 70Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

IF ID EX MEM WB

PipeliningKomplexere Pipelines

Grundlagen der Rechnerarchitektur ‐ Prozessor 71

Komplexere Piplelines• Pipeline‐Stufen sind nicht auf 5 festgelegt!• z.B. weitere Unterteilung von IF, ID, EX, MEM, WB

– Erlaubt höhere Taktung– Kann aufgrund der Instruktions‐Komplexität erforderlich sein– Kann aufgrund von Instruktionen mit zeitlich unbalancierten Stufen erforderlich sein

• Wie „pipelined“ man x86 ISA mit Instruktionslängen zwischen 1 und 17 Bytes?– Komplexe Instruktionen der x86 ISA werden in Folge von Mikroinstruktionen

übersetzt– Mikroinstruktionssatz ist vom Typ RISC– Pipelining findet auf den Mikroinstruktionen statt

• Beispiel AMD Opteron X4:

Grundlagen der Rechnerarchitektur ‐ Prozessor 72

Was das ist sehen wir noch im Kapitel Multiple‐Issue

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Pipeline‐Stufen einiger ausgewählter ProzessorenMikroprozesor Jahr Taktrate Pipeline‐Stufen LeistungIntel 486 1989 25 MHz 5 5 WIntel Pentium 1993 66 MHz 5 10 WIntel Pentium Pro 1997 200 MHz 10 29 WIntel Pentium 4 Willamette 2001 2000 MHz 22 75 WIntel Pentium 4 Prescott 2004 3600 MHz 31 103 WIntel Core 2006 2930 MHz 14 75 WUltraSPARC IV+ 2005 2100 MHz 14 90 WSun UltraSPARC T1 (Niagara) 2005 1200 MHz 6 70 W

Grundlagen der Rechnerarchitektur ‐ Prozessor 73

Pipeline‐Stufen sinken wieder?• Aggressives Pipelining ist sehr Leistungshungrig• Aktueller Trend eher zu Multi‐Cores mit geringerer

Leistungsaufnahme pro Core.

Data‐Hazards

Grundlagen der Rechnerarchitektur ‐ Prozessor 74

Motivation

Grundlagen der Rechnerarchitektur ‐ Prozessor 75

Ist die Pipelined‐Ausführung immer ohne Probleme möglich?

Beispiel:sub $2, $1, $3and $12, $2, $5or $13, $6, $2add $14, $2, $2sw $15, 100($2)

Also, alle vier nachfolgenden Instruktionen hängen von der sub‐Instruktion ab.

Annahme:$2 speichert 10 vor der sub‐Instruktion.$2 speichert ‐20 nach der sub‐Instruktion.

Betrachten wir die Pipeline:

sub $2, $1, $3and $12, $2, $5or $13, $6, $2add $14, $2, $2sw $15, 100($2)

Problem Rückwärtsabhängigkeiten

Grundlagen der Rechnerarchitektur ‐ Prozessor 76

Instr.‐Zeile

Sollte aus $2 lesen

Liest aus $2

and

or

add

sw

Data‐Hazard

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Behandeln von Data‐Hazards mittels Forwarding

Grundlagen der Rechnerarchitektur ‐ Prozessor 77Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Allgemeine Lösung mittels Forwarding‐Unit

Grundlagen der Rechnerarchitektur ‐ Prozessor 78Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

012

012

WB WB

EX/MEM.Rd

MEM/WB.Rd

Implementation der Forwarding‐Unit

Grundlagen der Rechnerarchitektur ‐ Prozessor 79

Bemerkungen

Grundlagen der Rechnerarchitektur ‐ Prozessor 80

Die Bestimmung von ForwardB erfolgt analog. (Übung)

Das Ganze muss noch als Wahrheitstabelle aufgeschrieben und dann als kombinatorische Schaltung realisiert werden.

Wie sieht die Wahrheitstabelle von ForwardA nach voriger hergeleiteter Vorschrift aus? (Übung) [Tipp: um Platz zu sparen sollte man möglichst viele „don‘t cares“ verwenden.]

Nicht auflösbare Data‐Hazards

Grundlagen der Rechnerarchitektur ‐ Prozessor 81

Nicht jeder Data‐Hazard lässt sich durch Forwardingauflösen. Beispiel: Zugriff auf vorher gelesenes Register.

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Pipeline‐Stall als Lösung

Grundlagen der Rechnerarchitektur ‐ Prozessor 82Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Allgemeine Lösung mittels Hazard‐Detection‐Unit

Grundlagen der Rechnerarchitektur ‐ Prozessor 83Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Implementation der Hazard‐Detection‐Unit

Grundlagen der Rechnerarchitektur ‐ Prozessor 84

Quiz: Vermeiden von Pipeline‐Stalls

Grundlagen der Rechnerarchitektur ‐ Prozessor 85

lw $t1, 0($t0)

lw $t2, 4($t0)

add $t3, $t1, $t2

sw $t3, 12($t0)

lw $t4, 8($t0)

add $t5, $t1, $t4

sw $t5, 16($t0)

Wo findet ein Pipe‐line‐Stall statt? Bitte ankreuzen.

Bitte Befehle umorganisie‐ren, sodass alle Stalls vermieden werden.

Anzahl Taktzyklen mit Stalls?Anzahl Taktzyklen ohne Stalls?

Control‐Hazards

Grundlagen der Rechnerarchitektur ‐ Prozessor 86

Control‐Hazards

Grundlagen der Rechnerarchitektur ‐ Prozessor 87Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Branch‐Not‐Taken‐Strategie und Pipeline‐Flush

Grundlagen der Rechnerarchitektur ‐ Prozessor 88

Flush = Verwerfe Instruktionen in der Pipeline. Hier: Setze IF/ID‐, ID/EX‐ und EX/MEM‐Register auf 0.

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Reduktion des Branch‐Delays• Adressberechnung kann schon in der

ID‐Stufe stattfinden• beq und bne erfordert lediglich ein

32‐Bit‐XOR und ein 32‐Bit‐OR– Dazu braucht man keine ALU– Also auch in der ID‐Stufe realisierbar

• Damit ist der Sprung schon in der ID‐Stufe entschieden

Grundlagen der Rechnerarchitektur ‐ Prozessor 89Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Beispiel: für $1 und $3:

Reduktion des Branch‐Delays

• Konsequenz– Branch‐Delay ist damit ein Instruktions‐Zyklus– Wir brauchen lediglich ein Flush‐IF/ID‐Register

Grundlagen der Rechnerarchitektur ‐ Prozessor 90

Reduktion des Branch‐Delays• Achtung!

– Forwarding aus späteren Stufen macht die Sache kompliziert.

– Kann Pipeline‐Stall aufgrund von Data‐Hazards erforderlich machen.

• z.B. ein Zyklus, wenn ALU‐Ergebnis in den Vergleich einfließt

• z.B. zwei Zyklen, wenn Vergleichsoperator einen Schritt vorher aus dem Speicher geladen wurde

– Betrachten wir aber hier nicht genauer.

Grundlagen der Rechnerarchitektur ‐ Prozessor 91Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Dynamic‐Branch‐Prediction‐Strategie

Grundlagen der Rechnerarchitektur ‐ Prozessor 92

Unterer Teil der Adresse

Branch hat stattgefunden

0x00 10x04 00x08 1...0xf8 00xfc 0

Branch‐Prediction‐Buffer

0x400000 : lw $1, 0($4)0x400004 : beq $1, $0, 400x400008 : add $1, $1, $10x40000c : ......

...0x40c004 : bne $3, $4, 120...

Vorhersagegenauigkeit

Grundlagen der Rechnerarchitektur ‐ Prozessor 93

Annahme unendlich langer Loop, der immer 9 mal und dann einmal nicht durchlaufen wird. Was ist die Vorhersagegenauigkeit der vorher beschriebenen Branch‐Prediction?

Lässt sich das verbessern?

loop: ......bne $1,$2,loop...j loop

N‐Bit‐Vorhersage am Beispiel 2‐Bit

Grundlagen der Rechnerarchitektur ‐ Prozessor 94Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Vorhersagegenauigkeit

Grundlagen der Rechnerarchitektur ‐ Prozessor 95

Annahme unendlich langer Loop, der immer 9 mal und dann einmal nicht durchlaufen wird. Was ist die Vorhersagegenauigkeit der vorher beschriebenen 2‐Bit‐Branch‐Prediction?

loop: ......bne $1,$2,loop...j loop

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Branch‐Delay‐Slot‐Idee

Grundlagen der Rechnerarchitektur ‐ Prozessor 96

loop: ......bne $1,$2,loop<instruktion><instruktion>

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

• Wird immer ausgeführt.• Instruktion muss aber unabhängig vonder Branch‐Entscheidung sein.

• Das muss der Compiler entscheiden.• Im Zweifelsfall: nop passt immer.

Beispiele von Branch‐Delay‐Slot‐Schedules

Grundlagen der Rechnerarchitektur ‐ Prozessor 97Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Weniger Branches mit Conditional‐Instruktionen

Grundlagen der Rechnerarchitektur ‐ Prozessor 98

Beispiel MIPS‐Instruktionen movn und movz:movn $8, $11, $4 # $8 = $11, wenn $4 != 0movz $8, $11, $4 # $8 = $11, wenn $4 == 0

Beispiel ARM‐ISA:ADDEQ r0,r1,r2 ; If zero flag set then…

; ... r0 = r1 + r2

Quiz

Grundlagen der Rechnerarchitektur ‐ Prozessor 99

Betrachte die folgenden Branch‐Strategien:1. Vorhersage Branch findet statt2. Vorhersage Branch findet nicht statt3. Dynamische Branch‐Vorhersage (mit 90% Genauigkeit)

Was ist die beste Strategie, wenn:

• Branch findet mit 5% Häufigkeit statt?

• Branch findet mit 95% Häufigkeit statt?

• Branch findet mit 70% Häufigkeit statt?

Multiple‐Issue

Grundlagen der Rechnerarchitektur ‐ Prozessor 100

Motivation• Bisher: Instruction‐Level‐Parallelism (ILP) durch Pipelining

– ILP kann durch Pipeline‐Stufe erhöht werden– Pipelines mit mehr Stufen sind anfälliger gegenüber Data‐ und Control‐

Hazards– Also: Pipeline‐Stufen nur bis zu gewisser Tiefe sinnvoll– Außerdem: Grenzen aufgrund der Leistungsaufnahme– CPI bleibt gleich oder steigt sogar (wegen Hazards), Clock‐Rate steigt

• Hier eine weitere Methode um ILP zu steigern: Multiple‐Issue– Replikation von internen CPU‐Strukturen, sodass mehrere Instruktionen pro

Pipeline‐Stufe möglich sind– CPI sinkt und Clock‐Rate bleibt gleich (oder sinkt sogar wegen erhöhter

Komplexität)– Beispiel: CPI eines 4‐Wege‐Multiple‐Issue‐Mikroprozessor hat eine ideale CPI

von? 0.25!– CPI liegt aber in der Regel höher, wie wir gleich sehen werden

• Wir unterscheiden zwischen:– Static‐Multiple‐Issue: Entscheidungen werden zur Compile‐Zeit gefällt– Dynamic‐Multiple‐Issue: Entscheidungen werden zur Laufzeit gefällt

(auch Superskalare CPU bezeichnet)

Grundlagen der Rechnerarchitektur ‐ Prozessor 101

Multiple‐IssueStatic‐Multiple‐Issue

Grundlagen der Rechnerarchitektur ‐ Prozessor 102

Generelle Idee• Eine große Instruktion pro Clock‐Cycle• Große Instruktion besteht aus mehreren gleichzeitig stattfindenden Operationen

• Aber nicht jede Kombination von Operationen möglich

• Beispiel:– ALU‐Operation und Speicheroperation gleichzeitig möglich

– Aber zwei ALU‐Operation auf einmal nicht möglich

• Terminologie: VLIW (Very Long Instruction Word)

Grundlagen der Rechnerarchitektur ‐ Prozessor 103

Beispiel am MIPS‐Datenpfad

Grundlagen der Rechnerarchitektur ‐ Prozessor 104Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Extra ALU für gleichzeitige Adresskalkulation

ALU für arithmetische Operationen

Statische Two‐Issue Pipeline im Betrieb

Grundlagen der Rechnerarchitektur ‐ Prozessor 105Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Was ist der CPI‐Wert?

Was ist nun die Aufgabe des Compilers?

Grundlagen der Rechnerarchitektur ‐ Prozessor 106Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Loop: lw $t0, 0($s1) # $t0=Array-Elementaddu $t0, $t0, $s2 # addiere Wertsw $t0, 0($s1) # Speichere Elementaddi $s1, $s1, -4 # nächstes Elementbne $s1, $zero, Loop # solange $s1 != 0

Compiler erzeugt Assembler‐Code:

und ordnet Instruktionen so an, dass keine Pipeline‐Stalls entstehen

Was ist der CPI‐Wert?

Verbesserung: Loop‐Unrolling

Grundlagen der Rechnerarchitektur ‐ Prozessor 107

Loop: lw $t0, 0($s1) # $t0=Array-Elementaddu $t0, $t0, $s2 # addiere Wertsw $t0, 0($s1) # Speichere Elementaddi $s1, $s1, -4 # nächstes Elementbne $s1, $zero, Loop # solange $s1 != 0

Code wie vorher (der Einfachheit sei Loop‐Index Vielfaches von 4):

Loop‐Body vier mal kopiert und Register‐Renaming

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Was ist der CPI‐Wert?

Multiple‐IssueDynamic‐Multiple‐Issue

Grundlagen der Rechnerarchitektur ‐ Prozessor 108

Generelle‐Idee• CPU entscheidet, ob und wie viele aufeinander folgende Instruktionen parallel gestartet werden können

• Compiler erzeugt nur eine Folge von Instruktionen; kein VLIW

• Instruktions‐Scheduling des Compilers nicht mehr erforderlich aber trotzdem aus Performance‐Gründen sinnvoll

• Verbesserung der Superskalarität durch dynamisches Pipeline‐Scheduling: Instruktionsreihenfolge darf geändert werden, um Stalls zu vermeiden

Grundlagen der Rechnerarchitektur ‐ Prozessor 109

Dynamic‐Pipeline‐Scheduling Motivation

Grundlagen der Rechnerarchitektur ‐ Prozessor 110

lw $t0, 20($s2) # zunächst $t0 ladenaddu $t1, $t0, $t2 # addu durch lw verzögertsub $s4, $s4, $t3 # sub könnte schon startenslti $t5, $s4, 20 # und genau so auch slti

Warum nicht sub (und ggf. slti) vor addu vorziehen?

Dynamic‐Pipeline‐Scheduling generell

Grundlagen der Rechnerarchitektur ‐ Prozessor 111Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

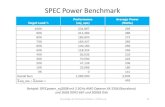

Wiedervorlage: Daten einiger ausgewählter Prozessoren

Grundlagen der Rechnerarchitektur ‐ Prozessor 112Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Zusammenfassung und Literatur

Grundlagen der Rechnerarchitektur ‐ Prozessor 113

Zusammenfassung• Schlechte Performance von Single‐Cylce‐Ansatz• Instruktionsabarbeitung besteht aus mehreren Zyklen• Moderne Prozessoren nutzen dies für

– Pipelining– Multiple‐Issue

• Allgemein als Instruction‐Level‐Parallelism bezeichnet• Für High‐Level‐Programmierer ist die Parallelität nicht sichtbar

– Sichtbar auf Assembler‐Ebene– Sichtbar auf Compiler‐Ebene

• Hauptprobleme die die Parallelität einschränken– Daten‐Abhängigkeiten– Control‐Abhängigkeiten

• Methoden um Data‐ und Control‐Hazards zu reduzieren– Scheduling– Spekulation

• Sichtbare Grenze der Power‐Wall ist erreicht• Trend zu Multicores mit einfacheren Pipelines• Konsequenz: Parallelität nicht mehr von der Hardware gekapselt

Grundlagen der Rechnerarchitektur ‐ Prozessor 114

Quiz

Bildquelle: www.geemag.de/wp‐content/artikel_endgegner_bild.jpg

Welchen Einfluss hat Pipelining auf den CPI‐Wert?[ ] Der CPI‐Wert bleibt immer unverändert. [ ] Der CPI‐Wert kann unter 1 fallen. [ ] Der CPI‐Wert steigt in der Regel an.

Grundlagen der Rechnerarchitektur ‐ Logik und Arithmetik 115

Mittels Pipelining kann man die Taktrate eines Rechners erhöhen.[ ] Stimmt! [ ] Nein, das ist völliger Quatsch.

Eine Pipeline mit k Stufen erreicht asymptotisch immer eine Performance‐Ratio von k.[ ] Jawohl. [ ] Nein, die Ratio kann darunter liegen.[ ] Nein, die Ratio kann sogar noch höher liegen.

Welchen Einfluss hat Superskalarität auf den CPI‐Wert?[ ] Der CPI‐Wert bleibt immer unverändert, [ ] Der CPI‐Wert steigt an.[ ] Der CPI‐Wert kann unter 1 fallen.

Pipelining erhöht den Durchsatz aber reduziert nicht die Instruktions‐Latenz.[ ] Nein, Durchsatz und Latenz sinken [ ] Nein, Durchsatz und Latenz steigen [ ] Ja, das ist richtig

Super! Geschafft. Auf zum nächsten Level.

Literatur[PattersonHennessy2012] David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 20124.1 Introduction4.2 Logic Design Conventions4.3 Building a Datapath4.4 A Simple Implementation Scheme4.5 An Overview of Pipelining4.6 Pipelined Datapath and Control4.7 Data Hazards: Forwarding versus Stalling4.8 Control Hazards4.10 Parallelism and Advanced Instruction‐Level Parallelism4.11 Real Stuff: the AMD Opteron X4 (Barcelona) Pipeline

Grundlagen der Rechnerarchitektur ‐ Prozessor 116