. . .

description

Transcript of . . .

.

.

.

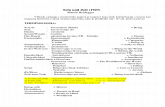

006ch0080h

7

6

1

0

0002h0000h

xxx1h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

1nterrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

xxx1h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

1nterrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

xxx1h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten

(retten; Adr. ISR)nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

006ch

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten

(retten; Adr. ISR)nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

30a7h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten

(retten; Adr. ISR)nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

30a7h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

30a8h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

30a8h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

.

.

.

006ch0080h

7

6

1

0

0002h0000h

3xxxh

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

3xxxh

.

.

.

006ch0080h

7

6

1

0

0002h0000h

3end+1h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

reti

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

3xxxh

3endh

.

.

.

006ch0080h

7

6

1

0

0002h0000h

xxx1h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

reti

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

3xxxh

3endh

.

.

.

006ch0080h

7

6

1

0

0002h0000h

xxx1h

int

nmi

Bef-Zähler

nmi-Vek

Reg‘s

/0-Vek

BRDZ

Vektor Vektor

PIC CPU

Adr.Adr.Adr.

.

.

.

30a7h

0000h

0002h

006ch

xxx1h

.

.

.

reti

.

.

.

.

.

.

30a7h

xxx0h

Int.-Tabelle

ISR

Daten-Bus

Adress-Bus

HS

+1

Bitfolge aus HS holen

Befehlszähler + 1

Befehlsregister interpretieren

Befehl komplett ? nein

ja Bitfolge aus HS holen

Befehlszähler + 1Befehl abarbeiten(Mikroprogramm)

Interrupt ? ja Interrupt bearbeiten(retten; Adr. ISR)

nein

Adr. Mikroprogramm

Befehlsregister

Reg. i

3xxxh

3endh