Bitübertragungsschicht 2.1 Signal-to-Ground-Verbindungen 2 ... · 2.3 EMV/EMC-Schutzmaßnahmen ......

Transcript of Bitübertragungsschicht 2.1 Signal-to-Ground-Verbindungen 2 ... · 2.3 EMV/EMC-Schutzmaßnahmen ......

1

Bitübertragungsschicht 1 Netzwerke in der Automatisierungstechnik .................................................. 2 2 Busanschaltungen ....................................................................................... 2

2.1 Signal-to-Ground-Verbindungen ....................................................... 2 2.1.1 Das 1-Draht-Bussystem .............................................................. 2

2.1.1.1 Funktionsprinzip ..................................................................... 2 2.1.1.2 1-WIRE SIGNALING .............................................................. 3 2.1.1.3 Einsatzbeispiel: Das DS1920 Temperature iButton ................ 5 2.1.1.4 Einsatzbeispiel: Die 'intelligente/smart' Batterie ..................... 5

2.1.2 Das Kommunikationsprotokoll I2C ............................................. 7 2.1.2.1 Konzept und Topologie .......................................................... 7 2.1.2.2 Elektrische Eigenschaften ...................................................... 9 2.1.2.3 Transferraten .......................................................................... 9 2.1.2.4 Hardware-Grundlagen ............................................................ 9 2.1.2.5 Datenübertragung ................................................................ 10 2.1.2.6 Steuersignale ....................................................................... 11 2.1.2.7 Adressierung ........................................................................ 12 2.1.2.8 Transferarten ........................................................................ 13

2.1.3 Der Inter-IC Sound Bus ............................................................. 14 2.1.3.1 Einsatzgebiete ...................................................................... 14 2.1.3.2 Aufbau .................................................................................. 14 2.1.3.3 Eigenschaften ...................................................................... 14 2.1.3.4 Transferraten ........................................................................ 15

2.1.4 Ein I2C-Derivat, der SMBus ....................................................... 15 2.1.4.1 Einsatzbeispiel für I2C-Bus .................................................. 18

2.1.5 Die SPI-Schnittstelle ................................................................. 21 2.1.5.1 Funktionsprinzip ................................................................... 21 2.1.5.2 Beispielimplementierung PIC16C65-Master u. 82527-Slave 23

2.1.6 Beispiel: Ansteuerung digitaler Potis ........................................... 23

2.2 Differentielle Kommunikationsverbindungen ................................ 25 2.2.1 Motivation für differentielle Kommunikationsverbindungen .......... 25 2.2.2 Guidelines for Proper Wiring of an RS-485 Network ................... 27 2.2.3 Struktur des RS485-Bussystems ................................................. 36 2.2.4 Die hardwaretechnische Realisierung des RS485-Busses .......... 37 2.2.5 Bsp.: Der MAXIM Low-Power RS-485/RS-422 Transceiver ........ 38

2.3 EMV/EMC-Schutzmaßnahmen ......................................................... 38

2.3.1 Elektrostatische Entladungen ...................................................... 38 2.3.2 Transienten ................................................................................. 38 2.3.3 Störabstrahlungen ....................................................................... 38

2.4 Anwendungsbeispiele aus der Praxis ............................................ 40

2.4.1 Einsatzbeispiel RS485-Kommunikation mit Wechselrichtern ...... 40 2.4.2 Vergleich von RS232-, RS485- und Powerline-Verbindungen .... 42

2

Netzwerke in der Automatisierungstechnik

1 Busanschaltungen

Busanschaltungen realisieren die Bitübertragungsschicht auf dem ISO/OSI-Layer 1. Bei in-dustriellen Feldbussystemen hat sich hier insbesondere die RS-485-Schnittstelle für eine „multi point“-Verbindung als Übertragungsstandard durchgesetzt.

Zuvor soll jedoch auf typische „point to point“-Verbindungen eingegangen werden, wie z. B. I2C und SPI und anhand diesen die Verbindungstypen erläutert werden.

1.1 Signal-to-Ground-Verbindungen

1.1.1 Das 1-Draht-Bussystem

1.1.1.1 Funktionsprinzip

Stromversorgung

Bild: Prinzipelle Verdrahtung mit Pull-Up Widerstand

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open drain or 3-state outputs.

The 1-Wire port of the DS1920 (data contact) is open drain with an internal circuit equivalent to that shown in the next Figure.

A multidrop bus consists of a 1-Wire bus with multiple slaves attached. The 1-Wire bus re-quires a pull up resistor of approximately 5 kW. The idle state for the 1-Wire bus is high.

If for any reason a transaction needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. If this does not occur and the bus is left low for more than 120 ms, one or more of the devices on the bus will be reset.

3

Bild: Sender- und Empfänger-Konfiguration der „1-wire“-Hardware

1.1.1.2 1-WIRE SIGNALING

The DS1920 requires strict protocols to ensure data integrity. The protocol consists of five types of signaling on one line: Reset Sequence with Reset Pulse and Presence Pulse, Write 0, Write 1, Read Data and Strong Pullup.

All these signals except Presence Pulse are initiated by the bus master.

Initialization Sequence

The initialization sequence required to begin any communication with the DS1920 is shown in the next Figure.

Bild: Sequenz zur Initialisierung der Datenkommunikation

A Reset Pulse followed by a Presence Pulse indicates the DS1920 is ready to accept a ROM command. The bus master transmits (TX) a Reset Pulse (tRSTL, minimum 480 ms). The bus master then releases the line and goes into receive mode (RX).

The 1-Wire bus is pulled to a high state via the pullup resistor. After detecting the rising edge on the 1-Wire line, the DS1920 waits (tPDH, 15-60 ms) and then transmits the Presence Pulse (tPDL, 60-240 ms).

READ/WRITE TIME SLOTS

4

The definitions of write and read time slots are illustrated in the next figure. All time slots are initiated by the master driving the data line low. The falling edge of the data line syn-chronizes the DS1920 to the master by triggering a delay circuit in the DS1920.

During write time slots, the delay circuit determines when the DS1920 will sample the data line.

For a read data time slot, if a 0 is to be transmitted, the delay circuit determines how long the DS1920 will hold the data line low overriding the 1 generated by the master. If the data bit is a 1, the DS1920 will leave the read data time slot unchanged.

Bild: „Write-1“-Time Slot

Bild: „Write-0“-Time Slot

Bild: Read-Data Time Slot

5

Bild: Die hierarchische Struktur des „1-wire“-Protokolls

1.1.1.3 Einsatzbeispiel: Das DS1920 Temperature iButton

siehe unter Applikation auf der Webseite www.Dallas.com

1.1.1.4 Einsatzbeispiel: Die 'intelligente/smart' Batterie

Zunehmend sind heutige aufladbare Batterien 'intelligent/smart'. Ausgerüstet mit einem Mik-rochip sind diese Batterien in der Lage, mit dem Ladegerät und auch mit dem Benutzer zu kommunizieren. Eine typische Anwendung von 'intelligenten' Batterien sind die Batterien von Notebooks-Computer und Video-Kameras. Außerdem werden solche Batterien auch in bio-medizinischen Geräten und im militärischen Bereich eingesetzt.

Die einfachste 'intelligente' Batterie enthält nur einen Chip, der dem Ladegerät die anzuwen-denden Ladealgorithmen vermittelt. In den Augen eines so genannten Smart Battery System (SBS) Forums verdienen jedoch solche Batterien die Bezeichnung 'intelligent' nicht.

6

Was macht eine Batterie 'intelligent'? Das Forum SBS erklärt, dass eine 'intelligente' Batterie in der Lage sein muss, SoC-Angaben machen zu können. Benchmarq war um 1990 die erste Firma, die ein Konzept anbot, das die Technologie des Treibstoffmessgerätes verwendete. Heute stellen verschiedene Hersteller solche Chips her. Der Bereich umfasst 1-Draht-Systeme, 2-Draht-Systeme bis zum SMBus (System Management System). Befassen wir uns zuerst mit dem 1-Draht-System.

Das 1-Draht-System liefert die Datenkommunikation über 1 Draht. Eine solche Batterie ver-wendet 3 Verbindungsdrähte: Die gemeinsamen positiven und negativen Batterieanschlüsse und einen eindrahtigen Datenanschluss, welcher ebenfalls die Synchronisationsinformatio-nen liefert. Aus Sicherheitsgründen verwenden die meisten Hersteller einen separaten Draht für den Temperatursensor. Das nachstehende Bild zeigt das Prinzipschema eines 1-Draht-Systems.

Bild: 1-Draht-System einer 'intelligenten' Batterie

Ein einziger Draht wird für die Datenübermittlung verwendet. Aus Sicherheitsgründen ver-wenden die meisten Hersteller einen separaten Draht für den Temperatursensor.

Das 1-Draht-System speichert den Batteriecode und überwacht die Batteriedaten, inklusive Temperatur, Spannung, Strom und SoC (Ladezustand).

Die meisten 1-Draht-Systeme haben keine einheitliche Ausführungsform, noch bieten sie eine einheitliche Messung des Gesundheitszustandes (SoH) an. Dies würde Probleme erge-ben beim Konzept für Universalladegeräte. Die Benchmarq Lösung für 1-Draht-Systeme kann z.B. den Strom nicht direkt messen; sie kann jedoch aus der Kapazitätsänderung über die Zeit abgeleitet werden. Dazu kommt, dass der 1-Draht-Bus den Gesundheitszustand SoH nur dann messen kann, wenn das Gerät und die Batterie zueinander kompatibel sind.

7

1.1.2 Das Kommunikationsprotokoll I2C

I2C-Spezifikation (46Seiten) -> siehe Dokument: I2C-Spezifikation--39340011.pdf

Anfang der 80er Jahre entwickelte die Firma Philips das I2C-Busprotokoll. Ausschlaggebend war der steigende Einsatz von Mikroprozessoren in Konsumergeräten.

Gerade die Elektronikbranche ist darauf angewiesen, möglichst preiswert zu produzieren. Einsparungen waren somit dringend notwendig. Und genau hier setzt der I2C-Bus an. Bisher wurden teure CPU’s mit 8- oder 16-Bit breiten Datenbussen in Elektronikschaltungen einge-setzt, die nunmehr von einem seriellen aufwandsarmen I2C-Bus ersetzt werden (z. B. in Fernsehgerät). Durch das serielle Datenübertragungsverfahren fallen viele Leitungen weg, es werden weniger Anschlüsse nach außen geführt und die IC’s können somit kleiner produziert werden. Auch der Platzbedarf auf der Platine verringert sich stark. Zudem fallen weniger Platinenbohrungen und Lötpunkte an, was letztlich den Fertigungsaufwand reduziert und sich kosten senkend auswirkt.

I2C steht für “Inter Integrated Circuit”. Und genau dort wird er auch eingesetzt, als seriellen Bus zwischen Mikroprozessoren, IC’s und Ein-/Ausgabeeinheiten jeglicher Art, die in der Regel ihren Platz auf einer gemeinsamen Platine finden.

Die Daten werden mit Hilfe zweier Leitungen als serielle Information übertragen. Vorraus-setzung ist ferner ein gemeinsames Massepotential.

1.1.2.1 Konzept und Topologie

Die gesamte Kommunikation wird über nur zwei Leitungen abgewickelt. SCL (Serial Clock) trägt das notwendige Taktsignal und SDA (Serial Data) die Information. Im I2C-Bus erfolgt die Datenübertragung bitseriell und synchron, d. h. dass jedes Datenbit auf der SDA-Leitung mit dem Takt der SCL-Leitung synchronisiert wird. Beide Leitungen sind bidirektional aus-geführt, was es jedem IC ermöglicht, Daten zu verschicken oder anzufordern. Um zu ge-währleisten, dass die Information zum richtigen Empfänger gelangt, erhält jedes am Bus beteiligte IC eine eindeutige Adresse, mit der es identifiziert werden kann.

Das Konzept sieht eine Unterscheidung von Geräten (IC’s) in Master und Slave vor. Als Master wird ein Gerät bezeichnet, das einen Datentransfer initiiert und das notwendige Clock-Signal generiert. Geräte, die vom Master adressiert, also zum Transfer aufgefordert werden, bezeichnet man als Slave. Des weiteren wird noch eine Unterscheidung in Trans-mitter und Receiver gemacht. Der Transmitter sendet Daten und der Receiver empfängt sie. Anhand zweier Beispiele soll dieses nun verdeutlicht werden:

Mikroprozessor (MP) A sendet Daten an MP B

A (Master) adressiert B (Slave)

A (Master-Transmitter) sendet Daten an B (Slave-Receiver)

A beendet den Transfer

Mikroprozessor (MP) A fordert Daten von MP B an

A (Master) adressiert B (Slave)

A (Master-Receiver) empfängt Daten von B (Slave-Transmitter)

8

A beendet den Transfer

Prinzipiell ist jedes Gerät in der Lage, Master- bzw. Slave-Funktionen zu übernehmen, da die Zuordnung dynamisch erfolgt und keinen Regeln unterliegt.

Da beliebig viele IC’s am Bus einen Transfer initiieren dürfen, wird er auch als Multimaster-Bus bezeichnet. Es muss daher gewährleistet sein, dass nur ein Master zur selben Zeit aktiv ist. Um Problemen vorzubeugen, bietet das I2C-Protokoll mehrere Maßnahmen zur Vermei-dung von Kollisionen, auf die im weiteren Verlauf näher eingegangen werden soll.

9

Bild: Schaltplan eines I2C-Netzwerkes

1.1.2.2 Elektrische Eigenschaften

SCL (Serial Clock) und SDA (Serial Data) arbeiten bidirektional und werden durch Pullup-Widerstände auf High-Potential (logisch “1”) gezogen.

1.1.2.3 Transferraten

Low Speed Mode 10 kBit/s (inzwischen bedeutungslos)

Standard Mode 100 kBit/s

Fast Mode 400 kBit/s

High Speed Mode 3,4 MBit/s (1998 eingeführt; keine oder kaum IC’s, die diesen Standard unterstützen)

Beschränkung der maximalen Buskapazität auf 400 pF

kompatibel zu den gängigen Logikfamilien

1.1.2.4 Hardware-Grundlagen

Wie bereits beschrieben, besteht der I2C-Bus aus zwei aktiven Leitungen SDA und SCL so-wie der Masseleitung als Bezugspotential. Die Leitungen SDA und SCL sind über Pullup-Wi-derstände mit der Betriebsspannung verbunden.

Im Ruhezustand befinden sich also beide Leitungen auf High-Pegel (positive Logik). Die un-ten stehende Abbildung zeigt schematisch die Eingangs- und Ausgangskreise von Master- und Slave-Bausteinen. Bezeichnet wird die Gesamtheit dieser Chips als Wired-AND-Schal-tung. Im Ruhezustand sind die als Open-Collector ausgeführten Transistoren gesperrt und der Bus befindet sich auf High-Pegel.

10

Bild: Verschaltung von Master und Slave

Zur Ausgabe einer logischen 0 wird der Transistor leitend und zieht die entsprechende Lei-tung auf Masse. Im umgekehrten Fall bleibt die Basis des Transistors stromlos und die Lei-tung liegt, bedingt durch den Pullup-Widerstand auf logisch 1. Die Eingangskreise erkennen die Pegeländerungen auf den Busleitungen und können sie dann entsprechend auswerten.

Der High-Pegel ist definiert als NICHT-LOW-Pegel, d. h. es kann auch mit entsprechenden Bausteinen an einem System mit Spannung ungleich 5V (z.B. 3,3V) gearbeitet werden.

1.1.2.5 Datenübertragung

Um die Kompatibilität zu den Mikroprozessorsystemen zu wahren, werden die Daten im 8 Bit-Format übertragen. Die Anzahl der zu übertragenden Bytes in einem Transfer ist dank der SCL-Leitung, die das Clock-Signal zur Synchronisation trägt, unbegrenzt. Allerdings können einige Bausteine abhängig von ihrer Funktion nur eine bestimmte Anzahl Bytes sen-den und empfangen.

Das Byte wird mit dem höchstwertigen Bit MSB (Most Significant Bit) voran übermittelt. Wichtig ist, dass die Daten auf der SDA-Leitung stabil sein müssen, solange die SCL-Leitung High führt, ansonsten werden die Signale als Steuersignale interpretiert. Schreibende Geräte (Transmitter) müssen ihre Daten auf die Leitung legen, wenn SCL Low ist. So erreichen sie einen stabilen Zustand in der High-Phase. Nun können die lesenden Geräte die Daten bei SCL High aufnehmen.

Im Timing-Diagramm kann man gut die Übertragung eines gültigen Datenbits erkennen. Nun wird auch schon deutlich, wie simpel und dennoch effizient das I2C-Protokoll arbeitet. Ist SCL High, wird die Datenleitung SDA abgefragt und das stabil anliegende Signal als Information interpretiert.

Bild: Datenübertragung mit SDA und SCL

11

1.1.2.6 Steuersignale

Neben der „reinen“ Datenübertragung muss der gesamte Ablauf noch koordiniert werden. Damit nicht jedes anliegende Gerät zu Senden oder Empfangen beginnt, wird eine Identi-fikation der IC’s in Form einer Adresse den Daten vorangestellt. Des weiteren wird z. B. der Beginn und das Ende einer Übertragung markiert. Diese wichtigen Signale, die das ganze Verhalten auf den Leitungen bestimmen, werden zusammengefasst als Steuersignale be-zeichnet.

Wie unterscheidet man nun die Daten- von den Steuersignalen?

Einige lassen sich einfach an der Reihenfolge erkennen. Sinnigerweise muss erst die Ad-resse mitgeteilt werden und dann können die Daten folgen.

Es gibt noch eine andere Möglichkeit. Man verändert die Signale auf der Datenleitung. Um nun nicht mit den Regeln zu brechen, die unter anderem besagen, dass alles, was im High-Zustand von SCL als Pegel auf SDA liegt, ein Datenbit ist, hat man sich nun noch etwas Be-sonderes einfallen lassen. Bestimmte Steuersignale werden anhand ihrer Pegeländerung während der High-Phase der Clockleitung identifiziert. Von den Receivern wird nun nicht mehr der Pegel, sondern die Flanke gelesen.

Elementar sind die Start- und Stoppbedingung, die eine zu übermittelnde Sequenz kenn-zeichnen.

Das Startsignal wird durch eine fallende Flanke auf SDA herbeigeführt. Wichtig ist, dass während des Flankenwechsels SCL High führen muss. Die Stoppbedingung wird analog ko-diert, nur dass sie eine steigende Flanke darstellt. Start- und Stoppbedingung dürfen zu je-dem Zeitpunkt eines laufenden Transfers erzeugt werden. Beide Signale werden vom Master erzeugt. Nach jedem Start wird der Bus als Busy (belegt) angesehen. Nur der Master, der den Transfer initiiert hat, darf den Bus wieder auf Idle (frei) setzen.

Ist das Byte übermittelt, wird häufig ein optionales Handshaking vollzogen. Der Slave muss nun nach jedem empfangenen Byte ein Acknowledge an den Master senden. Antwortet der Slave auf dieses Bestätigungssignal mit einem High-Bit, gibt es damit zu erkennen, dass es an der Kommunikation nicht mehr teilnimmt bzw. diese beendet.

Will nun ein Gerät einen Slave auslesen, z. B. einen Speicher, muss nun der Master nach jedem Byte das Acknowledge senden. Ist die Kapazität des Speichers überschritten, kann der Master nach Empfangen des High-Pegels eine entsprechende Fehlerroutine starten. Es ist jedoch zu beachten, dass kein Master weitersenden darf, wenn er ein High-Acknowledge-Bit, auch als NACK (Not Acknowledge) bezeichnet, empfangen hat. Ansonsten gehen sämt-liche nachträglich gesendete Informationen verloren.

Auch wenn das Acknowledge-Bit ein Steuersignal ist, wird es praktisch wie ein Datenbit ge-handhabt, der Master erzeugt hierfür noch ein zusätzlichen neunten Taktimpuls auf SCL. Der einzige Unterschied ist, dass sich das Verhalten von Transmitter und Receiver kurzfristig umdreht, schließlich muss der Slave die folgende Übertragung mit einem Low quittieren, wenn die Übertragung fortgesetzt werden soll. Sendet der Slave dagegen ein High, gibt er das Ende der Kommunikation bekannt.

12

Bild: Steuersignale (Start, Stopp)

1.1.2.7 Adressierung

Will nun ein Master mit einem bestimmten Gerät über den Bus kommunizieren, muss als erstes eine Adresse übermittelt werden, die das IC eindeutig identifiziert. Die logische Kon-sequenz der Adresse ist, dass sie einmalig und dem Master bekannt sein muss.

Im Normalfall ist der Master das steuernde Gerät auf dem Bus, er allein kann einen Transfer initiieren. Herrschen mehrere Master über den Bus, ist eine Adressierung der einzelnen Master unabdingbar. Ansonsten ist eine vollständige Kommunikation zwischen den Mastern nicht möglich.

Die ursprüngliche Größe der Adresse beträgt 7 Bit, damit ließen sich im Höchstfall 128 IC’s im Bus einsetzen. Da allerdings noch einige Adressen reserviert sind und nicht jedes Gerät jede beliebige Adresse annehmen kann, wurde eine Erweiterung auf eine Länge von 10 Bit spezifiziert. Nun bleibt es dem Anwender überlassen, für welches Format er sich entscheidet, nur gibt der Markt zur Zeit kaum bis keine IC’s mit 10 Bit langen Adressen her.

Bild: Adressierung

Nach der gesendeten Startbedingung wird unmittelbar die Adresse übertragen. Im 7-Bit-Format, auf welches hier näher eingegangen werden soll, wird die Adresse in dem nächsten Byte angegeben. Da hier ein Bit übrig bleibt, das LSB, wird hier noch zusätzlich die Richtung des Transfers (R/W) verschlüsselt (Abb. 7). Eine logische “0” bedeutet “Schreiben”, eine “1” steht für den Lesebetrieb. Hier entscheidet sich die Funktion von Master und Slave, ob das Gerät nun als Receiver (Lesen) oder Transmitter (Schreiben) arbeitet.

Nachdem die Adresse übertragen wurde, wartet der Master auf eine Bestätigung. Hat ein Slave die 8 Bit empfangen, vergleicht er sie mit seiner eigenen Adresse. Bei Misserfolg ver-halten sie sich ruhig und warten auf die nächste Startbedingung. Stimmt die Adresse überein, meldet sich der Baustein mit einem Acknowledge und gibt zu erkennen, dass er bereit für die folgende Übertragung ist.

Die Art der Adresskodierung der Bausteine ist recht vielfältig. Es gibt zum einen reine Soft-warelösungen, die z. B. in Mikroprozessoren realisierbar sind. In der Regel stehen externe Pins zur Verfügung, die über Jumper gesetzt werden können. Um die Abmaße der Bausteine klein zu halten, werden häufig nur die niedrigsten drei Bits der Adresse nach außen zur Kon-

13

figuration geführt. Die restlichen vier Bits sind fest im Gehäuse verdrahtet und somit nicht zugänglich.

Eine wichtige Adresse ist die 10 Bit-Slave-Adresse, die wie der Name schon sagt, eine 10 Bit lange Adresse einleitet. Hier sind nur die höherwertigen fünf Bits reserviert, die restlichen enthalten schon die ersten zwei Bits der eigentlichen Adresse und natürlich das Richtungsbit.

Bild: Struktur der 10 Bit-Slave-Adresse

1.1.2.8 Transferarten

Prinzipiell gibt es drei verschiedene Arten des Transfers. Sie geben die Richtung der zu übertragenden Daten an. Um einen kleinen Überblick zu gewähren, sind die Betriebsarten noch einmal aufgezeichnet.

• Master sendet Daten an Slave

Die Richtung des Transfers bleibt erhalten, Daten werden vom Master auf den Bus ge-bracht. Der Slave antwortet nur, wenn überhaupt gewünscht, mit einem Acknowledge.

• Master fordert Daten vom Slave an

Hier wechselt die Transferrichtung. Der Slave sendet die angeforderten Daten und der Master quittiert gegebenenfalls mit einem Acknowledge. Beendet wird die Verbindung dennoch vom Master.

14

• Kombiniertes Format

Nach einer Repeated-Start-Bedingung erfolgt ein Richtungswechsel von anfangs schrei-bend auf lesend, aus Sicht des Masters.

1.1.3 Der Inter-IC Sound Bus Der I2S-Bus (Inter-IC Sound Bus) wurde von Philips entwickelt. Dieser Bus wurde speziell für die serielle Kommunikation zwischen ICs bei digitalen Audio Geräten entwickelt.

1.1.3.1 Einsatzgebiete Der I2S Bus wird verwendet bei DSPs, A/D Wandlern, D/A Wandlern und digitalen Filtern.

1.1.3.2 Aufbau

Der I2S Bus wird ausschliesslich zur Übertragung von Audio Daten verwendet. Der Bus be-steht aus drei Leitungen (Takt-, Daten- und Word Select-Leitung). Die Kommunikation erfolgt nur in eine Richtung, d.h. Audio Daten werden beispielsweise von einem DSP zu einem D/A Wandler gesendet und darüber eine Sprachausgabe realisiert. Ein anderes Beispiel ist, dass ein A/D Wandler die Signale eines Mikrofons in digitale Werte wandelt und danach über ei-nen I2S Bus die Daten an einen DSP schickt.

1.1.3.3 Eigenschaften 3 Leitungen (SCK, SD, WS)

keine Adressierung

keine bidirektionale Kommunikation

Hohe Datenraten

Bausteine mit unterschiedlichen Wortlängen kombinierbar

15

1.1.3.4 Transferraten Die Datentransferraten sind abhängig von der jeweiligen Anwendung: CD-Spieler: 44,1kHz * 16 bit => 1.4MBit/s DAT: 48kHz * 16 bit => 1,536MBit/s SACD: 96kHz * 24 bit => 4,608MBit/s

1.1.4 Ein I2C-Derivat, der SMBus Der System Management Bus (abgekürzt SMBus oder SMB) ist ein Zweileiterbus, der für die Baugruppenkommunikation entwickelt wurde (besonders für Halbleiter-ICs). Er hilft, den Zu-stand von Komponenten zu erkennen und Hardwareeinstellungen vorzunehmen.

17

Zum Stromsparen macht es etwa in tragbaren Computern (Notebook, PDA, Telefon) Sinn, nicht benötigte Erweiterungssteckplätze abzuschalten, das Display etwas abzudunkeln usw. Die Bitrate auf dem SMBus beträgt maximal 100 kbit/s. Am SMBus übernimmt jeweils ein Master die Bussteuerung (und damit vor allem die Takterzeugung), wenn er mit einem Slave kommuniziert. Kommunizieren zwei Master miteinander, so übernimmt der angesprochene Master zeitweise die Rolle eines Slaves.

Da der SMBus in der Regel nur zwei Leitungen (Takt- und Datenleitung) benötigt, kann er sehr platzsparend auf Platinen verlegt werden; ebenso benötigen die angeschlossenen Chips nur zwei Pins und passen dadurch in kleinere Gehäuse.

Da es Slaves gibt, die als steuerbare Schalter wirken, kann man damit Jumper (steckbare Verbindungsbrücken) auf Hauptplatinen ersetzen. Auf diese Weise lassen sich komplett jumperlose Hauptplatinen realisieren, was für den Benutzer häufig bequemer ist.

Ein SMBus-Gerät kann z. B. Herstellerinformationen zur Verfügung stellen, die Modell-/Seriennummer ausgeben, den Status des Energiesparmodus anzeigen, unterschiedliche Arten von Fehlern melden, Steuerparameter annehmen, einen Status zurückgeben oder eine Anzeige steuern. Da die Nutzung des SMBusses detaillierte Kenntnis der vorliegenden Hardware voraussetzt, ist er für den Benutzer in der Regel weder konfigurierbar noch zu-greifbar.

Der Bus wurde von Intel 1995 definiert. Der Standard beinhaltet den genauen zeitlichen Ab-lauf der Bussignale und die elektrischen Anschlußdaten. Der SMBus basiert auf dem I²C-Serienbusprotokoll von Philips. Die Spannungspegel auf dem Bus dürfen zwischen 3 V und 5 V liegen und sind damit zu denen vom I²C-Bus abwärtskompatibel.

Der SMBus hat optionales Signal (ALERT#), welches vom Slave genutzt werden kann, um einen Interrupt an den Controller zu senden.

Der SMBus wird von Linux und ab Windows 2000 unterstützt, jedoch nicht von Windows 98.

Für die Nutzung des SMBusses müssen von den Hauptplatinen-Herstellern Abgaben bezahlt werden.

21

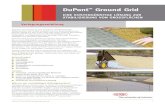

Bild: Quelle „Xicor Application Note AN124“

1.1.5 Die SPI-Schnittstelle

1.1.5.1 Funktionsprinzip

Das Serial Peripheral Interface (oder SPI) ist ein von Motorola entwickeltes Bus-System mit einem sehr lockeren Standard für einen synchronen seriellen Datenbus, mit dem digitale

22

Schaltkreise miteinander verbunden werden können. Ein ähnliches Bus-System existiert von National Semiconductor und nennt sich Microwire.

Die Vorteile von SPI liegen darin, dass es nur drei Leitungen benötigt und Taktfrequenzen bis in den MHz-Bereich zulässt. Dies macht es für Audio- und Messanwendungen interessant.

Der Bus besteht aus drei Leitungen, an denen alle Teilnehmer parallel angeschlossen sind:

SDO (Serial Data Out) bzw. MOSI (Master out Slave in)

SDI (Serial Data In) bzw. MISO (Master in Slave out)

SCKL (Serial Clock)

Darüberhinaus ist zum Ansteuern der Slaves jeweils eine eigene Leitung zwischen Master und Slave erforderlich:

SS/CS (Slave Select/Chip Select), auch STE (Slave Transmit Enable)

Bild: Schaltplan eines SPI-Netzwerkes

Es können theoretisch beliebig viele Teilnehmer an den Bus angeschlossen werden, wobei es immer exakt einen Master geben muss. Er ist derjenige, der das Clock-Signal an SCK erzeugt und festlegt, mit welchem Slave er kommunizieren will. Letzteres geschieht über die Leitung "Slave Select". Wird sie gegen Masse gezogen, wird der jeweilige Slave aktiv und "lauscht" an MOSI und legt seine Daten im Takt von SCK an MISO. Es wird somit ein Byte

23

vom Master zum Slave und ein anderes Byte von Slave zum Master transportiert. Ein Proto-koll hierzu wird von SPI nicht festgelegt. Auch ist nicht eindeutig festgelegt, ob die Daten bei der steigenden oder fallenden Flanke gültig sind und ob das MSB oder LSB zuerst gesendet wird. Mikrocontroller, die dieses Interface per Hardware anbieten, sind in diesen Punkten meist konfigurierbar und müssen an den angeschlossenen Schaltkreis angepasst werden.

1.1.5.2 Beispielimplementierung PIC16C65-Master und 82527-Slave

Die SPI-Schnittstelle ist eine Drei-Leiter-Schnittstelle, in welcher zwei Leiter als Datenleitung und ein Leiter als Takt-Vorgabe fungieren. Die Leiter sind im einzelnen mit MISO (Master In Slave Out), MOSI (Master Out Slave In) und SCLK (Shift Clock-Signal) bezeichnet.

Die MOSI-Leitung überträgt die Daten seriell vom Master zum Slave, die MISO-Leitung vom Slave zum Master jeweils mit dem MSB zuerst. Die SCLK-Leitung sorgt für die Taktvorgabe vom Master, hierbei werden bei jedem SCLK-Impuls Daten in beide Richtungen (MOSI, MISO) „geschoben“, wobei ein Datenbyte mit acht SCLK-Pulsen übertragen wird.

Das nachfolgende Blockschaltbild zeigt die Verbindung PIC und 82527 über ein SPI-Interface

Bild: SPI-Interface

Das SPI-Protokoll besteht aus einem Datensatz von bis zu 17 Bytes, welche seriell über das SPI-Interface übertragen werden. In Byte 1 des Protokolls wird die Adresse des 82527 über-tragen, auf welche ein Schreib-/ Lesezugriff erfolgen soll. Byte 2 des Protokolls ist das sog. „Serial Control Byte“, welches wie folgt aufgebaut ist:

Bild: Aufbau des Serial Control Byte

Bit 7 des Control Byte gibt die Richtung der SPI-Kommunikation vor, d.h. es wird ein Schreib- oder Lesezugriff definiert. Ist Bit 7 gesetzt, so erfolgt ein Schreibzugriff (vom Master gese-hen); ist Bit 7 nicht gesetzt, so erfolgt ein Lesezugriff (vom Master aus betrachtet). Die Bits 3 bis 0 geben die Anzahl der zu übertragenden/lesenden Bytes vor. Der Data Length Code darf niemals zu Null gesetzt sein.

Ab dem Byte 3 werden dann im Protokoll die Daten übertragen/gelesen.

1.1.6 Beispiel: Ansteuerung von digitalen Potis

- Application Note: A Primer on Digitally-Controlled Potentiometers (4 Seiten, 35kB)

- Bsp: Ansteuerung digitaler Potentiometer via SPI - 3-wire interface - Digital Poti XICOR x9110 (129kB)

24

- Bsp: Ansteuerung digitaler Potentiometer via I2C - 2-wire interface - Digital Poti XICOR x9408 (551kB)

1.1.7 Vergleich und Bewertung

Rei

chw

eite

Kos

ten

Ges

chw

indi

gkei

t

Verb

indu

ngst

yp

Rob

usth

eit

(U

nem

pfin

dlic

h ge

gen

EMV)

1-Draht-Bus

2-Draht-Bus z. B. I²C

3-Draht-Bus z. B. SPI

RS 485

25

1.2 Differentielle Kommunikationsverbindungen

1.2.1 Motivation für differentielle Kommunikationsverbindungen Nachteile von Signal-to-Ground Verbindungen

R’

R’ R’

R’ R’

R’

L’

L’ L’

L’ L’

L’

C’C’

Maßnahmen zur Gewinnung von sicheren Informationen

27

1.2.2 Guidelines for Proper Wiring of an RS-485 (TIA/EIA-485-A) Network The proper method of wiring an RS-485 network is described, with recommendations for twisted-pair cabling and correct location of termination resistors. Received waveforms are shown for examples of proper and improper cable termination. Network configurations are

28

shown for simple single-transmitter/multiple receiver through multiple transceiver to multi-branched circuits.

This application note is intended to provide basic guidelines for wiring an RS-485 network. The RS-485 specification (officially called TIA/EIA-485-A) does not specifically spell out how an RS-485 network should be wired. But it does give some guidelines. These guidelines and sound engineering practices are the basis of this note. The suggestions here, however, are by no means inclusive of all the different ways a network can be designed.

RS-485 transmits digital information between multiple locations. Data rates can be up to, and sometimes greater than, 10Mbps. RS-485 is designed to transmit this information over sig-nificant lengths, and 1000 meters are well within its capability. The distance and the data rate with which RS-485 can be successfully used depend a great deal on the wiring of the system.

Wire

RS-485 is designed to be a balanced system. Simply put, this means there are 2 wires, other than ground, that are used to transmit the signal.

Figure 1. A balanced system uses 2 wires, other than ground, to transmit data.

The system is called balanced, because the signal on one wire is ideally the exact opposite of the signal on the second wire. In other words, if one wire is transmitting a high, the other wire will be transmitting a low, and vice versa. See Figure 2.

29

Figure 2. The signals on the 2 wires of a balanced system are ideally opposite.

Although RS-485 can be successfully transmitted using multiple types of media, it should be used with wiring commonly called "twisted pair."

What Is Twisted Pair, and Why Is It Used?

As its name implies, a twisted pair is simply a pair of wires that are of equal length and are twisted together. Using an RS-485-compliant transmitter with twisted-pair wire reduces two major sources of problems for designers of high-speed long-distance networks: radiated EMI and received EMI.

Radiated EMI

As shown in Figure 3, high-frequency components are present whenever fast edges are used in transmitting information. These fast edges are necessary at the higher data rates that RS-485 is capable of transmitting.

Figure 3. Waveform of a 125kHz square wave and its FFT plot

The resultant high-frequency components of these fast edges coupled with long wires can have the effect of radiating EMI. A balanced system used with twisted-pair wire reduces this effect by trying to make the system an inefficient radiator. It works on a very simple principle. As the signals on the wires are equal but opposite, the radiated signals from each wire will also tend to be equal but opposite. This has the effect of canceling each other out, meaning no net radiated EMI. However, this is based on the assumption that the wires are exactly the same length and in exactly the same location. Because it is impossible to have two wires in the same location at the same time, the wires should be as close to each other as possible. Twisting the wires helps counteract any remaining EMI due to the finite distance between the two wires.

Received EMI

Received EMI is basically the same problem as radiated EMI but in reverse. The wiring used in an RS-485 system will also act as an antenna that receives unwanted signals. These un-wanted signals could distort the desired signals, which, if bad enough, can cause data errors. For the same reason that twisted-pair wire helps prevent radiated EMI, it will also help reduce the effects of received EMI. Because the two wires are close together and twisted, the noise received on one wire will tend to be the same as that received on the second wire. This type of noise is referred to as "common-mode noise." As RS-485 receivers are designed to look

30

for signals that are the opposite of each other, they can easily reject noise that is common to both.

Characteristic Impedance of Twisted-Pair Wire

Depending on the geometry of the cable and the materials used in the insulation, twisted-pair wire will have a "characteristic impedance" associated with it that is usually specified by its manufacturer. The RS-485 specification recommends, but does not specifically dictate, that this characteristic impedance be 120 ohms. Recommending this impedance is necessary to calculate worst-case loading and common-mode voltage ranges given in the RS-485 specifi-cation. The specification probably does not dictate this impedance in the interest of flexibility. If for some reason 120-ohm cable cannot be used, it is recommended that the worst-case loading (the number of transmitters and receivers that can be used) and worst-case common-mode voltage ranges be recalculated to make sure the system under design will work. Publication TSB89 has a section specifically devoted to such calculations.

Number of Twisted Pairs per Transmitter

Now that we have a feel for the type of wire needed, the question arises as to how many twisted pairs a transmitter can drive. The short answer is exactly one. Although it is possible for a transmitter to drive more than one twisted pair under certain circumstances, this is not the intent of the specification.

Termination Resistors

Because of the high frequencies and the distances involved, proper attention must be paid to transmission-line effects. However, a thorough discussion of transmission-line effects and proper termination techniques are well beyond the scope of this application note. With this in mind, terminations will be briefly discussed in their simplest form as they relate to RS-485.

A terminating resistor is simply a resistor that is placed at the extreme end or ends of a cable (Figure 4). The value of the terminating resistor is ideally the same value as the characteristic impedance of the cable.

Figure 4. Termination resistors should be the same value of the characteristic impedance of the twisted pair and should be placed at the far ends of the cable.

When the termination resistance isn't the same value as the characteristic impedance of the wiring, reflections will occur as the signal is traveling down the cable. This is governed by the equation (Rt-Zo)/(Zo+Rt), where Zo is the impedance of the cable and Rt is the value of the terminating resistor. Although some reflections are inevitable due to cable and resistor toler-ances, large enough mismatches can cause reflections big enough to bring about errors in the data. See Figure 5.

31

Figure 5. Using the circuit shown at the top, the waveform on the left was obtained with a MAX3485 driving a 120-ohm twisted pair terminated with 54 ohms. The waveform on the right was obtained with the cable terminated properly with 120 ohms.

With this in mind, it is important to match the terminating resistance and the characteristic impedance as closely as possible. The position of the terminating resistors is also very im-portant. Termination resistors should always be placed at the far ends of the cable.

As a general rule, termination resistors should be placed at both far ends of the cable. Al-though properly terminating both ends is absolutely critical for most system designs, it can be argued that in one special case only one termination resistor is needed. This case occurs in a system when there is a single transmitter and that single transmitter is located at the far end of the cable. In this case it is unnecessary to place a termination resistor at the end of the cable with the transmitter, because the signal is intended to always travel away from this end of the cable.

Maximum Number of Transmitters and Receivers on a Network

The simplest RS-485 network is comprised of a single transmitter and a single receiver. Al-though useful in a number of applications, RS-485 allows for greater flexibility by permitting multiple receivers and transmitters on a single twisted pair. The maximum allowed depends on how much each device loads down the system.

In an ideal world, all receivers and inactive transmitters will have infinite impedance and will not load the system down in any way. In the real world, however, this isn't the case. Every receiver attached to the network and all inactive transmitters will add an incremental load. To help the designer of an RS-485 network figure out just how many devices can be added to a network, a hypothetical unit called a "unit load" was created. All devices that are connected to an RS-485 network should be characterized in regard to multiples or fractions of unit loads. Two examples are the MAX3485, which is specified at 1 unit load, and the MAX 487, which is

32

specified at 1/4 of a unit load. The maximum number of unit loads allowed on a twisted pair, assuming a properly terminated cable with a characteristic impedance of 120 ohms or more, is 32. Using the examples given above, this means that up to 32 MAX3485s or up to 128 MAX487s can be placed on a single network.

Examples of Proper Networks

With the above information, we are ready to design some RS-485 networks. Here are a few examples.

One Transmitter, One Receiver

The simplest network is one transmitter and one receiver (Figure 6). In this example, a ter-mination resistor is shown at the transmitter end of the cable. Although unnecessary here, it is probably a good habit to design in both termination resistors. This allows the transmitter to be moved to locations other than the far end and permits additional transmitters to be added to the network should that become necessary.

Figure 6. A one-transmitter one-receiver RS-485 network

One Transmitter, Multiple Receivers

Figure 7 shows a one-transmitter multiple-receivers network. Here, it is important to keep the distances from the twisted pair to the receivers as short as possible.

Figure 7. A one-transmitter multiple-receivers RS-485 network

Two Transceivers

Figure 8 shows a two-transceivers network.

33

Figure 8. A two-transceivers RS-485 network

Multiple Transceivers

Figure 9 shows a multiple-transceivers network. As in the one-transmitter and multiple-re-ceivers example, it is important to keep the distances from the twisted pair to the receivers as short as possible.

Figure 9. A multiple-transceivers RS-485 network

Examples of Improper Networks

The diagrams below are examples of improperly configured systems. Each example shows the waveform obtained from the improperly designed network and compares it to a waveform from a properly designed system. The waveform is measured differentially at points A and B (A-B).

Unterminated Network

In this example, the ends of the twisted pair are unterminated. As the signal propagates down the wire, it encounters the open circuit at the end of the cable. This constitutes an impedance mismatch, bringing about reflections. In the case of an open circuit (as shown below), all of the energy is reflected back to the source, causing the waveform to become very distorted.

34

Figure 10. An unterminated RS-485 network (top) and its resultant waveform (left), compared with a waveform obtained from a correctly terminated network (right)

Wrong Termination Location

Figure 11 shows a termination resistor, but it is located in a position other than the far end of the cable. As the signal propagates down the cable, it encounters two impedance mis-matches. The first occurs at the termination resistor. Even though the resistor is matched to the characteristic impedance of the cable, there is still cable after the resistor. This extra ca-ble causes a mismatch and therefore reflections. The second mismatch is at the end of the unterminated cable, leading to further reflections.

35

Figure 11. An RS-485 network with the termination resistor placed at the wrong location (top) and its resultant waveform (left), compared to a properly terminated network (right)

Multiple Cables

In Figure 12, there are multiple problems with the layout. The first problem is that RS-485 drivers are designed to drive only a single, properly terminated twisted pair. Here, the trans-mitters are each driving four twisted pairs in parallel. This means that the required minimum logic levels cannot be guaranteed. In addition to the heavy loading, there is an impedance mismatch at the point where multiple cables are connected. Impedance mismatches again mean reflections and therefore signal distortions.

Figure 12. An RS-485 network that uses multiple twisted pairs incorrectly

Long Stubs

In Figure 13, the cable is properly terminated and the transmitter is driving only a single twisted pair; however, the connection point (stub) for the receiver is excessively long. A long stub causes a significant impedance mismatch and thus reflections. All stubs should be kept as short as possible.

36

Figure 13. An RS-485 network that has a 10-foot stub (top) and its resultant waveform (left), compared to a waveform obtained with a short stub

References

1. TIA/EIA-485-A Electrical Characteristics of Generators and Receivers for Use in Balanced Digital Multipoint Systems 2. TSB89 Application Guidelines for TIA/EIA-485-A

1.2.3 Struktur des RS485-Bussystems

Das RS485-Bussystems stellt eine Erweiterung des RS-422 Standards dar in dem Sinne, dass sich viele Sender den Zugriff auf die Datenleitung teilen. Momentan nicht aktive Sender schalten sich in einen hochohmigen Zustand, d. h. sind elektrisch quasi von der Busleitung getrennt.

Das vernetzungstechnische Problem besteht darin, den einzelnen Sendern im richtigen Mo-ment die Sendeerlaubnis zu erteilen, ohne dass Zugriffs-Überschneidungen auftreten.

Hierzu eignet sich besonders eine Master-Slave-Struktur des Netzwerks: ein Master-Rechner verteilt Sende-Berechtigungen an die verschiedenen Slaves. Alle anderen Slaves müssen ihren Sender abschalten und dürfen nur als Empfänger aktiv sein. Wenn der sendeberech-tigte Slave seine Nachricht gesendet hat, muss er ebenfalls wieder auf Empfang umschalten. Das Datenprotokolls muss so konstruiert sein, dass die Datenlänge einer jeden Nachricht von vornherein festgelegt ist oder zu Beginn der Nachricht gesendet wird. Daraus kann der

37

Master das Ende der Meldung ermitteln und die Sendeberechtigung an einen anderen Slave erteilen.

Ein RS-485 Netzwerk kann in einer 2-Draht Architektur (Half Duplex) oder in einer 4-Draht Architektur (Full Duplex) aufgebaut werden. Bei einer 2-Draht Architektur laufen die Sende-signale des Masters und der Slaves auf einem einzigen Adernpaar; die Datenrichtung wird permanent umschaltet (half duplex).

Bei einem kleinen Übertragungsfehler kann es passieren, dass der Master die Sendekon-trolle verliert und die Slaves nicht mehr erreichen kann. Bei einer 4-Draht Architektur hat der Master eine exklusive Sendeleitung, kann also jederzeit allen Slaves das Senden verbieten. Mit dem Preis eines höheren Verkabelungsaufwandes erkauft man sich ein erheblich stabile-res Netzwerk. Aus diesem Grunde verwenden viele Industrieunternehmen grundsätzlich nur 4-Draht Vernetzungen.

Die bisherigen Angaben über RS-485 beschreiben lediglich die physikalische Kommunika-tionsverbindung. Darin ist noch nicht definiert, welche Codes welche Bedeutung übertragen. Dies wird in konkreteren, teilweise firmenspezifischen Kommunikationsprotokollen festgelegt. Der Schwierigkeitsgrad für den Entwurf und die Programmierung eines solchen Netzwerk-protokolls sollte nicht unterschätzt werden.

1.2.4 Die hardwaretechnische Realisierung des RS485-Busses

Wichtigstes Bauteil beim Aufbau eines RS485-Bussystems ist ein Treiberbaustein, der von diversen Herstellern angeboten wird, z. B. MAX485, MAX487, MAX487E, LT485, etc..

Besonders geeignet ist z. B. "MAX487E" von Maxim, er besitzt sehr gute EMV-/ESD-Eigen-schaften und ermöglicht die Vernetzung von bis zu 255 Busteilnehmern. Per Definition wer-den mindestens 32 Teilnehmer gefordert.

Bild: Aufbau eines RS485-Netzwerkes

Ein RS485-Bus besteht aus einer Zweidrahtleitung, die an beiden Enden mit einem Wider-stand abgeschlossen ist. Dieser Widerstand dient zur Vermeidung von Leitungsreflektionen und liegt üblicherweise im Bereich von 120 Ohm. Die Länge des Busses darf - je nach Kabel und Baudrate - bis zu 4 km betragen.

38

Es darf immer nur ein Busteilnehmer senden. Die Empfänger entscheiden anhand der Diffe-renz zwischen den beiden Leitungen A und B, ob eine '1' oder eine '0' empfangen wird. Das Datenbit ergibt sich differentiell und nicht, wie etwa bei der RS232-Schnittstelle, anhand des Spannungswertes gegen Masse (GND). Das Differenzsignal macht den Bus sehr unemp-findlich gegen Störungen.

Manche Protokolle erfordern einen festen "Ruhepegel" für die Sendepausen. Dieser Ruhe-pegel wird im einfachsten Fall durch die beiden 560 Ohm Widerstände eingestellt.

Für den Busbetrieb selbst muss jedem Teilnehmer eine Adresse zugeordnet werden. Es ist wichtig, dass der sendende Busteilnehmer am Ende seiner "Nachricht" den Bus möglichst rasch wieder freigibt.

1.2.5 Bsp.: Der MAXIM Low-Power RS-485/RS-422 Transceiver

=> siehe Dokument RS485--MAX1487-MAX491.pdf

1.3 EMV/EMC-Schutzmaßnahmen

Beim Betrieb von Netzwerken sollte über Schutzmaßnahmen nachgedacht werden:

Elektrostatische Entladungen (ESD)

Transienten durch Blitzschläge in der näheren Umgebung

Störabstrahlungen

1.3.1 Elektrostatische Entladungen

Elektrostatische Entladungen sind sehr häufig und führen zu kurzen Impulsen mit be-trächtlichen Spannungen (bis ca. 30 kV (!)). Manche Bausteine verkraften ESD aufgrund ih-res Designs recht problemlos, wie z. B. der MAX487E, bei anderen ist gegebenenfalls ein zusätzlicher Schutz notwendig. Für ESD-Impulse gibt es diverse technische Modellierungen, z. B. IEC-801. Allen gemeinsam ist, dass sich ein Kondensator von ca. 100-200 pF, aufge-laden auf ca. 3-10kV über einen Widerstand von ca. 0-2kOhm auf den Probanden entlädt.

1.3.2 Transienten

Transienten besitzen mehr Energie als ESD-Impulse, erzeugen aber in der Regel eine nied-rigere Störspannung. Die Ursache für Transienten können z. B. Blitzschläge in der Umge-bung sein, wo der Transient durch Induktionen erzeugt wird.

1.3.3 Störabstrahlungen

Beim Auftreten von steilflankigen Signalen können Störabstrahlungen entstehen. Einige ICs begrenzen daher von sich aus die Anstiegsgeschwindigkeit (sog. Slew-Rate). Dadurch wird auch die Terminierung des Kabels unkritischer.

39

Als Ausgangsbasis für einen universellen Schutz gegen ESD und schwächere Transienten hat sich folgende Verschaltung bewährt:

Bild: Schutzbeschaltung durch Standard-Zenerdioden

Gut geeignet sind Standard-Zenerdioden. Diese sind billig und können normalerweise kurze Impulse von bis zu einigen Ampere problemlos verkraften. Durch die antiparallele Schaltung ist die Kapazität der Schutzbeschaltung minimal, Datenraten bis zu 250 kBd sind problemlos möglich. Falls nötig, können die Zenerdioden auch durch höher belastbare Überspannungs-Schutzdioden ersetzt werden.

Bild: RS485-Bausteine am Beispiel der BITBUS-Konfiguration

40

1.4 Anwendungsbeispiele aus der Praxis

1.4.1 Einsatzbeispiel RS485-Kommunikation mit Wechselrichtern

41

Bild: Verkabelung eines SB / SWR über RS485 an einen Sunny Boy Control; Quelle: Fa. SMA Dokumentnummer: SB-SWR-RS-NR-12:SD0105, Installation und Konfiguration der Schnittstellenmodule 485PB-NR

Bild: Verkabelung eines SB / SWR über RS485 an einen PC