CPU GRUNDLAGEN -2zai/HTL/SYT... · CPU GRUNDLAGEN -2 V20.01 H. Zainzinger, Februar 2020 Prozessor...

Transcript of CPU GRUNDLAGEN -2zai/HTL/SYT... · CPU GRUNDLAGEN -2 V20.01 H. Zainzinger, Februar 2020 Prozessor...

CPUGRUNDLAGEN - 2

V20.01

H. Zainzinger, Februar 2020

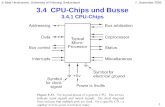

Prozessor-Busse (WH)

klassische CPU kommuniziert nach außen über Busse = logisch zusammengehörige Leitungen

Datenbus:• Zur Übertragung von Daten (z.B. mit Hauptspeicher)• Ein Datenzugriff überträgt ein Wort• Wortbreite = Anzahl der Datenleitungen

Adressbus:• Definiert Adresse der Speicherzelle, auf die zugegriffen wird• Busbreite bestimmt maximale Anzahl der Speicherzellen • Bestimmt wieviel Speicher der Prozessor (physisch, linear = direkt) adressieren kann.• n Leitungen ➔ 2n Speicherzellen können direkt physisch adressiert werden

Steuerbus:• Definiert Art der Peripherieanschlüsse des Prozessors• Diverse Leitungen zur Steuerung des Prozessorsystems • Bsp: Clock, Reset, Interrupt, ALE, …

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 2

von Neumann und Harvard Architektur

von Neumann CPU

ArbeitsspeicherDaten

Programm

Daten

Programm

Daten

Programm

Adressbus

Steuerbus

Datenbus

Bus für Daten und Code=Programme

von Neumann Architektur:• Daten und Code im selben Speicher• Gemeinsamer Bus für Daten und Code• Kein gleichzeitiger Zugriff auf Code und Daten

→ von Neumann Flaschenhals• geringere Betriebssicherheit (Daten können

Code überschreiben → Pufferüberlauf)• einfache Architektur (weniger Bus-Leitungen)

HarvardCPU

Datenspeicher

DatenAdressbus

Steuerbus

Datenbus

Programm- Speicher

Programm = Code

Steuerbus

Datenbus

Bus für Programmcode

Bus für Daten

Adressbus

Harvard Architektur:• Daten und Code in getrenntem Speicher• Getrennte Bus für Daten und Code• Gleichzeitiger Zugriff auf Code und Daten• unbenutzter Datenspeicher kann nicht als

Programmspeicher verwendet werden• keine Probleme durch Pufferüberlauf

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 3

Grundaufbau Prozessor

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 4

Detaillierterer Grundaufbau Prozessor (v. Neumann Arch.)

Adressbus Datenbus Steuerbus

Arbeitsregister 1

Arbeitsregister n

Status-Register (PSW, Flag)

Befehlszähler (PC, IP)

Stapelzeiger = Stackpointer

Befehlsregister

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 5

Datenpfad

Datenpfad = Die für die eigentlichen Berechnungen erforderlichen Bestandteile einer CPU.

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 6

Grundlegende Befehlstypen

Übernehmen Speicherwörter in Register

oder schreiben Registerinhalte in Speicherwörter

„Wort“ = Dateneinheit, die zwischen Speicher und Register bewegt wird

Bsp (8085):

LDA adr … Kopiert Inhalt der Speicherzelle adr in das Register A

STA adr … Kopiert Inhalt von Register A in die Speicherzelle adrMVI A,$08 … Schreibt den Wert $08 ins Register A (A = 8) „move immediately"

Register – Speicher Befehle

•Führt Operation mit einem oder mehreren Registern durch

•und speichert Ergebnis in einem Register ab.

•Bsp (8085):

•MOV L, A … Kopiert Inhalt von Register A nach L (L = A) „move“

•INR A … Increment A (A = A +1 oder A++)

•ADD B … Addiert Register B zu Register A hinzu (A = A + B oder A+=B)

Register-Register Befehle

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 7

Befehlskategorien

• Arithmetische Operationen: Führen Berechnungen durch (ADD, ADC, SUB, DIV, MUL, INC, DEC)

• Logische Operationen: Verknüpfen Bitfelder logisch miteinander (AND, OR, XOR, NOT)

• Bit-orientierte Operationen: Mit ihnen kann man einzelne Bits in einem Bitfeld genau ansprechen, auslesen, verschieben (Shift und Rotate) bzw. manipulieren

• Speicheroperationen: Übertragen Daten zwischen Prozessorregistern (MOV, MVI, XCHG), innerhalb eines Registers (BSWAP), sowie Registern und Speicher (LDA, STA)

• Vergleichsoperationen: Vergleich von Werten mittels <, >, sowie = (CMP, TEST)

• Steueroperationen: Verzweigungen, die den Ablauf des Programms beeinflussen (JC,JNZ,...)

• Datenkonvertierung: Diese Befehle wandeln Werte von einer Darstellung in eine andere um, u. U. auch mit Verlust. Zum Beispiel: ein Byte in ein Word, einen Long-Integer in ein Byte oder eine doppelte genaue Fließkommazahl in einen Integer. Bsp: DAA (BCD → Binär)

• Kombinierte Befehle aus Vergleichsoperationen, arithmetischen Operationen, und Datenaustausch (XADD, CMPXCHG)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 8

Shift - Operationen

= ≠

Multiplikation mit 2

Division durch 2mit Abrunden nach - im2er KomplementSAL

Java: <<

SARJava: >>

SHRJava: >>>

Division durch 2mit Abrunden ohne2er Komplement

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 9

Shift-OperationenBeispiel Java

public static void main(String[] args) {int shift1=1, shift2=1<<31; // shift2=1000000…00bfor(int j=0; j<32; j++){

int sh1 = shift1 << j; // Links Shiftint sh2 = shift2 >> j; // Rechts-shift mit 2er Komplementint sh3 = shift2 >>> j; // Rechts-Shift ohne 2er Komplem.System.out.println(String.format("%2d %11d %11d %11d",

j, sh1, sh2, sh3));}

}

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 10

Rotations- Operationen

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 11

LOAD/Store Architektur

LOAD / STORE Architektur

• = Register / Register Architektur

• Hauptspeicherzugriffe erfolgen ausschließlich mit speziellen Load (Lade-) und Store (Speicher-) Befehlen

• Ergebnisse werden in Register zwischengespeichert

• Viele Register erforderlich

• Meist RISC-Architektur (Reduced Instruction Set Computer)

• BSP: ARM Prozessoren (→ fast alle Smartphones)

Klassische Architektur

• Viele Maschinenbefehle erlauben Speicherzugriff

• ➔ Unterschiedliche Adressierungsmodi

• Meist CISC-Architektur (Complex Instruction Set Computer)

• Bsp: x86 und Nachfolger (Core i9, Ryzen)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 12

Adressierungsarten von Prozessoren

Die meisten Maschinenbefehl arbeiten mit Operanden (=womit wird etwas berechnet?)➔Ort des Operanden muss spezifiziert werden.Unterschiedliche Adressierungsmodi

• Implizite Adressierung (Implied Mode)• Unmittelbare Adressierung (Immediate Mode)• Registeradressierung (Register Mode)• Direkte Adressierung (Direct Mode)• Indirekte Registeradressierung (Register-Indirect Mode)• Indizierte Adressierung (Indexed Mode)• Indirekte Adressierung (Indirect Mode)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 13

Implizite Adressierung (Implied Mode)

• Implizite Adressierung (Implied Mode = Implicit Mode)• Kein Operand erforderlich -- Operand steckt bereits im OP-Code• Ist genau genommen gar keine Adressierung• Beispiele (8085)

• NOP → 00 (No Operation)• EI → FB (Enable Interrupt)

Operator

1 Byte

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 14

Register-Adressierung

• Register-Adressierung (Register Mode)• Operand steht in einem Register• Sonderfall der impliziten Adressierung• VT: sehr schnell

• z.B. (8085):• MOV A,D → 7A

• MOV …. Operator• A … Ziel-Register• D … Quell-Register

Register

A 0

B 0

C 0

D 7B

Register

A 7B

B 0

C 0

D 7B

MOV A,D

Operator

1 Byte

MOV A,B → 78MOV A,C → 79MOV A,D → 7AMOV A,E → 7B

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 15

Unmittelbare Adressierung

• Unmittelbare Adressierung (Immediate Mode)• Operand ist eine Konstante und wird im Speicher nach dem Maschinenbefehl

abgelegt (also nach dem OP-Code)• VT: Speicherzugriff nur auf benachbarte Zelle erforderlich (➔ relativ schnell)• NT: funktioniert nur mit Konstanten.• z.B. (8085): MVI A,02 → 3E02 oder: MVI B,0AFh → 06AF

Register

A 0

B 0

C 0

D 0

Register

A 02

B 0

C 0

D 0

MVI A,02

Operator

1 Byte

Operand = Konstante

1 Byte

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 16

Direkte Adressierung

• Direkte Adressierung (Direct Addressing Mode)• Operand wird aus Hauptspeicher gelesen• Im Befehl ist die Adresse des Operanden (=Speicherzelle) angegeben• NT: Zugriff immer auf die selbe Speicherstelle• NT: funktioniert nur mit globalen Variablen, deren Position im Speicher zum

Zeitpunkt der Übersetzung des Programmes (= Compile-Time) bekannt ist!• z.B. (8085): LDA 1240h→ 3A4012

→ Lade Inhalt der Speicherstelle 1240in das Register A

Memory Address

A 0 123E

123F

74 1240

1241

Memory Address

A 74 123E

123F

74 1240

1241

LDA 1240h

Operator Adresse des Operanden

1 Byte 2 Byte

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 17

Indirekte RegisterAdressierung

• Indirekte Registeradressierung (Register-Indirect Mode)• Quelle oder Ziel des Befehls befinden sich im Speicher• Adresse des Operanden wird aus Register (oder Registerpaar) ausgelesen (ist also

nicht fest codiert) ➔ Zeiger (Pointer)• VT: Befehl kann mit jedem Aufruf eine andere Speicherzelle dereferenzieren (=

über einen Zeiger auf eine Speicherzelle zugreifen)

z.B. (8085): MOV A, M

→ A … Ziel, →M = Speicherstelle, die durch Registerpaar H,L bestimmt wird

Memory Address

A 0 123E

47 123F

H 12 1240

L 3F 1241

Memory Address

A 47 123E

47 123F

H 12 1240

L 3F 1241

MOV A,M

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 18

Indizierte Adressierung

• Indizierte Adressierung (Indexed Mode)• Quelle oder Ziel des Befehls befinden sich im Speicher• Adresse des Operanden wird berechnet:• Adresse = Basisadresse + Index• Basisadresse ist eine Konstante • Index = Displacement = Offset• Index wird in einem Register gespeichert

Bsp: MOV A, 123Eh[R] (gibt es nicht beim 8085)• Kopiert den Wert von der Adresse (123E + R )ins Register A

MOV A, 123Eh[R]

Memory Address

A 0 41 123E

12 123F

R 2 74 1240

47 1241

Memory Address

A 74 41 123E

12 123F

R 2 74 1240

47 1241

+2

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 19

Indirekte Zeiger-Adressierung

• Indirekte Zeiger-Adressierung (Indirect Pointer-Mode)• Quelle oder Ziel des Befehls befinden sich im Speicher• Adresse des Operanden wird aus dem Speicher ausgelesen (ist also nicht fest

codiert) ➔ Zeiger (Pointer) = Wert, dessen Bedeutung eine Speicheradresse ist. VT: Befehl kann mit jedem Aufruf eine andere Speicherzelle dereferenzieren (= über einen Zeiger auf eine Speicherzelle zugreifen)

• NT: langsam (2 Speicherzugriffe erforderlich)Bsp: MOV A, [123Eh] (gibt es nicht beim 8085)• Kopiert den Wert von jener Adresse, die in Speicherstelle 123E steht

MOV A, [123Eh]

Memory Address

A 0 41 123E

12 123F

74 1240

47 1241

Memory Address

A 47 41 123E

12 123F

74 1240

47 1241

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 20

CISC Architektur

Ziel: komplexere Funktionen direkt durch den Prozessor mit einem Maschinenbefehl durchführen (Complex Instruction Set Computer)

CISC Eigenschaften

• Große Anzahl an Maschinenbefehlen (>100)

• Komplexe Operationen direkt in der Hardware

• Unterschiedliche Befehlslänge

• Unterschiedliche Ausführungszeiten für die einzelnen Befehle

• Große Anzahl unterschiedlicher Adressierungsarten

• Kleine Anzahl von Registern

• Die meisten Register werden für spezielle Aufgaben eingesetzt

• Unterstützung mehrerer Datentypen direkt durch die Hardware (z.BString-Befehle, Gleitkommabefehle)

• Interpretation der einzelnen Befehle (Microcodes) in der CPU durch Mikroprogramm

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 21

RISC Architektur

Ziel: wenige, dafür aber schnell auszuführende Befehle (Reduced Instruction Set Computer)

RISC Eigenschaften

• Wenige, schnell ausführbare Maschinenbefehlen (Low RISC-Prozessor: ca. 20 Befehle)

• Einfache Operationen, in einem Verarbeitungsschritt ausführbar

• Gleiche Ausführungszeiten für die einzelnen Befehle

• Schnelle Decodierung (Maschinenbefehle sind gleich lang)

• Geringe Anzahl unterschiedlicher Adressierungsarten (z.B. Load/Store Architektur)

• Große Anzahl von Registern, die meisten sind frei verwendbar → weniger Zugriffe auf (langsameren) Hauptspeicher erforderlich

• Feste Verdrahtung des Steuerwerks (kein Mikroprogramm)

• Einfacher im Entwurf → kleinerer Chip

• höhere Taktfrequenz oder geringerer Energieverbrauch möglich

• Mehr Platz für schnellen Speicher auf dem Chip (z.B.: viele Register, Cache)

• Ermöglicht einfaches Pipelining

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 22

Leistungsmerkmale CPU

Wortbreite der Arbeitsregister (incl. AKKU):• Definiert Wertebereich von Ganzzahlen und • Genauigkeit / Wertebereich von Gleitpunktzahlen

Wortbreite des Datenbusses• Wie viele Bits werden gleichzeitig aus Speicher übertragen• → Entscheidend für Geschwindigkeit des Datenaustausches

Wortbreite des Adressbusses:• →Max. Größe des physischen Arbeitsspeichers.

Taktfrequenz (Clock-rate):• Rechengeschwindigkeit der CPU• Meist Vielfaches der Mainboard-Taktfrequenz• „Overclocking“ führt zu Überhitzung

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 23

CPU-Funktionsblöcke Intel-Core

Quelle: c’t 2016, Heft 11

BPU: Branch Prediction Unit

µOP = Micro-Operation

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 24

CPU-Funktionsblöcke Intel-Core

Quelle: c’t 2016, Heft 11

Quelle: c’t 2016, Heft 11

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 25

Kontrollfragen zum Handout CPU- Prozessorfassungs-Grundlagen

1. Was sind die wesentlichen Aufgaben des CPU Front-Ends?2. Was bedeutet Pipelining?3. Wozu wird die BPU (Branch Prediction Unit) verwendet?4. Was sind Befehle in Zwei-Operanden-Form / Drei-Operanden Form?5. Was ist ein µOP?6. Was bedeutet Out-of-Order Execution (OoO)?7. Was ist In-Order-Technik?8. Wozu dient der Reorder Buffer (ROB)?9. Was ist der Loop-Stream-Detector?10. Was macht ein TLB (=Translation Lookaside Buffer)?11. Was sind: FPU, AGU? (→Wikipedia)12. Wozu gibt es deutlich mehr (versteckte) physische Register als sichtbare (logische)

Architektur-Register?13. Was macht die Allocate und Rename-Einheit?14. Warum gibt es zwei Level 1 Caches (L1-D-Cache und L1-I-Cache) → Um welche wesentliche

Rechnerarchitektur handelt es sich dabei?15. Was wird im (unified) Level 2 Cache gespeichert?16. Warum sind die Kontakte einer CPU vergoldet?17. Wozu befinden sich direkt auf der CPU-Unterseite Kondensatoren?18. Was ist ein Integrated Heat Spreader (IHS)?19. Warum haben moderne CPUs über 100 Anschlüsse (=Pins) für die Stromversorgung?20. Wie hoch ist die typische Versorgungsspannung eines modernen Prozessors? 21. Wie viel Strom fließt dabei (größenordnungsmäßig) bei Voll-Last?

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 26

Benchmarks

Benchmark = Referenzprogramme, zur Messung der Leistung eines Computers Dabei wird die Ausführungsdauer (von Start bis Ende) des Programms gemessen

MIPS • „Million Instructions Per Second“• Anzahl der Befehle, die eine CPU pro Sekunde ausführen kann

FLOPS• „Floating Point Operations Second“• Anzahl der Gleitpunktoperationen, die eine CPU pro Sekunde ausführen kann

SPEC-Benchmarak (Standard Performance Evaluation Corporation)• besteht aus mehrere Kategorien, z.B.:

• SPECint: Integer-Leistung• SPECfp: Gleitkomma-Leistung• SPECvirt: Leistung von Datacenter-Server für virtuelle Umgebungen• SPECviewperf: Grafik-Leistung• SPECpower: Energieeffizienz = Rechenleistung pro Watt

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 27

aus c’t 2015, Heft 27

Thermal Design Power (TDP)Wird CPU zu heiß ➔ Taktfrequenz wird gesenktTurbo-Boost: Bei Bedarf wird CPU kurzfristig höher getaktet (z.B. bei komplexen Berechnungen)

CMOS-Gleichung: 𝑷 ~ 𝑪𝑳 ∙ 𝑼𝟐 ∙ 𝒇CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 28

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 29

Befehlsstufen (Stages)

• Der durch den Befehlszähler adressierte Befehl wird aus dem Arbeitsspeicher geladen.

• Der Befehlszähler wird anschließend hochgezählt.

Befehlsbereitstellungsphase: Befehlscode laden (IF, Instruction Fetch)

• Der geladene Befehl wird dekodiert

• Notwendige Daten aus Arbeitsspeicher oder Registersatz laden (=Operanden abrufen)

Instruktion dekodieren und Laden der Daten (ID, Instruction Decoding)

• Der dekodierte Befehl wir ausgeführt und das Ergebnis gepuffert.

Befehl ausführen (EX, Execution)

• Ergebnis in den Arbeitsspeicher oder in den Registersatz zurückschreiben

Ergebnisse zurückschreiben (WB, Write Back)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 30

Pipeline

Befehlsverarbeitung ohne Pipelining

IF ID EX WBIF ID EX WB

IF ID EX WBIF ID EX WB

Befehl Nr.

1234

ZeitTaktzyklen

Unterschiedliche Phasen werden von verschiedenen Schaltkreisen innerhalb der CPU abgearbeitetIdee: Phasen der Befehlsabarbeitung parallelisieren (wie bei Fließband)Pipeline mit mehreren Stufen =Stages (hier: 4 Stages)

Befehlsverarbeitung mit Pipelining

Befehl Nr.

IF ID EX WBIF ID EX WB

IF ID EX WBIF ID EX WB

1234

ZeitTaktzyklen

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 31

Pipeline Hazards (=Konflikte)

Data Hazard = Datenabhängigkeit• Bei 2 aufeinanderfolgenden Befehlen kann passieren, dass der 2. Befehl das

Ergebnis des ersten Befehls benötigt.• Durch die parallele Befehlsausführung ist es möglich, dass der erste Befehl noch

nicht abgeschlossen ist.Vermeidung von Data Hazards:• Einfügen von Wartezyklen (NOP)• Befehlsreihenfolge ändern (s.u.)

Parallele Befehlsausführung: Problem

Befehl 2 verwendet A-Register, nochbevor Befehl 1 das Ergebnis ausgeführt hat

MVI A,5 ;Befehl 1

ADD B ;Befehl 2

Befehl Nr.

Zeit

MVI A,5

ADD B

IF ID EX WBIF ID EX WB

IF ID EX WBIF ID EX WB

1234

Befehl Nr.

Zeit

MVI A,5IF ID EX WBIF ID EX WB

IF ID EX WBIF ID EX WB

1234

NOP

NOP

ADD B

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 32

Pipeline Hazards (=Konflikte)

Control Hazard bei bedingten Sprungbefehlen• Bei Verzweigungen, die von Bedingungen abhängen• Zuerst muss Bedingung ausgewertet werden• Danach erst kann entschieden werden, an welche Stelle zu springen istVermeidung von Control Hazards:• Einfügen von Wartezyklen (NOP)• Spekulative Befehlsausführung = Out of Order Execution (OoO): CPU führt den

wahrscheinlichsten Folgebefehl aus. Wurde mit der falschen Befehlssequenz weitergerechnet → Pipeline muss geleert werden (=pipeline flush)

Parallele Befehlsausführung: Problem

Nachdem JC Ziel die IF Phase verlassen hat, kann nicht sofort der nächste Befehl (DCR A) geladen werden, weil ja noch nicht bekannt ist, ob gesprungen werden muss.

ADD B ;Befehl 1:A=A+B

JC Ziel ;Springe bei Übertrag

DCR A ;A=A-1

Ziel:

ADD B

JC Ziel

DCR A

Befehl Nr.

Zeit

IF ID EX WBIF ID EX WB

IF ID EX WBIF ID EX WB

1234

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 33

Piepline Stages in Intel Prozessoren

Quelle: https://en.wikipedia.org/wiki/List_of_Intel_CPU_microarchitectures

CPU Grundlagen, ZAI HTL Rennweg 2020-02

Year Micro-architecturePipelinestages

MHz [nm]

19788086 (8086, 8088) 2 530001982186 (80186, 80188) 2 253000

1982286 (80286) 3 2515001985386 (80386) 3 331500

1989486 (80486) 5 10010001993P5 (Pentium) 5 2008001995P6 (Pentium Pro) 14 450500

1997P5 (Pentium MMX) 6 2333501999P6 (Pentium III) 12 1400250

2000Pentium 4 (Willamette)20

2000180

2002Pentium 4 (Northwood, Gallatin)

3466130

2003Pentium M 10 23331302004Pentium 4 (Prescott) 31 3800902006Intel Core

12300065

2007Penryn 333345

2008Nehalem 20 3600

Bonnell 16 2100

Year Micro-architecturePipelinestages

MHz [nm]

2010Westmere 20 373032

2011Saltwell 16 2130Sandy Bridge

144000

2012Ivy Bridge 410022

2013Silvermont 17 2670Haswell

144400

2014Broadwell 3700

14

2015Airmont 17 2640

Skylake 14 4200

2016Goldmont 20 2600

Kaby Lake14

4500

2017Coffee Lake 5000Goldmont Plus 20 2800

2018Cannon Lake

14

320010Whiskey Lake 4800

14Amber Lake 4200

2019Cascade Lake 4400Comet Lake 4900

Ice Lake, Lakefield 14 410010

Seite 34

CPU mit mehreren Pipelines

Vorteil• mehrere Befehle können gleichzeitig ausgeführt werdenNachteil• Vervielfachung der Hardware (von S2 bis S5)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 35

Superskalare Architektur

• während Befehl 1 z.B. in der Gleitkommaeinheit ausgeführt wird (viele Taktzyklen), kann der nächste (kurze) Befehl 2 in der ALU berechnet werden

• Achtung: Falls Befehl 2 das Ergebnis von Befehl 1 benötigt ➔ Befehl 2 muss warten!

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 36

Beschleunigung von Prozessoren

•höhere Leistungsaufnahme (→kürzere Akkulaufzeit)

•höhere Wärmeentwicklung (→ schneller drehende = lautere Lüfter)→Man versucht, die Versorgungsspannung zu reduzieren (CMOS-Gleichung!)

Taktfrequenz erhöhen

•Pipeline Hazards machen Vorteil wieder zunichte

Größere Anzahl an Pipeline-Stufen / mehrere Pipelines / Superskalar-Architektur

•Software muss diese auch wirklich verwenden

Zusätzliche Funktionseinheiten einbauen

•größere Chipfläche → höhere Herstellungskosten

Mehrere CPUs (Kerne) auf dem selben Chip integrieren

•ein zweiter Thread (=paralleler Programmablauf) kann Hardware nutzen, die ein beschäftigter erster Thread gerade nicht benötigt

Multithreading

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 37

Beispiel: Zusätzliche Funktionseinheiten (Intel)

→ neue, leistungsfähige Maschinenbefehleaktuelle Beispiele:

AVX-2 (Advanced Vector Extensions)Zur besonders schnellen Verarbeitung von Gleitkomma- und Integer-Zahlen.• Nützlich für gleitkommaintensive Berechnung, vor allem im Multimedia-,

wissenschaftlichen oder Finanzberechnungen. • Neue Befehle der Form C = A + B (nicht destruktive Drei-Operanden-Form):

Rechenergebnis zerstört das Quellregister nicht → Verringert die Registerlast• Erhöhte Parallelität und Durchsatz von Gleitkommaberechnungen• Größere Registerbreite (z.B.: AVX-512 mit 512 bit Registerbreite in Xeon Phi Knights

Landing)

TSX (Transactional Synchronization Extensions)• Beschleunigt die Ausführung von Software auf Mehrkern-Prozessoren • Code wird parallel ausgeführt auch dann, wenn SW nicht in mehrere Prozesse oder

Threads aufgeteilt wurde• Anwendung besonders bei Datenbanksystemen• Wurde nachträglich auf mehreren Prozessoren per Microcode-Update deaktiviert• heißt bei AMD: Advanced Synchronization Facility (ASF)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 38

Multi-Core Prozessoren

Ein Chip mit einem CPU-Kern und mehreren Pipelines

Mehrere Befehle (aus mehreren Prozessen) können gleichzeitig ausgeführt werden, sofern diese nicht die selben Funktionseinheiten auf der CPU benötigen

Ein Chip mit zwei CPU-Kernen (und je einer Pipeline)

Mehrere Prozesse können gleichzeitig ausgeführt werden (ohne gegenseitige Beeinflussung)

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 39

Multi-Core Prozessoren

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Quelle: https://en.wikichip.org/wiki/amd/microarchitectures/zen_2

Quelle: https://www.microway.com/hpc-tech-tips/amd-epyc-rome-cpu-review/

Bsp. Serverprozessor AMD EPYC 7702 ES• 1 I/O Die:

• 128 Lanes PCIe V4 • Kanal DDR V4)

• 8 Compute Dies = CPU Chiplets• Compute Die-Size 10.32 mm × 7.34 mm• Wieviele Kerne hat ein Compute Die?

Seite 40

Quelle: c't 2018/10 Seite 108

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 41

Multithreading

Mehrere Prozesse (oder Threads) können (scheinbar) gleichzeitig ausgeführt werden!Bsp ohne Multithreading: 3 Threads (a), (b) (c).

Befehl A1 benötigt 1 Taktzyklus (auch A3, A4, A6-A8, B3-B8, C1-C3, C5, C7, C8)Befehl A2 greift auf Speicher zu, muss warten und benötigt 3 Zyklen

(auch A5, B1, B2, C4, C6)

→ Multithreading:Befehle von mehreren Threads abwechselnd hintereinander auf 1 Kern ausführen:

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 42

Multithreaded Programming

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 43

Hyperthreading (Intel)Simultaneous Multithreading (AMD)

Hyperthreading (HT) = Simultaneous Multithreading (SMT):Multithreading bei Intel Prozessoren („Gleichzeitig“ mehrere Threads ausführen)

Für Betriebssystem sieht ein Core-i7-Chip mit Hyperthreading wie ein Dual-Prozessor aus, in dem beide CPUs einen allgemeinen Cache und den Hauptspeicher gemeinsam nutzen.

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 44

Info: Typennummern von Prozessoren

Quelle: c't 2018/10 Seite 103

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 45

Benchmarksaus c’t 2015, Heft 27

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 46

aus c’t 2015, Heft 27

Was bedeuten Intel Prozessornummer? Siehe: https://www.intel.de/content/www/de/de/processors/processor-numbers.htmlBsp: Intel Core i7-4600U

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 47

Prozessorarchitektur Intel Core-i7

jeder Kern (hier: 4) hat privaten L1 Daten und L1 Befehls-cache und L2 Cache

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 48

Prozessorarchitektur Intel Core-i9

CPU Grundlagen, ZAI HTL Rennweg 2020-02

https://www.anandtech.com/show/11550/the-intel-skylakex-review-core-i9-7900x-i7-7820x-and-i7-7800x-tested/5

Seite 49

Prozessorarchitektur AMD Ryzen Threadripper

Abbildungen: c’t 2017, Heft 18

Ryzen Threadripper:• bis zu 4 aktive Dies• bis zu 32 Kerne• 64 Threads (SMT)• 64 PCI-Express-Lanes• 4 DDR4- Speicherkanäle

Als variablen Turbo gibt es obendrein die Funktion Extended Frequency Range (XFR): Hat der verwendete Kühler noch Reserven, dürfen der Threadripper 1950X und 1920X in 25-MHz-Schritten bis zu 200 MHz über die genannten Werte hinausgehen.

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 50

Prozessorarchitektur AMD Ryzen Threadripper

Quelle: c’t 2019, Heft 16

Quelle: c’t 2017, Heft 18

1950X

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 51

Fachartikel: "Transistor-Wettrüsten bei Prozessoren"

CPU Grundlagen, ZAI HTL Rennweg 2020-02

Satte 35 Milliarden Transistoren quetscht

Xilinx auf das Silizium-Die des kommenden FPGA Virtex UltraScale+ VU19P. Das ist der

Rekordwert für einen „normalen“ Prozessor,

also einen Logikchip.

Bei DRAM lassen sich Transistoren zwar noch dichter packen, aber die Silizium-Dies sind

kleiner, sonst würden sie zu teuer. Mit Die-

Stapeln und Chiplets bekommt man jedoch viel mehr Transistoren in ein Bauelement –

und dann gibt es noch Spezialkonstruktionen,

die komplette Wafer nutzen, etwa im Heidelberger BrainScaleS-Computer oder

beim KI-Monster von Cerebras mit 400.000

Rechenkernen aus 1,2 Billionen Transistoren. […]

Zitiert aus c't Heft 20/2019 Seite 28

Seite 52

Fachartikel: AMD setzt auf Chiplets und 7 Nanometer

CPU Grundlagen, ZAI HTL Rennweg 2020-02

[…] Anders als in den letzten Jahren kann AMD einen

Fertigungsvorteil in die Waagschale werfen. Denn bei Intel

halten die Schwierigkeiten mit der eigentlich schon vor

Jahren fest eingeplanten 10-nm-Herstellung an, während die

von AMD beauftragte Chipschmiede TSMC bereits

Schaltkreise mit 7 nm feinen Strukturen liefert. Die sollen

doppelt so viele Transistoren pro Quadratmillimeter packen

wie die hauseigene 14-nm-Technik. AMD nutzt diesen Vorteil

bei Zen 2 auf geschickte Weise und dekonstruiert den

Prozessor namens „Rome“. Denn nur die eigentlichen

Rechenkerne samt Cache und Infinity-Fabric-(IF-)Link zur

Anbindung werden in 7 nm bei TSMC hergestellt, ein

Compute-Cache-Die (CCD) gewissermaßen. Bis zu acht

dieser kleinen Chip-chen (Chiplets) mit je acht CPU-Kernen

sind via IF-Link mit einem zentralen I/O-Die verbunden, das

Fertigungspartner Globalfoundries in 14 nm herstellt. Der

beherbergt außer den acht Speichercontrollern und den PCI-

Express Root-Hubs, die erstmals in der x86-Welt auch PCIe

4.0 beherrschen, auch den IF-Switch. Über ihn

kommunizieren die Rechenkerne miteinander. AMD schlägt

zwei Fliegen mit einer Klappe, da im I/O-Die auch die

analogen Schaltungen sitzen, die schlechter als reine Logik

oder Cache von der kleineren Fertigungsgeometrie

profitieren würden. Zum genauen Aufbau schweigt sich der

Hersteller noch aus.

Auf Nachfrage gab AMD immerhin zu Protokoll, dass

Programmierer nun mit deterministischen Latenzen beim

Speicherzugriff rechnen können. […]

Nicht nur Prozessoren, auch Grafikchips hat AMD

überarbeitet und lässt diese in 7-nm-Technik fertigen. Sie

sollen als Radeon Instinct MI50 und MI60,

Beschleunigerkarten für Machine Learning, noch 2018 auf

den Markt kommen. Die 13,2 Milliarden Transistoren quetscht

AMD auf 331 Quadratmillimeter – zum Vergleich: Nvidias

Tesla V100 ist 146 Prozent größer. Dank der kleineren

Chipfläche kann AMD Nvidia vor allem preislich unter Druck

setzen.

Die neue AMD-GPU basiert auf der Vega-GPU, hat aber einige

Neuerungen bekommen. Statt zwei arbeiten nun vier

Speichercontroller, was außer verdoppelter Transferrate von

bis zu 1 TByte/s auch die zweifache Speichermenge von 32

GByte ermöglicht. Zudem sind nun sämtliche Caches und

Register ECC-geschützt. Die 4096 Shader-Recheneinheiten

schaffen bei doppelter Gleitkommagenauigkeit nun 50

Prozent des regulären FP32-Durchsatzes und toppen mit 7,4

TFlops Nvidias PCIe-Version der Tesla V100 knapp. Fürs

Machine Learning hat AMD die Shader-Einheiten umgebaut,

sodass sie nun auch INT8 (59 Tera-Ops/s) und INT4 (118

TOPS) beherrschen. […]

Zitiert aus c't Heft 25/2018 Seite 22 bzwhttps://www.heise.de/select/ct/2018/25/1544258829095894

Seite 53

Strukturgrößen = kleinste Struktur auf Halbleiterchip. Derzeit: 10 nm (z.B. Samsung S8, Apple iPhone 8) → Haar ist 5000x so dickab Juli 2019: 7nm in CPU (AMD) erwartet → deutlich weniger Energieverbrauch!

Quelle: Frank Klemm in der Wikipedia auf Deutsch, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=36936777

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 54

Harddisks: Preis/Leistungsverhältnis verbessert jährlich um ca. 50%

Speicherchips (DRAM)→ Ca. alle 3 Jahre eine neue Generation an Speicherchips mit 4-facher Speicherkapazität→ Anzahl der Transistoren verdoppelt sich ungefähr alle 1,5 Jahre:

Mooresches „Gesetz“→ über viele Jahre verdoppelte sich im gleichen Zeitraum die Komplexität der

Computerchips bei gleichbleibenden Kosten (Gordon Moore 1965)

Anzahl der Transistoren bei Speicherchips (Quelle: Tanenbaum/Austin: Rechnerarchitekturen, Pearson 2014)

Faktor 1024 = 210

→ 10 mal verdoppelt

ca. 15 Jahre

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 55

Strukturgrößen

Quelle: https://medium.com/stoned-immaculate/the-120-years-of-moores-law-fccddc16dc76

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 56

Wachstumsspirale

technologischer Fortschritt (z.B. mehr Transistoren pro Chip)

bessere Produkte zu niedrigeren Preisen

neue Anwendungen

neue Märkte,neue Firmen

größerer Wettbewerb

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 57

Nathans 1. Gesetz: Software ist wie ein ideales Gas und füllt jeden „Container“ ausProgramme werden immer komplexer und "ressourcenhungriger" programmiert. Egal wie viele Ressourcen vorhanden sind, die Programme benutzen alle vorhandenen Ressourcen (Hauptspeicher, Festplattenspeicher, CPU Performance, …)

Nathans 2. Gesetz: Software wächst, bis sie durch das Mooresche Gesetz begrenzt wird→ zwingt jeden Prozessor in die Knie, bevor neues Modell verfügbar ist

Nathans 3. Gesetz: Durch Software-Wachstum wird Mooresches Gesetz „ermöglicht“→ Software zu ressourcenhungrig (zu groß / zu langsam)→ Bedarf nach leistungsfähigeren Chips (bei gleichem Preis)

Nathans 4. Gesetz: SW ist nur durch menschliche Ambitionen und Erwartungen limitiert

Nathans Software „Gesetze“→ Nathan Myhrvold, 1997 CTO von Microsoft

CPU Grundlagen, ZAI HTL Rennweg 2020-02 Seite 58