Documentation

Transcript of Documentation

Gameboy R⃝

wiederbeschreibbare Spielekassette

Solvalou

01. Oktober 2010

Zusammenfassung

Ziel des Projekts ist die Erstellung einer wiederbeschreibbaren, uni-versellen Spielekasette fur den NintendoR⃝ Gameboy R⃝.Der Programmcode wird auf eine SD-Karte geladen, welcher anschlie-ßend mittels einem Mikrocontroller ausgelesen und in den Speicherdes Gameboys R⃝ geschrieben wird.Diese Dokumentation enthalt eine genaue Beschreibung der verwen-deten Komponenten, der Schaltung selbst, dem FAT16-Dateisystem,der Hardware von SD-Karten und dem Programmcode des Mikrocon-trollers. Außerdem sind weitere Informationen uber die Hardware undSoftware-Programmierung des GameboyR⃝ vorhanden.

1

Inhaltsverzeichnis

1 SD-Karte 31.1 Anschlusse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31.2 SPI-Schnittstelle . . . . . . . . . . . . . . . . . . . . . . . . . 41.3 SPI am µC . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.3.1 Konfigurationsregister SPCR . . . . . . . . . . . . . . . 41.3.1.1 Ubertragungsmodi . . . . . . . . . . . . . . . 51.3.1.2 Taktrateneinstellung . . . . . . . . . . . . . . 6

1.3.2 Statusregister SPSR . . . . . . . . . . . . . . . . . . . 61.3.3 Datenregister SPDR . . . . . . . . . . . . . . . . . . . 7

1.3.3.1 Senden und Lesen von Bytes . . . . . . . . . 71.4 SD-Kommandos . . . . . . . . . . . . . . . . . . . . . . . . . . 71.5 SD-Antwort . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81.6 Initialisieren der SD-Karte . . . . . . . . . . . . . . . . . . . . 8

1.6.1 Startverzogerung . . . . . . . . . . . . . . . . . . . . . 81.6.2 Aktivieren des Idle-Modus . . . . . . . . . . . . . . . . 81.6.3 Aktivieren des Betriebsmodus . . . . . . . . . . . . . . 9

2 USART 102.1 Die Register des USART . . . . . . . . . . . . . . . . . . . . . 10

2.1.1 Kontroll- und Statusregister UCSRA . . . . . . . . . . 102.1.2 Kontroll- und Statusregister UCSRB . . . . . . . . . . 11

2

1 SD-Karte

Die Formatierung der Karten erfolgt im FAT16-Format, die maximale Anzahlan Partitionen betragt vier. Es konnen maximal 4GB Daten indiziert werden.Die interne Einteilung findet in 512Byte Sektoren statt. Die Karte wird imSPI-Modus (serial peripheral interface) betrieben, daher werden nur siebenstatt neun Anschlussen verwendet.

1.1 Anschlusse

SS slave selectMISO master in, slave outMOSI master out, slave inSCK serial clockVCC voltage of the common collectorVSS GNDDAT1 & DAT2 not connected in SPI-mode

SS Mit diesem Anschluss wird der anzusteuernde”Slave“ ausgewahlt, in

diesem Fall die SD-Karte selbst. der verwendete Master ist der C.

MISO Uber diese Leitung sendet der Slave Daten an den Master.

MOSI Uber diese Leitung sendet der Master Daten an den Slave.

SCK Diese Leitung gibt den Takt der Verarbeitung vor, sie ist an den Masterund an den Slave angeschlossen. Ein Slave kann erst dann Daten sendenwenn SS auf LOW gezogen wurde und ein Impuls uber SCK erfolgt ist.

3

1.2 SPI-Schnittstelle

serial peripheral interface

Ein aus drei Leitungen bestehendes Bus-System, welches von Motorola ent-wickelt wurde. Es verbindet mehrere Komponanten nach dem Master-Slave-Prinzip. Unterstutzt werden Taktfrequenzen bis in den MHz-Bereich. VieleµC bieten eine integrierte SPI-Anbindung, sie ist allerdings auch uber diestandard I/O-Anschlusse erzeugbar. Hierbei muss das Protokoll mittels Pro-grammcode nachgebildet werden.Ein einzelner Master kann mehrere Slaves ansprechen, allerdings nicht gleich-zeitig. Die Auswahl findet uber den SS-Anschluss statt, dieser wird beimanzusprechenden Gerat auf LOW-Pegel gesetzt. Nun generiert der Mastereinen Impuls auf der SCK-Leitung, mit jedem einzelnen Impuls wird auf derMISO-Leitung ein Bit vom Slave zum Master und gleichzeitig auf der MISO-Leitung ein Bit vom Master zum Slave ubertragen. Nach abgeschlossenerUbertragung wird die Impulserzeugung auf der SCK-Leitung eingestellt undder Anschluss des Slaves wieder auf den HIGH-Pegel gesetzt.Es liegt also, wie im vorhergehenden Absatz bereits beschrieben, eine bidi-rektionale (in beide Richtungen) Ubertragung vor. Meist wird allerdings nureine Richtung genutzt, es wird also entweder gelesen oder geschrieben. Hateine der Komponenten (Master oder Slave) keine sinnvollen Informationendie er weitergeben kann, setzt er seine Ausgangsleitung auf HIGH. Es wirdalso nur der logische Zustand ’1’ ubertragen.

1.3 SPI am µC

Alle Angaben und Grafiken beziehen sich auf einen AtMega-Mikrocontrollerder Firma Atmel. Dieser besitzt drei Register, welche eine große Rolle fur dieSPI-Ubertragung spielen.

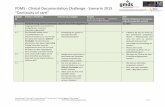

1.3.1 Konfigurationsregister SPCR

In diesem Register werden die Parameter der Ubertragung eingestellt, es hatdie Große von 8bit und beinhaltet die selbe Anzahl an Flags.

Abbildung 1: SPCR-Register

4

SPIE (SPI Interrupt Enable)Zeigt den Status des SPI-Interrups an

0 = inaktiv

1 = aktiv

SPE (SPI Enable)Zeigt den Status des SPI-Modus an

0 = inaktiv

1 = aktiv

DORD (Data Order)Zeigt an welches Bit aus dem Datenregister zuerst gesendet wird

0 = hochstwertiges BIT (MSB)

1 = niederwertiges Bit (LSB)

MSTR (Master/Slave Select)Zeigt an ob der µC als Master oder als Slave fungiert

CPOL (Clock Polarity)Gibt die Polaritat des SCK-Signals im Ruhezustand an

CPHA (Clock Phase)Gibt die Phasenlage des SCK-Signals im Ruhezustand an

SPR0/SPR1 (SPI Clock Rate Select)Gibt die Taktrate des SCK-Signals in Abhangigkeit des µC-Taktes an.Hier wird zusatzlich zu den SPR-Flags des Konfigurationsregisters dasSPI2X-Flag des Statusregisters verwendet.

1.3.1.1 Ubertragungsmodi

Das SPI-Protokoll ist nicht festgelegt. Es gibt vier Auswahlmoglichkeiten,welche Polaritat und Phase des Taktes bestimmen. Die Einstellungen wer-den im auszufuhrden Programm des µC gesetzt.

CPOL (clock polarity)

0: LOW ist der Ruhetakt, ein Wechsel auf HIGH bezeichnet die stei-gende Taktflanke

5

Mode CPOL CPHA0 0 01 0 12 1 03 1 1

Abbildung 2: Einstellung der Polaritat und Phase des Taktes

1: HIGH ist der Ruhetakt, ein Wechsel auf LOW bezeichnet die stei-gende Taktflanke

CPHA (clock phase)

0: Einlesen der Daten bei steigender Taktflanke, Ausgabe bei fallender

1: Ausgabe der Daten bei steigender Taktflanke, Einlesen bei fallender

1.3.1.2 Taktrateneinstellung

Durch das Setzen der entsprechenden Flags in den Registern wird die Ubert-ragungsrate der SPI-Schnittstelle festgelegt. Genauer gesagt wird hiermit derWert des Dividers verandert, dieser wiederum teilt die Taktrate des µC. Dieresultierende Rate wird der Schnittstelle zur Verfugung gestellt.

SPR1 SPR0 SPI2X Taktrate0 0 0 CPU/40 0 1 CPU/20 1 0 CPU/160 1 1 CPU/81 0 0 CPU/641 0 1 CPU/321 1 0 CPU/1281 1 1 CPU/64

Abbildung 3: Einstellung der Taktrate

1.3.2 Statusregister SPSR

Auch hierbei handelt es sich um ein 8bit-Register. Die Flags 6&7 sind ReadOnly, d.h. es konnen keineWerte beeinflusst werden. Flag 0 ist eine Erganzungdes Kontrollregisters, seine Funktion wurde in der Beschreibung des SPCRerklart.

6

Abbildung 4: Statusregister SPSR

SPIF SPI Interrupt FlagZeigt eine Interruptanforderung an

WCOL Write CollisionZeigt das Auftreten einer Schreibkollision an

1.3.3 Datenregister SPDR

Ein 8bit Register, welches die zu sendenden bzw. gelesenen Daten enthalt.

1.3.3.1 Senden und Lesen von Bytes

Um einen Datentransfer zu beginnen schreibt man das zu sendende Bytein das SPI Data Register (SPDR). Nach abgeschlossener Ubertragung wirddas SPI Interrupt Flag (SPIF) im SPI Status Register (SPSR) gesetzt. Dader Datenaustausch bidirektional stattfindet kann nun im SPDR das empfan-gene Byte ausgelesen werden. Das SPIF wird daraufhin automatisch zuruck-gesetzt.Soll nur gelesen werden sendet man einfach ein 0xFF an den angeschlosse-nen Slave. Eine SD-Karte macht das gleiche wenn sie nur Daten empfangt.Wahrend einer Transaktion muss der SS-Anschluss des Slaves auf dem LOW-Pegel gehalten werden.

1.4 SD-Kommandos

Byte Bedeutung1 Beginnt mit den Bits

”01“ gefolgt vom Kommado-Index

2-5 Paramter6 CRC7, letztes Bit stets ’1’

Abbildung 5: Aufbau eines Kommandos

Ein Kommando an die SD-Karte besteht stets aus 6Bytes. Das erste Bytegibt den Index des Kommandos an, seine erten beiden Bits besitzen immerden Wert

”01“. Somit ist die Gesamtzahl der Kommandos 26, also 64. Die

Abkurzung hat folgendes Format: CMD¡index¿.

7

Die nachfolgenden vier Bytes enthalten Paramter fur das vorher ubertrageneKommando. Besteht ein Paramter aus mehreren Bytes wird das hoherwertigezuerst ubertragen.Das letzte Byte enthalt die CRC-Prufsumme, diese wird im SPI-Modus nor-malerweise ignoriert. Nur bei den Kommandos CMD0 und CMD08 muss siestimmen. CMD0 dient dem Initialisiern von SD-Karten und CMD08 demInitialisieren von SDHC-Karten.

1.5 SD-Antwort

Bit Bedeutung0 stets 01 parameter error2 address error3 erase sequence error4 communication crc error5 illegal command6 erase reset7 in idle state

Abbildung 6: Antwort auf das Senden eines Kommandos

Nach dem Senden des Kommandos empfangt man eine Antwort der SD-Karte. Sollte die KArte keine wichtigen Informationen zur Weitergabe haben,sendet sie den Wert 0xFF. Es muss also so lange von der SPI-Schnittstellegelesen werden bis sich die empfangene Antwort von diesem Wert unterschei-det.Das Antwortformat wird

”R1“ genannt. Jedes Bit des Bytes steht fur einen

Fehler oder Status. Wird also 0x00 oder 0x01 empfangen, fand eine fehlerfreieUbertragung statt.

1.6 Initialisieren der SD-Karte

1.6.1 Startverzogerung

Nach dem Anlegen der Spannung sollte mindestens eine Sekunde gewartetwerden bevor der erste Zugriff auf die SD-Karte erfolgt. Anschließend wirdSS auf LOW und MOSI auf 0xFF gesetzt, dieser Zustand sollte nun furmindestens 74 Taktsignale eingehalten werden bevor das erste Kommandoverschickt wird.

8

1.6.2 Aktivieren des Idle-Modus

Das erste Kommando versetzt die SD-Karte in den Idle-Modus. Hierbei wirddas Kommando CMD0 (GO IDLE STATE) verschickt. Im Gegensatz zu an-deren Befehlen wist hier die CRC-Prufsumme von Bedeutung. Da das Kom-mando keine Parameter besitzt, werde diese mit logischen Nullen gefullt.Die SD-Karte uberpruft nach Empfangen des Befehles den Zustand der SS-Leitung. Befindet sich diese auf LOW-Pegel, startet dies Karte in den SPI-Modus. Dieser wird erst nach der Trennung der Betriebsspannung zuruckge-setzt.

Send: 0x40 0x00 0x00 0x00 0x00 0x00 0x95 (CMD0)

Recv: 0x01 //R1-Antwort mit dem "in-idle-state"-Bit gesetzt

Abbildung 7: Setzen des Idle-Modus, Beispiel anhand von Pseudocode

1.6.3 Aktivieren des Betriebsmodus

Nach erfolgreichem Setzen des Idle-Modus muss die Karte noch betribsbereitgesetzt werden. Hierbei wir das Kommando ACMD41 (SD SEND OP COND)verwendet. Auch hier werde fur die Paramter-Bytes Nullen gesendet. DieCRC-Prufsumme wird ignoriert, es muss jedoch darauf geachtet werden dasdas letzte Bit

”HIGH“ ist.

Die Initialisierung kann eine Zeit lang dauern, die Karte sendet als Antwort0x01 wenn sie sich noch im Idle-Modus befindet. Das Kommando muss nunso langeverschickt werden bis man die richtige Antwort, also 0x00 erhalt.Damit befindet sich der Slave im betriebsbereiten Zustand.

Send: 0x77 0x00 0x00 0x00 0x00 0x00 0x01

//CMD55, Prefix fur ein ACMD-Kommando

Recv: 0x01

Send: 0x69 0x00 0x00 0x00 0x00 0x00 0x01

//ACMD41

Recv: 0x01

//R1-Antwort mit dem "in-idle-state"-Bit gesetzt

Abbildung 8: Setzen des Betriebsmodus, Beispiel in Pseudocode Teil1

Da sich die KArte noch im Idle-State befindet wird der Vorgang mehrmalswiederholt bis mal folgende Antwort erhalt:

9

Recv: 0x00 //R1-Antwort mit dem "in-idle-state"-Bit ungesetzt

Abbildung 9: Beispiel Teil2

2 USART

Universal Synchronus/Asynchronous Receiver Transimitter

Der USART ist eine gangige Schnittstelle, welche Einsatz bei vielen µCund PCs findet. Sie bietet somit eine einfache Austauschmoglichkeit der bei-den Komponenten. Ein direkter Anschluss ist nicht moglich, da mit unter-schiedlichen Pegeln gearbeitet wird. Verwendet wird daher der PegelwandlerMAX232, welcher den Pegel von 5V auf 10V erhoht und umgekehrt.In diesem Projekt wird die Schnittstelle lediglich zu Debug-Zwecken genutztwerden. Wahrend der Abarbeitungdes Programmcodes kann man schlechtnachempfinden wenn es zu Stopps oder Fehlfunktionen kommt. der Codewird also entsprechend angepasst Meldungen uber die USART-Schnittstellean den PC zu ubermitteln. Somit kann stets verfolgt werden wo Problemeentstanden, aber aber auch welche Programmschritte erfolgeich abgeschlos-sen wurden.

2.1 Die Register des USART

2.1.1 Kontroll- und Statusregister UCSRA

UCSRA steht fur USART Control & Status Register A. Es konnen, wie derName bereits sagt, Zustande ausgelesen und das Verhalten der Schnittstelleduch das manipulieren von Flags beeinflusst werden. Das Register A dienthauptsachlich der Anzeige des Status.

RXC (USART Receive Complete)Die abgeschlossene Ubertragung eines Zeichens vom Empfangs-Schieberegisterzum Empfangs-Datenregister wird mit diesem Flag signalisiert. DasZeichen muss aus dem Datenregister gelesen werden bevor das nachfol-gende Zeichen empfangen wird. Andernfalls kann es zu Fehler- oderUberlaufsituationen kommen. Das Zurucksetzen des Flags geschiehtmit dem Auslesen des Datenregisters.

TXC (USART Transmit Complete)Wurde das im Sende-Schieberigster befindliche Zeichen vollstandig aus-gegeben und steht kein weiters an wird dieses Bit gesetzt. Dieses Flag

10

ist bei Halbduplex-Verbindungen (Ubertragung jeweils in eine Rich-tung) von hoher Bedeutung, es signalisiert wann die Ubertragung vonSenden auf Empfangen gewechselt werden muss. Im Vollduplex-Betrieb(Ubertragung in beide Richtungen gleichzeitig) kann das Bit unbeach-tet bleiben. Die Loschung des Flags findet nur statt wenn der entspre-chende Interrupthandler aufgerufen wird, ansonsten muss es manuellzuruckgesetzt werden.

UDRE (UART Date Register Empty)Gibt den Zustand des Sendepuffers an. Ist er leer wird das Flag ge-setzt. Es wird zuruckgesetzt wenn ein Zeichen im Sende-Datenregistervorhanden ist und noch nicht in das Sende-Schieberegister ubernom-men wurde. Atmel empfielt das UDRE auf LOW zu setzen wenn dasUCSRA beschrieben wird. Wird ein Zeichen in das Sende-Datenregistergeschrieben, findet eine autmatische Loschung des Flags statt.

FE (Framing Error)Das Flag wird gesetzt wenn der USART einen Zeichenfehler erkennt,dass heisst wenn das Stopbit eines empfangenen Zeichens LOW ist.Das Flag wird zuruckgesetzt wenn das Stopbit des empfangen Zeichensgesetzt ist.

DOR (Data Over Run)Das Bit wird gesetzt wenn das im Empfangs-Datenregister befindlicheZeichen nicht abgeholt wird bevor das nachfolgende Zeichen komplettempfangen wurde. Daraufhin wird das nachfolgende Zeichen verworfen.Ein Zurucksetzen des Bits findet statt, wenn das empfangene Zeichenin das Empfangs-Datenregister verschoben werden konnte.

PE (Parity Error)Dieses Flag wird gesetzt, wenn das sich im Empfangs-Datenregisterbereitliegende Zeichen einen Paritatsfehler aufweist. Das Flag wirdzuruckgesetzt wenn das empfangene Zeichen ind das Empfangs-Datenregisterverschoben werden konnte.

U2X (Double the transmission speed)Im synchronen Betriebsmodus ist dieses Bit auf ’0’ zu setzen. Wird dasBit in der asynchronen Betriebsart gesetzt, so wird der Baudratendivi-sor von 16 auf 8 halbiert und somit die Ubertragungsgeschwindigkeitverdoppelt.

MPCM (Mulit Processor Communication Mode)Uber dieses Flag wird die Multi-Prozessor-Kommunikation aktiviert.

11

Jeder eintreffende Frame ohne Adressinformationen wird somit igno-riert.

2.1.2 Kontroll- und Statusregister UCSRB

12