Entwickeln mit CPLDs - Stefan Buchgeher · Leuchtdioden D3 bis D9 mit den Vorwiderständen R49 bis...

Transcript of Entwickeln mit CPLDs - Stefan Buchgeher · Leuchtdioden D3 bis D9 mit den Vorwiderständen R49 bis...

Entwickelnmit CPLDs(am Beispiel einer

DCF-Uhr)

Autor: Buchgeher StefanLetzte Bearbeitung: 15. Oktober 2006

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 2

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 3

Inhaltsverzeichnis1. EINLEITUNG..........................................................................................................5

2. GRUNDLEGENDES ZU DCF.................................................................................6

3. SCHALTUNGSBESCHREIBUNG (DCF-UHR) ......................................................8

4. SOFTWAREENTWURF MIT CPLDS AM BEISPIEL DCF-UHR..........................11

4.1. Grundlagen..............................................................................................................................................11

4.2. Einteilung der Aufgabe in Blöcke ...........................................................................................................11

4.3. Einteilung in Blöcke am Beispiel der DCF-Uhr ......................................................................................11

5. UMSETZUNG DES DESIGNS IN AHDL ..............................................................23

Schritt 1: Ein neues Projekt in Quartus anlegen................................................................................................23

Schritt 2: Eingabe des Designs in AHDL............................................................................................................27

Schritt 3: Systemtakt definieren.........................................................................................................................38

Schritt 4: Erste Kompilierung ............................................................................................................................39

Schritt 5: Pinnummern zuweisen........................................................................................................................42

Schritt 6: Zweite Kompilierung..........................................................................................................................43

6. SIMULATION .......................................................................................................44

Schritt 1: Ein Vector Waveform File für dieses Projekt erzeugen.....................................................................44

Schritt 2: Simulator-Einstellungen.....................................................................................................................48

Schritt 3: Simulation beginnen ...........................................................................................................................49

Schritt 4: Simulationsergebnis analysieren ........................................................................................................50

Schritt 5: Zweite Simulation...............................................................................................................................50

7. PROGRAMMIEREN .............................................................................................53

8. NACHBAUANLEITUNG.......................................................................................55

Schritt 1: Platinen herstellen ..............................................................................................................................55

Schritt 2: Platinen bestücken..............................................................................................................................55

Schritt 3: Test der Steuerplatine.........................................................................................................................58

Schritt 4: DCF-Modul montieren und erste Funktionskontrolle .......................................................................58

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 4

Schritt 5: Steuer- und Anzeigeplatinen miteinander verbinden und zweite Funktionskontrolle......................59

Schritt 6: „Befestigungswinkel“ und Acrylglas-Scheibe vorbereiten.................................................................60

Schritt 7: Endmontage........................................................................................................................................61

ANHANG A: LAYOUTS .............................................................................................62

ANHANG B: STÜCKLISTE........................................................................................64

ANHANG C: QUELLEN .............................................................................................66

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 5

1. EinleitungDie Abkürzung CPLD steht für Complex Programmable Logic Device und bedeutetsoviel wie programmierbarer Logikbaustein für komplexe Anwendungen. Solcheprogrammierbaren Logikbausteine werden von unterschiedlichen Herstellern angebotenund unterscheiden sich erheblich voneinander. Zudem gibt es noch unterschiedlicheTechnologien vom eher einfachen (PAL1 und GAL2) bis zu sehr komplexen (CPLD3 undFPGA4).

Hier bei diesem Projekt wurde ein CPLD von Altera ausgewählt. Dies ist rein willkürlich,denn grundsätzlich könnte auch ein Baustein eines anderen Herstellers verwendetwerden. Einschränkungen ergeben sich nur in der Anzahl der verfügbaren Pins und der„Größe“ des Bausteins. Mit Größe ist hier nicht die Abmessung gemeint sondern dieGröße der Schaltung sprich die Anzahl der Makrozellen.

Bei programmierbaren Logikbausteinen ist weiters zu beachten dass die Funktion derSchaltung in den Baustein programmiert werden muss. Dazu muss diese aber zuerst inirgendeine Form erstellt werden. Hier hat sich eine spezielle Sprache entwickelt unddurchgesetzt. Mit dieser Sprache ist es möglich die zu programmierende Schaltung zubeschreiben. Man nennt diese HDL5, wobei sich hier verschiedene Dialekte entwickelthaben (VHDL6, AHDL7, ABEL-HDL usw.). Hier, bei diesem Projekt wurde die vomHersteller entwickelte Sprache AHDL verwendet.

Schließlich muss die erstellte Software noch in den Logikbaustein (IC) gebracht werden.Dazu gibt es vom Hersteller mehrere Downloadkabel, die entweder die paralleleSchnittstelle oder die USB-Schnittstelle verwenden.

Zuletzt soll noch erwähnt werden, dass der Hersteller zu seinen programmierbarenLogikbausteinen auch eine kostenlose Entwicklungsumgebung bereitstellt. Diese kannvon der Hersteller-Hompage (www.altera.com) kostenlos gedownloadet werden.

1 PAL steht für Programmable Array Logic2 GAL steht für Generic Array Logic3 CPLD steht für Complex Programmable Logic Device4 FPGA steht für Field Programmable Gate Array5 HDL steht für Hardware Description Language6 VHDL steht für Very high speed integrated circuit Hardware Description Language7 AHDL steht für Altera Hardware Description Language

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 6

2. Grundlegendes zu DCFDer Zeitzeichensender DCF77 befindet sich in Mainflingen, ca.25 km südöstlich von Frankfurt am Main. DieserLangwellensender hat, bedingt durch die niedrigeTrägerfrequenz von 77,5 kHz eine Reichweite von ca. 1500 kmbis 2000 km. (Bild 2.1)

Der Dauerträger desDCF-Senders senkt imSekundentakt für 100ms oder 200ms dieAmplitude der Trägerfrequenz auf 25 % ab, waseiner einfachen Amplitudenmodulation ent-spricht. Die Länge dieser so genanntenSekundenmarken überträgt in codierter Form dasZeittelegramm. Eine Absenkdauer des Trägersum 100ms (Toleranz: ±20ms) entspricht dabei

einem logischen Low-Pegel, während einlogischer High-Pegel mit einer Absenkdauer von200ms (Toleranz ±40ms) codiert ist. In jeder 59.

Sekunde wird die Absenkung nicht vorgenommen, so dass damit eine eindeutigeZuordnung des Minutenanfangs möglich ist. Die neue Sekunde beginnt, mit Ausnahmeder 59. Sekunde, jeweils mit dem Absenken des 77,5 kHz-Trägers.

Im jeweils einminütigem Zeittelegramm ist die Zeit (Stunde und Minute) der nächst-folgenden Minute sowie das komplette Datum und der jeweilige Wochentag codiert. Diefolgende Tabelle zeigt die Bedeutung der 59 Bits, die pro Minute versandt werden.

Bit Bedeutung Wertig-keit

Bit Bedeutung Wertig-keit

0 Minutenbeginn Low 20 Telegrammbeginn High1 Reserve 21 Minuten Einer 12 Reserve 22 Minuten Einer 23 Reserve 23 Minuten Einer 44 Reserve 24 Minuten Einer 85 Reserve 25 Minuten Zehner 106 Reserve 26 Minuten Zehner 207 Reserve 27 Minuten Zehner 408 Reserve 28 Prüfbit 19 Reserve 29 Stunden Einer 110 Reserve 30 Stunden Einer 211 Reserve 31 Stunden Einer 412 Reserve 32 Stunden Einer 813 Reserve 33 Stunden Zehner 1014 Reserve 34 Stunden Zehner 2015 Reserveantenne 35 Prüfbit 216 Zeitumstellung Ankündigung 36 Kalendertag Einer 117 Zeitzonenbit 1 37 Kalendertag Einer 218 Zeitzonenbit 2 38 Kalendertag Einer 419 Schaltsekunde Ankündigung 39 Kalendertag Einer 8

Tabelle 2.1: Zeittelegramm

Bild 2.1: Rechweite des DCF77-Senders(Quelle: www.dcf77.com/)

Bild 2.2: Amplitudenmodulation des77,5kHz-Trägers

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 7

Bit Bedeutung Wertig-keit

Bit Bedeutung Wertig-keit

40 Kalendertag Zehner 10 50 Jahr Einer 141 Kalendertag Zehner 20 51 Jahr Einer 242 Wochentag 1 52 Jahr Einer 443 Wochentag 2 53 Jahr Einer 844 Wochentag 4 54 Jahr Zehner 1045 Monat Einer 1 55 Jahr Zehner 2046 Monat Einer 2 56 Jahr Zehner 4047 Monat Einer 4 57 Jahr Zehner 8048 Monat Einer 8 58 Prüfbit 349 Monat Zehner 10 59 Keine Austastung

Tabelle 2.1: Zeittelegramm (Fortsetzung)

Die Synchronisation des Sekundenzählers erfolgt mit Ausbleiben der Absenkung der59. Sekunde. Die nächste Absenkung ist immer Low. Die Bits 1 bis 14 sind nicht belegt.Bit 15 zeigt durch einen High-Pegel an, dass zurzeit die Reserveantenne des DCF77-Senders aktiv ist. Im Normalfall ist dieses Bit auf „Low“ gesetzt. Bit 16 wird eine Stundebevor die Zeitumstellung von Sommer- auf Winterzeit bzw. umgekehrt erfolgt auf „high“gesetzt und mit der Zeitumstellung wieder zurückgesetzt. Die Zeitangaben beziehensich auf die UTC-Zeit (Universal Time Coordinated). Bezogen auf die UTC-Zeit eilt diemitteleuropäische Zeit (MEZ) um eine Stunde vor, während die mitteleuropäischeSommerzeit (MESZ) um 2 Stunden voreilt. Diese Differenz wird in den Zeitzonenbits 17und 18 ausgedrückt. Während der MEZ ist Bit 17 High und Bit 18 Low, während bei derSommerzeit (MESZ) der Abstand zur UTC 2 Stunden beträgt und somit Bit 17 Low undBit 18 High ist. Bit 19 kündigt eine bevorstehende Schaltsekunde an. Das eigentlicheZeit- und Datumstelegramm ist in den Bits 20 bis 58 codiert. Für die Einerstellen derZeit und Datumsinformationen sind jeweils 4 Bit, während für die Zehnerstellen nur 2oder 3 Bit erforderlich sind. Die Zahlendarstellung der Zeit- und Datumsinformationerfolgt im Binärformat (BCD-Code). Für die Jahreszahl werden nur die Einer- undZehnerstelle übertragen. Die Bits 42 bis 44 geben in binärer Schreibweise denWochentag an (der Wert 1 steht für den Montag, der Wert 7 für den Sonntag). DasPrüfbit 1 ergänzt die Bits 21 bis 27 auf gerade Parität, d.h. es werden die High-Bits 21bis einschließlich 28 addiert, deren Ergebnis muss dann eine gerade Zahl ergeben. DasPrüfbit 2 ergänzt die Parität von Bit 29 bis 34, während Prüfbit 3 für die Parität der Bits36 bis 57 zuständig ist. Diese Prüfbits sind ein erstes Überprüfungskriterium für einDCF-Empfangsprogramm, welches damit zunächst auf einfache Weise die Konformitätder empfangenen Daten überprüfen kann. Für eine fehlerfreie DCF-Decodierung sindallerdings noch weitere Maßnahmen notwendig. (Zum Beispiel ein Vergleich der soebendekodierten Uhrzeit und des Datums mit der Uhrzeit und dem Datum welches mit dervorhergehenden Minute übertragen wurde und zusätzlich noch eine mitlaufendeSoftwareuhr).

In unregelmäßigen Zeitabständen muss eine Schaltsekunde eingefügt werden. Dies istdadurch bedingt, dass sich die Erde nicht genau in 24 Stunden um sich selbst dreht.Auf die koordinierte Weltzeitskala UTC bezogen, wird diese Korrektur zum Ende derletzten Stunde des 31. Dezember oder 30. Juni vorgenommen. In Mitteleuropa mussdie Schaltsekunde daher am 1. Januar um 1.00 Uhr MEZ oder am 1.Juli um 2.00 MESZeingeschoben werden. Zu den genannten Zeiten werden daher 61 Sekunden gesendet.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 8

3. Schaltungsbeschreibung (DCF-Uhr)

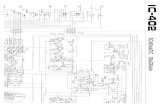

Bild 3.1.: Schaltung

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 9

Die Schaltung sieht auf dem ersten Blick vielleicht etwas umfangreich aus, ist abereigentlich sehr einfach. Es handelt sich um einige Standardlösungen.

Der größte Bauteil ist das CPLD (IC1). Dieser benötigt neben derVersorgungsspannung (Anschlüsse VCCxx und GND) zunächst eine Reset-Beschaltung und eine Takt-Beschaltung.Die Reset-Beschaltung besteht aus einem einfachen RC-Glied bestehend aus demWiderstand R1 und dem Elektrolyt-Kondensator C1. Dieses RC-Glied bewirkt bei jedemEinschalten einen Reset.Die Takt-Beschaltung ist schon etwas umfangreicher. Sie besteht aus einem speziellenInverter (IC2), einem 32,768kHz-Quarz (X1) zwei Kondensatoren (C2 und C3) und zweiWiderständen (R2 und R3)8.Der eher unübliche Wert für den Quarz von 32,768kHz wurde deswegen gewählt, weildaraus sehr einfach ein 1-Hz-Takt erzeugt werden kann. Dieser 1-Hz wird im CPLD fürdie Uhr benötigt. (siehe auch Abschnitt 4.3.).Wichtig: Für IC2 muss unbedingt der in der Stückliste angegebene Typ 74HCU04verwendet werden.

Die Ausgabe der Uhrzeit erfolgt mit 7-Segment-Anzeigen (LD1 bis LD5). LD5 beinhaltetzwei solche 7-Segment-Anzeigen, während LD1 bis LD4 nur jeweils eine beinhalten,dafür sind diese aber etwas größer. Für jede 7-Segment-Anzeige ist jeweils ein eigenerDekoder-IC notwendig (IC3 bis IC8 vom Typ 74LS47). Diese Dekoder haben dieAufgabe die richtigen Segmente einer 7-Segment-Anzeige anzusteuern. Weiters sindfür jedes Segment der 7-Segment-Anzeige Vorwiderstände notwendig (R5 bis R18 undR21 bis R48). Dabei fällt auf, dass die Vorwiderstände R35 bis R48 einen größerenWert besitzen. Dies liegt daran, dass unterschiedliche 7-Segment-Anzeigen verwendetwurden, die unterschiedlich stark leuchten. Durch diese unterschiedlichenWiderstandswerte wird erreicht, dass trotzdem alle Anzeigen in etwa gleich hellleuchten. Die Dekoder-ICs besitzen einige Steuerleitungen, die hier zu besonderen„Effekten“ führen. Mit dem Steuereingang RBI (Pin 5) wird die 7-Segment-Anzeige nurdann aktiv, wenn sie einen Wert größer als 0 anzeigen soll. Mit anderen Worten: eine 0wird nicht angezeigt. Dies wird hier bei der Zehnerstelle der Stundenanzeigeausgenützt. Die übrigen 7-Segment-Anzeigen verwenden den Steuereingang BI/RB0(Pin 4). Mit diesem kann die Anzeige ein- und ausgeschaltet werden. Bei diesemProjekt erzielt man damit, dass die Anzeige erst dann eingeschaltet wird, wenn eingültiges DCF-Telegramm empfangen wurde.

Die Leuchtdioden D1 und D2 mit den Vorwiderständen R19 und R20 dienen zurAnzeige des Sekundentakts zwischen der Stunden- und Minutenanzeige. DieLeuchtdioden D3 bis D9 mit den Vorwiderständen R49 bis R55 dienen zur Anzeige vonStatusinformationen. Diese sind optional und können mit den Jumpern JP1 bis JP7ausgeschaltet werden. Die Leuchtdioden D8 und D9 haben hier noch keine Bedeutung,sie sind aber für weitere Zwecke vorhanden, da noch genügend Ein/Ausgabepinsvorhanden sind. IC9 dient hier zur Isolierung, da Verbraucher (Leuchtdioden, Relais,Motoren etc.) nicht direkt an das CPLD angeschlossen werden sollen.

Der 10polige Anschluss JTAG (K1) dient zum Programmieren des CPLD.

8 Eine genauere Beschreibung zu dieser Takt-Schaltung finden Sie im Buch „306 Schaltungen“ (ISBN: 3-89576-022-6), Seite 399f

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 10

Zur Dekodierung des DCF-Telegramms dient ein bei Conrad erhältliches DCF-Empfangsmodul (Bestell-Nr.: 641138). Dieses Modul enthält eine Empfangsantenneund einen Demodulator, so dass am Ausgang des Moduls das übertrageneZeittelegramm mit einem CPLD ausgewertet werden kann. Bild 3.2. zeigt dieses DCF-Empfangsmodul.

Bild 3.2.: DCF-Empfangsmodul

Der Ausgangsstrom von nur einem Milliampere ist für die Kontroll-Leuchtdiode (D12)zuwenig. Die nachgeschaltete Transistorstufe (T1) mit den Widerständen R56 und R58gleicht diesen Nachteil aus. Der Widerstand R57 dient als Vorwiderstand für dieLeuchtdiode (D12). Diese Leuchtdiode signalisiert den empfangenen Datenstrom, wennder Jumper JP9 gesteckt ist. Bei einem korrekten Empfang blinkt diese Leuchtdiode imSekundentakt. Dieses Blinken zeigt sozusagen den Ausgangspegel der Anpass-Schaltung an. Das Puls-Pausen-Verhältnis (Leuchtzeit/Dunkelzeit der Leuchtdiode D12)entspricht der im Abschnitt 2 genannten Zeiten. Bei etwas Übung kann der Unterschiedzwischen Low (100ms Absenkung des Trägers, LED ist 100ms dunkel) und High(200ms Absenkung des Trägers, LED ist 200ms dunkel) optisch erkannt werden.

Der Kondensator C16 dient zur Entkoppelung der Betriebsspannung für das DCF-Modul. Für diesen Koppelkondensator sollte ein Keramiktyp verwendet werden. Diesermuss möglichst nahe am DCF-Modul angebracht werden.

Für die Stromversorgung wurde ebenfalls eine Standardschaltung bestehend aus demFestspannungsregler (IC10) vom Typ 7805 und den Kondensatoren C4 bis C7 gewählt.Da die 7-Segment-Anzeigen und das CPLD einiges an Strom benötigen, wird derFestspannungsregler schon ziemlich warm. Daher sollte dieser mit einem Kühlkörper(gemäß Stückliste im Anhang B) versehen werden.Die Diode D10 dient als Verpolungsschutz und die Leuchtdiode D11 zeigt an, ob dieDCF-Uhr mit Spannung versorgt ist.

Die Kondensatoren C8 bis C12 dienen zur Entkoppelung der Betriebsspannung für IC2bis IC9. Für diese Koppelkondensatoren sollten Keramiktyp verwendet werden. Diesesollten möglichst nahe an den ICs angebracht werden.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 11

4. Softwareentwurf mit CPLDs am Beispiel DCF-Uhr

4.1. GrundlagenKomplexe digitale Schaltungen sind stets eine Zusammensetzung aus kombinatorischerLogik9 (in Form von Addierer, Adressdekodierer, Multiplexer und Demultiplexer, usw.)und sequentieller Logik10 (in Form von Zählern, Schieberegister, diskreten FlipFlopsund Zustandsmaschinen). Es ist daher unbedingt notwendig, dass man diese digitalenGrundschaltungen beherrscht.

4.2. Einteilung der Aufgabe in BlöckeBei der Entwicklung von Schaltungen mit CPLDs gibt es eine Vielzahl von Ansätzenund Vorgehensweisen. Eine davon ist die so genannte „Top-Down-Methode“. Bei dieserMethode wird der gesamten Prozess in Blöcke unterteilen. Diesen Blöcken ordnet manbestimmte Aufgaben zu, wobei man sich vorerst noch nicht um deren Innenleben zukümmern braucht. Auf dieser Ebene denkt man über den gesamten Prozess nach undversucht dabei das Zusammenspiel dieser Blöcke zu optimieren. Erscheint einem dieseAufteilung optimal, so Unterteilt man die einzelnen Blöcke wieder in Unterblöcke. Dabeigeht man genau so vor, wie in der ersten Ebene. Nun kann man sich auf die Aufteilungdieser bereits kleineren Blöcke konzentrieren und muss sich nicht mehr so intensiv mitdem gesamten Prozess kümmern. Diese Vorgehensweise wiederholt man so lange, bisman schließlich bei Blöcken mit einer überschaubaren Größe angekommen ist. DieseBlöcke können dann meist als einfache Zustandsmaschinen oder als kombinatorischeLogik realisiert werden.

4.3. Einteilung in Blöcke am Beispiel der DCF-UhrBevor man die gestellte Software-Aufgabe in Blöcke einteilen kann, muss man sichzuerst im Klaren sein, was denn die Software alles erledigen muss, und wie man dieseam besten und sinnvollsten realisiert. (Dabei spielt sicher auch die Erfahrung einewichtige Rolle!)

Hier, bei der DCF-Uhr hat die Software (im Zusammenspiel mit der Hardware) folgendeAufgaben:• Aus dem seriellen DCF-Datenstrom (Eingangspin 55) „Low“, „High“

„Minutenwechsel“ ermitteln. (gemäß Abschnitt 2. Grundlegendes zu DCF). DieseInformationen zwischenspeichern und an den Ausgängen 51 (für „Low“) und 52 (für„High“) ausgeben.

• Bei einem fehlerhaften Empfang (d.h. wenn weder ein „Low“, ein „High“ oder ein„Minutenwechsel“ erkannt wurde, die Fehler Ausgänge 41 und 49 setzen.

• Eine frei mitlaufende Uhr, welche ständig mit einer gültigen Uhrzeit aus dem DCF-Empfang synchronisiert wird. Eine gültige Uhrzeit liegt vor, wenn ein DCF-Telegramm fehlerfrei empfangen wurde.

9 Kombinatorische Logik wird oft auch mit „Schaltwerke“ bezeichnet10 Sequentielle Logik wird oft auch mit „Schaltnetze“ bezeichnet

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 12

• Die Anzeige der Uhrzeit soll erst dann erfolgen, wenn ein gültiges DCF-Telegrammempfangen wurde. (Ausgangspin 16). Dies soll außerdem am Ausgang „Sync“ (Pin45) angezeigt werden.

• Die Uhrzeit in BCD-Form ausgeben.• Alle Eingänge mit dem Takt synchronisieren. Dies erfolgt normalerweise mit einem

einfachen D-FlipFlop. Anmerkung: Die DCF-Uhr besitzt nur einen Eingang, folglichist nur ein D-FlipFlop notwendig.

Bild 4.1. zeigt die Blockeinteilung für die DCF-Uhr. Bei dieser ersten Aufteilung sprichtman auch vom „Top-Design“ oder „Top-Level-Design“.

Bild 4.1.: Top-Level-Design (DCF-Uhr)

Hier, bei der DCF-Uhr erfolgt das Top-Level-Design aus zwei Blöcken.

Anmerkung: Die hier getroffene Blockeinteilung ist sicher nur eine Möglichkeit vonmehreren. Hier liegt die Freiheit des Entwicklers, die geforderte Aufgabe in sinnvolleTeilaufgaben zu zerlegen, was mitunter auch ein wenig Erfahrung benötigt.

Block „DCF-Dekodierung“Dieser Block hat die Haupt-Aufgabe aus dem seriellen DCF-Datenstrom dasTelegramm (Low- und High-Bits) zu ermitteln und diese zwischenzuspeichern.

Die Bilder 4.2. und 4.3. zeigen die Realisierung dieses Blocks. Dieser Block besteht auseiner Zustandsmaschine (iZM_DCF), einem Zähler (iZAEHLER_DCF) zur Ermittlungvon Zeiten, einem Schiebregister (iSR_DCF) zur Speicherung des Telegramms, undeinigen D-FlipFlops zur Speicherung diverser Zustände und zur Synchronisierung desDCF-Eingangs mit dem Systemtakt (iFF_DCF_In).

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 13

Bild 4.2.: Block “DCF-Dekodierung”

Die Hauptaufgabe der Zustandsmaschine (iZM_DCF) ist es aus dem seriellenDatenstrom am Eingang die LOWs und HIGHs zu ermitteln. Gemäß Abschnitt 2 erfolgtzu jeder Sekunde ein Impuls. Ein Low-Impuls dauert zwischen 80ms und 120ms undein High-Impuls zwischen 160ms und 240ms. Bei einem Minutenwechsel bleibt dieserImpuls aus. Bild 4.3 (links oben) zeigt noch einmal diesen Zusammenhang. Für dieAuswertung ist aber nicht diese Impulszeit interessant, sondern vielmehr die Zeitzwischen zwei Impulsen (siehe Bild 4.3, links oben). Denn mit dieser Zeit kanneindeutig zwischen einem Low, einem High und einem Minutenwechsel unterschiedenwerden. Die Grundidee ist nun die, dass, diese Zeit mit Hilfe eines Zählers(iZAEHLER_DCF im Bild 4.2.) gezählt wird, wobei der Zähler bei einer steigendenFlanke am Eingang freigegeben (also gestartet wird) und bei einer fallenden Flanke amEingang wird der Zählwert eingelesen und ausgewertet. Im Zustandsdiagramm (Bild4.3.) sind dies die Zustände Z0, Z1 und Z2. Erfolgt aber nach einer gewissen Zeit keinefallende Flanke, so erfolgt ein Time-Out, also ein Fehler. Gemäß Zustandsdiagramm(Bild 4.3.) erfolgt dann nach dem Zustand Z1 der Zustand Z7, wo die beiden Fehler-FlipFlops (iFF_DCF_BitFehler und iFF_DCF_Fehler) gesetzt werden. Anschließendgelangt die Zustandsmaschine in den Ausgangszustand (Z0) zurück und wartet auf dienächste steigende Flanke.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 14

Bild 4.3.: Zustandsdiagramm „iZM_DCF“

Erfolgt aber eine fallende Flanke am Eingang innerhalb der Time-Out-Zeit, so gelangtdie Zustandmaschine nun zum Zustand Z2. hier erfolgt die Auswertung desZählerstands des Zählers iZAEHLER_DCF.• Entspricht der Zählerstand dieses Zählers einem Wert zwischen 28835 (entspricht

880 ms) und 30147 (entspricht 920 ms), so wurde ein LOW empfangen. Daher folgtauf den Zustand Z2 nun der Zustand Z3, wo dem Schieberegister (iSR_DCF) einLOW hinzugefügt wird. Weiters wird das FlipFlop iFF_DCF_Lo gesetzt, zurKennzeichnung, dass ein Low empfangen wurde, während die FilpFlopsiFF_DCF_High und iFF_DCF_BitFehler gelöscht werden. Anschließend gelangt dieZustandsmaschine in den Ausgangszustand (Z0) zurück und wartet auf die nächstesteigende Flanke.

• Entspricht der Zählerstand dieses Zählers einem Wert zwischen 24903 (entspricht760 ms) und 27526 (entspricht 840 ms), so wurde ein HIGH empfangen. Daher folgtauf den Zustand Z2 nun der Zustand Z4, wo dem Schieberegister (iSR_DCF) einHIGH hinzugefügt wird. Weiters wird das FlipFlop iFF_DCF_High gesetzt, zurKennzeichnung, dass ein High empfangen wurde, während die FilpFlopsiFF_DCF_Lo und iFF_DCF_BitFehler gelöscht werden. Anschließend gelangt dieZustandsmaschine in den Ausgangszustand (Z0) zurück und wartet auf die nächstesteigende Flanke.

• Entspricht der Zählerstand dieses Zählers einem Wert zwischen 57671 (entspricht1760 ms) und 62915 (entspricht 1920 ms), so wurde ein Minutenwechselempfangen. Daher folgt auf den Zustand Z2 nun der Zustand Z5, wenn das Fehler-FlipFlop iFF_DCF_Fehler nicht gesetzt ist, oder der Zustand Z6, wenn das Fehler-FlipFlop iFF_DCF_Fehler gesetzt ist. Diese Unterscheidung hat folgende Gründe:

o Ist das Fehler-FlipFlop iFF_DCF_Fehler nicht gesetzt, so bedeutet dass,das ein komplettes DCF_Telegramm fehlerfrei empfangen wurde, da jasobald ein Fehler auftritt dieses Fehler-FlipFlop gesetzt wird

o Zu Beginn (also nach dem Einschalten) ist das Fehler-FlipFlop gesetzt(der Set-Eingang dieses FlipFlops ist ja mit der Reset-Leitung verbunden,

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 15

siehe Bild 4.2.). Das bedeutet, dass zunächst auf einen Minutenwechselgewartet werden muss.

Im Zustand Z5 wird die frei mitlaufende Uhr mit der empfangenen DCF-Uhrzeit (undDatum) synchronisiert. Die Daten (Uhrzeit und Datum) befinden sich ja nun imSchieberegister und können an den entsprechenden Ausgängen abgegriffenwerden. Bild 4.4. zeigt, welche Daten an welchen Ausgängen des Schieberegistersanliegen. Weiters wird im Zustand Z5 das FlipFlop iFF_DCF_Sync gesetzt. Diesezeigt an, dass die DCF-Uhr nun synchronisiert ist. Anschließend gelangt dieZustandsmaschine in den Ausgangszustand (Z0) zurück und wartet auf die nächstesteigende Flanke.Der Zustand Z6 hat nur die Aufgabe, das Fehler-FlipFlop iFF_DCF_Fehler wiederzurückzusetzen. In diesem Fall wird die frei mitlaufende Uhr nicht mit den Datenvom Schieberegister synchronisiert, da die Daten im Schieberegister fehlerhaft sind.Anschließend gelangt die Zustandsmaschine in den Ausgangszustand (Z0) zurückund wartet auf die nächste steigende Flanke.

Bild 4.4.: Schieberegister iSR_DCF

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 16

Noch eine Anmerkung zum Zähler iZAEHLER_DCF:Der Systemtakt beträgt, wie schon im Abschnitt 3 erläutert, f = 32,768 kHz. Da derZähler iZAEHLER_DCF mit diesem Takt getaktet wird ergibt sich eine Zeit T von

sf

T32768

11==

Für eine Zeit von Beispielsweise t = 880ms (wie oben erwähnt) ergibt sich somit einZählerstand von

Also ein Zählwert von 28835.

Achtung: Der Nachteil bei dieser Auswertemethode ist, dass die Uhr um 1 Sekundenachgeht, da ja die Auswertung am „Ende der Sekunde erfolgt“, und da beginnt jaschon die „neue Sekunde“. Im Allgemeinen spielt dass aber nur eine sehruntergeordnete Rolle.

Block „Freilaufende Uhr“Dieser Block hat die Haupt-Aufgabe eine (freilaufende) Uhr zu erzeugen, welche auchgeladen werden kann. Die einfachste Realisierung einer Uhr besteht darin Zählerhintereinander zu schalten, wobei der Ausgang des ersten Zählers der Takt für denzweiten Zähler ist, der Ausgang des zweiten Zählers der Takt für den nächsten Zählerusw. Diese asynchrone Methode wird als „Ripple-Counter“ bezeichnet. Ihr größterVorteil ist ihre Einfachheit. Ihre Nachteile sollten aber auch nicht unerwähnt bleiben.Diese asynchrone Methode eignet sich nur für niedrige Frequenzen und es könnenbeim Übergang von einem Zählwert zum nächsten Zählwert kurzzeitig falscheZählwerte auftreten. Beide Nachteile sind bei dieser Anwendung als DCF-Uhr aber vonuntergeordneter Rolle, da der Systemtakt mit 32.768kHz sehr gering ist, und die Uhrzeitnur mit 7-Segment-Anzeigen angezeigt werden soll. Unser menschliches Augebekommt es gar nicht mit, wenn kurzzeitig (kurzzeitig bedeutet hier im 10ns-Bereich)eine „falsche“ Uhrzeit angezeigt wird.

Bild 4.5. zeigt die Realisierung der freilaufenden Uhr.

Bild 4.5.: Block “Freilaufende Uhr”

84,288353276888,0 1 =⋅=⋅== −ssftTtZählerwert

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 17

Dieser Block wird hier wieder in mehrere Blöcke gemäß Abschnitt 4.2 aufgeteilt. Hierhandelt es sich im Wesentlichen um verschiedene Zähler. Die Aufgabe des erstenZählers ist die Erzeugung eines 1-Sekunden-Taktes aus dem Systemtakt. Die nächstendrei Blöcke sind für die Uhrzeit zuständig. Hier handelt es sich jeweils um BCD-Zählervon 0 bis 59 (für Sekunden und Minuten) bzw. von 0 bis 23 (für die Stunden).

Neben dem Systemtakt (clock_DCF) sind noch die Leitungen „Uhr freigeben“, „Laden“und das dekodierte DCF-Telegramm vorhanden. Die freilaufende Uhr soll erst dann „mitihrer Arbeit beginnen“, wenn ein gültiges DCF-Telegramm empfangen wurde. Erst abdiesem Zeitpunkt wird die Anzeige mit der Leitung „Uhr freigeben“ aktiviert und diefreilaufende Uhr beginnt unabhängig von der DCF-Dekodierung zu laufen, wobei aberjedes Mal wenn ein gültiges DCF-Telegramm empfangen wurde die Uhr (also dieZähler) mit den Daten aus dem DCF-Telegramm überschrieben werden. Dazu ist dieLeitung „Laden“ zuständig. Weiters soll die Leitung „Laden“ auch den Sekundenzählerund den Zähler für den Sekundentakt löschen.

Block „Zähler für Sekundentakt“Dieser Block hat die Aufgabe aus dem Systemtakt (32.768kHz) einen 1-Sekunden-Taktzu erzeugen. Wenn man bedenkt, dass 32768 nichts anderes als 215 ist, und manaußerdem weiß, dass jede Stufe eines Binärzähler durch 2 dividiert, so liegt es nahe fürdiese Aufgabe einen 15-Stufigen-Binärzähler zu verwenden. Altera bietet in seinerEntwicklungsumgebung (Quartus) u.a. solche Zähler (lpm_counter) an, welche nochüber einige Zusatzfunktionen (wie Zähler freigeben, Zähler löschen, Zähler laden usw.)verfügen. Diese Zusatzfunktionen kommen uns sehr gelegen, da wir diese hier teilweiseverwenden, denn dieser Zähler soll wie Bild 4.5. zeigt, freigegeben und gelöscht werdenkönnen.

Block „BCD-Zähler 0 - 59 (Sekunden)“Bild 4.6. zeigt einen BCD-Zähler für die Sekunden. Dieser besteht aus einem 4-Bit-Zähler für die Sekunden-Einer (iZAEHLER_SEK_E) und einem 3-Bit-Zähler für dieSekunden-Zehner (iZAEHLER_SEK_Z), wobei diese Zähler aber nicht ihren gesamtenZählbereich (0 bis 15 bzw. 0 bis 7) ausnützen sondern nur den für Sekunden sinnvollenBereich von 0 bis 9 (Einer) und 0 bis 5 (Zehner). Diese Eigenschaft lässt sich in derSoftware für jeden Zähler angeben. (siehe Abschnitt 5, Schritt 2)Die Steuerleitung „Laden“ setzt beide Zähler zurück.

Bild 4.6.: Block “BCD-Zähler 0-59 (Sekunden)”

Der Takt für den Sekunden-Einer-Zähler (iZAEHLER_SEK_Z) stammt vom Block„Zähler für Sekundentakt“ (siehe Bild 4.5.). Als Takt für den Sekunden-Zehner-Zähler(iZAEHLER_SEK_Z) dient der höchstwertige Ausgang (q[3]) des Sekunden-Einer-

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 18

Zählers (iZAEHLER_SEK_E) in negierter Form (siehe Bild 4.6). Bild 4.7. zeigt weshalb.Beim Übergang von 9 nach 0 des Sekunden-Einer-Zählers geht der Ausgang q[3] vonhigh nach low. Da dies der einzige high-low-Übergang von q[3] ist und dieser genaudann auftritt wenn der Zählstand der Sekunde von 9 nach 0 übergeht kann dieser alsTakt für die Zehner-Stelle dienen. Allerdings in negierter Form.

Bild 4.7.: Zeitdiagramm des Zählers für die Einerstelle der Sekunde

Ähnliches gilt als Takt für den nachfolgenden Minuten-Zähler-Block. Als Takt für denMinuten-Einer-Zähler (iZAEHLER_MIN_E) dient der höchstwertige Ausgang (q[2]) desSekunden-Zehner-Zählers (iZAEHLER_SEK_Z) in negierter Form (siehe Bild 4.5). Bild4.8. zeigt weshalb. Beim Übergang von 5 nach 0 des Sekunden-Zehner-Zählers gehtder Ausgang q[2] von high nach low. Da dies der einzige High-Low-Übergang von q[1]ist und dieser genau dann auftritt wenn der Zählstand der Minute von 5 nach 0 übergehtkann dieser als Takt für die Einer-Stelle für die Minute dienen. Allerdings in negierterForm.

Bild 4.8.: Zeitdiagramm des Zählers für die Zehnerstelle der Sekunde

Block „BCD-Zähler 0 - 59 (Minuten)“Bild 4.9. zeigt einen BCD-Zähler für die Minuten. Auch dieser Block besteht aus einem4-Bit-Zähler (für die Minuten-Einer, iZAEHLER_MIN_E) und einem 3-Bit-Zähler (für dieMinuten-Zehner, iZAEHLER_MIN_Z). Der Unterschied zum Block „BCD-Zähler 0-59(Sekunden)“ ist, dass diese beiden Zähler geladen werden können. Und zwar mit derMinuten-Information aus dem DCF-Telegramm. Die Steuerleitung „Laden“ hat also hierdie Aufgabe die beiden Zähler mit den anliegenden Daten aus dem DCF-Telegramm zuladen. Diese Daten liegen an den Zähler-Eingängen data[3..0] (für die Einerstelle) bzw.data[2..0] für die Zehnerstelle an.Als Takt für Einerzähler dient, wie schon vorher erwähnt, der höchstwertigeZählerausgang des Zählers für die Sekunden-Zehnerstelle (q[2]), allerdings in negierterForm. Als Takt für den Minuten-Zehner-Zähler dient der höchstwertige Ausgang (q[3])des Minuten-Einer-Zählers (iZAEHLER_MIN_E) in negierter Form (siehe Bild 4.9). Auchhier gelten die gleichen Überlegungen wie für den Block „BCD-Zähler 0-59 (Sekunden)“.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 19

Bild 4.9.: Block “BCD-Zähler 0-59 (Minuten)”

Block „BCD-Zähler 0 - 23 (Stunden)“Bild 4.10. zeigt einen BCD-Zähler für die Stunden. Auch dieser Block besteht aus einem4-Bit-Zähler (für die Stunden-Einer, iZAEHLER_STD_E) und einem 2-Bit-Zähler (für dieStunden-Zehner, iZAEHLER_STD_Z).

Bild 4.10.: Block “BCD-Zähler 0-23 (Stunden)”

Die Besonderheit bei diesem BCD-Zähler ist, dass dieser nur bis 23 zählen soll. Dieserreicht man dadurch, indem man, sobald der BCD-Zähler zum Wert 24 gelangt beideZähler löscht. Diese Aufgabe übernimmt das UND-Gatter (siehe Bild 4.10). DerAusgang dieses UND-Gatters ist mit den Lösch-Eingängen (.aclr) der beiden Zählerverbunden. D.h. sobald beide Eingänge am UND-Gatter logisch high sind wird derZähler gelöscht und beginnt wieder beim Wert 0 zu zählen. Das Zeitdiagramm (Bild4.11.) zeigt uns warum q[2] der Einerstelle und q[1] der Zehnerstelle als “Auslöser“ fürdas Löschen der Zähler zu verwenden sind.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 20

Bild 4.11.: Zeitdiagramm (BCD-Zähler 0-23, Stunden)

Die Kombination q[2] (Einer) = 1 und q[1] (Zehner) = 1 tritt wie im Bild 4.11. zu erkennennur beim BCD-Zählwert 24 auf.

Der „Nachteil“ bei dieser Methode ist, dass kurzzeitig der Wert 24 am Ausgang desBCD-Zählers ansteht. Hier, bei dieser Anwendung als einfach DCF-Uhr, welche nur dieUhrzeit anzeigen soll ist dieser Nachteil nicht von großer Bedeutung, da die Zeit, wodieser „falsche“ Wert angezeigt wird nur sehr, sehr gering ist (im ns-Bereich), und dahervom menschlichen Auge gar nicht wahrgenommen wird.

Beginnt man nun mit den zuletzt beschriebenen Blöcken und fügt man diese in denjeweils übergeordneten Block ein, also die Bilder 4.10., 4.9. und 4.6. in 4.5., diesen und4.2. in das Top-Level-Design (Bild 4.1.) so ergibt sich das fertige Design. Bild 4.12a.zeigt dieses fertige Gesamtdesign für die Anwendung des CPLD als DCF-Uhr. Bild4.12b. zeigt nochmals die Zustandsmaschine (iZM_DCF) vom Bild 4.3.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 21

Bild 4.12a. Gesamtdesign

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 22

Bild 4.12b.: Gesamtdesign (Zustandsdiagramm „iZM_DCF“)

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 23

5. Umsetzung des Designs in AHDLAls nächster Schritt erfolgt nun die Umsetzung des am Papier entworfenen Designs(hier für die DCF-Uhr) in eine für das CPLD verständliche Sprache. Hierfür gibt esmehrere Möglichkeiten. Eine Möglichkeit wäre die Eingabe in Form eines Schaltplans.Diese Methode wird aber selten verwendet, da sie sehr zeitintensiv ist. Eine andereMethode ist die Verwendung einer so genanten „Hardware-Beschreibungssprache“(engl. HDL für Hardware Description Language). Da hier ein CPLD des HerstellersAltera verwendet wird liegt es nahe die von Altera entwickelte Variante AHDL zuverwenden. Weiters ist eine Entwicklungsumgebung notwendig. Hier fiel die Wahl aufdas von Altera entwickelte Entwicklungssystem „Quartus“ (Version II 5.0 Web-Edition),welches kostenlos vom Internet unter www.altera.com gedownloadet werden kann.Nach der Installation dieses Programms ist eine kostenlose Lizenz notwendig. (Durchumgehen dieser Lizenz kann zwar ein Design erstellt und kompiliert werden, es ist abernicht möglich dieses Design in ein CPLD zu programmieren)

Die nun folgenden Schritte sollen zeigen, wie man ein neues Projekt (mit Quartus)erstellt, welche Einstellungen notwendig sind, wie man das Design (vom Bild 5.12.) mitAHDL beschreibt, usw. Zu diesen Schritten existiert in der Online-Hilfe ein sehr gutesTutorial (allerdings nur in englischer Sprache)

Schritt 1: Ein neues Projekt in Quartus anlegenQuartus starten. Nach einer Weile erscheint der Startbildschirm (nach Bild 5.1)

Bild 5.1.: Startbild der Entwicklungssoftware Quartus (hier II Version 5.0)

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 24

Durch anklicken von „File“ und „New Project Wizard…“ wird ein Dialog zur Erstellungeines neues Projektes gestartet. Es erfolgt zunächst eine Einführung über folgendendurch zu führenden Schritte (Bild 5.2)

Bild 5.2.: Dialog zur Erstellung einesneuen Projekts (Einführung)

Taste „Next >“

Bild 5.3.: Dialog zur Erstellung einesneuen Projekts (Schritt 1)

Hier erfolgt die Auswahl des Projekt-Ordners, des Projekt-Namens und des Namensdes Top-Level-Designs.

Anmerkungen: Für den Projekt-Namen und für den Namen des Top-Level-Designssollten „sprechende“ Namen verwendet, so dass man schon an diesen Namen erkenntworum es bei diesem Projekt geht. Für beide kann durchaus, so wie hier, der gleicheName gewählt werden.

Taste „Next >“

1

23

4

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 25

Bild 5.4.: Dialog zur Erstellung einesneuen Projekts (Schritt 2)

Hier können schon vorhanden Design-Files in das Projekt eingebunden werden. Beidiesem Projekt gehen wir davon aus, dass noch keine Design-Files vorhanden sind. DieEingabefelder bleiben daher leer.

Taste „Next >“

Bild 5.5.: Dialog zur Erstellung einesneuen Projekts (Schritt 3)

Nun wird das CPLD ausgewählt. Wir verwenden hier ein Mitglied der MAX7000S-Familie (1). Mit dem Filter (2) kann die Suche nach dem verwendeten Typ erleichtertwerden. Da wir hier den Typ EPM7128SLC84-15 verwenden wählen wir diesen auchaus (3). Siehe auch Schaltungsbeschreibung (Abschnitt 3) und Stückliste (Anhang B)

Taste „Next >“

1

21

3

4

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 26

Bild 5.6.: Dialog zur Erstellung einesneuen Projekts (Schritt 4)

Hier können weitere (spezielle) Werkzeuge ausgewählt werden. Wir benötigen hierkeine.

Taste „Next >“

Bild 5.7.: Dialog zur Erstellung eines neuenProjekts (Schritt 5, Zusammenfassung)

Abschließend erfolgt eine Zusammenfassung über die gewählten Einstellungen.

Taste „Finish“

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 27

Bild 5.8.: Arbeitsbereich nach dem Erstellen eines neuen Projekts

Bild 5.8. zeigt wieder den Arbeitsbereich der Entwicklungsumgebung. Im Gegensatzzum Startbild (Bild 5.1) zeigt dieses nun ganz oben den Projekt-Ordner, denProjektnamen und den Namen des Top-Level-Designs an (1) und im Abschnitt „ProjectNavigator“befindet sich das gewählte CPLD (hier: EPM7128SLC84-15) und der Namedes Top-Level-Design (hier: dcf) (2). Nun folgt die Eingabe des Designs in der SpracheAHDL.

Schritt 2: Eingabe des Designs in AHDLDurch anklicken von „File“ und „New“ kann neues Design-File dem Projekt hinzugefügtwerden. Bild 5.9. zeigt eine Liste mit den möglichen Design-Arten. Wir wollen unserDesign in AHDL erstellen und wählen daher „AHDL File“ aus (1). Anschließend „OK“(2).

Bild 5.9.: Design-File-Auswahl

1

2

1

2

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 28

Bild 5.10 zeigt nun den „neuen“ Arbeitsbereich. Im neuen Fenster erfolgt nun dieEingabe der Code-Zeilen.

Bild 5.10.: Arbeitsbereich

Da wir unser Design in AHDL beschreiben wollen, zunächst den grundlegenden Aufbaueines AHDL-Design-Files.

Auf den folgenden Seiten ist nun das AHDL-File für die DCF-Uhr in Form eines Listingszu sehen. Man erkennt den soeben erwähnten Aufbau. Zur besseren Orientierung habeich auch die Zeilennummern angegeben, so wie sie auch in der Entwicklungsumgebungangezeigt werden:• In Zeile 27 erkennt man den Namen des Designs, hier: SUBDESIGN dcf.• In den Zeilen 29 bis 52 werden alle Ein- und Ausgänge definiert (Anmerkung: Die

Zuweisung der Pinnummern erfolgt an anderer Stelle, siehe Schritt 5)• In den Zeilen 57 bis 147 erfolgt die Definition und Einstellung aller verwendeten

Flipflops, Zähler, Schieberegister und der Zustandsmaschine.• Ab Zeile 151 (bis zum Ende) beginnt schließlich die Beschreibung der Schaltung.

SUBDESIGN xxx(

…)

VARIABLE…

BEGIN…

END;

Hier werden alle Ein- und Ausgänge definiert.

Werden im Design FlipFlops, Zähler, Schieberegister, usw.verwendet, so werden diese hier definiert und ggf.parametrisiert.

In diesem Block befindet sich die Beschreibung der Schaltung.

Name des Designs

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 29

Listing (dcf.tdf)1 %****************************************************************************%2 %* DCF-Dekodierung (ohne Datum) (in AHDL) mit EPM7128S und 32,768-kHz-Takt *%

3 %* *%4 %* Entwickler: Buchgeher Stefan *%

5 %* Entwicklungsbeginn: 28. Dezember 2004 *% 6 %* Funktionsfaehig seit: 3. Mai 2005 *%

7 %* Letzte Bearbeitung: 15. September 2005 *%8 %****************************************************************************%9

10 %***************** Include-Dateien ******************************************%11 INCLUDE "lpm_counter.inc";

12 INCLUDE "lpm_shiftreg.inc";13

14 15 %***************** Konstanten ***********************************************%16 CONSTANT KONSTDCFLMIN = 28835; % entspricht 880 ms %17 CONSTANT KONSTDCFLMAX = 30147; % entspricht 920 ms %18 CONSTANT KONSTDCFHMIN = 24903; % entspricht 760 ms %19 CONSTANT KONSTDCFHMAX = 27526; % entspricht 840 ms %20 CONSTANT KONSTDCFMINMIN = 57671; % entspricht 1760 ms %21 CONSTANT KONSTDCFMINMAX = 62915; % entspricht 1920 ms %

22 CONSTANT KONSTDCFTIMEOUT = 65400; % Time-Out %23 CONSTANT KONST_ANZ_SR = 36; % 36...0 %

24 25 26 %***************** Definition der Ein- und Ausgaenge ************************%27 SUBDESIGN dcf28 (29 clock_DCF : INPUT; % System-Takt %30

31 reset : INPUT;32

33 inDCF_In : INPUT; % DCFIN %34

35 outSEK_Takt,36 outDCF_Fehler : OUTPUT; % Zustandsanzeige "FEHLER" %

37 outDCF_Sync : OUTPUT; % Zustandsanzeige "SYNC" % 38 39 outDCF_BitFehler, % Zustandsanzeige "?" %40 outDCF_Lo, % Zustandsanzeige "LO" %41 outDCF_Hi : OUTPUT; % Zustandsanzeige "HI" %42

43 outANZEIGE_EN : OUTPUT; % Aktiviert die Anzeige %44

45 outSEK_E[3..0], 46 outSEK_Z[2..0] : OUTPUT; % Sekunden im BCD-Format % 47 48 outMIN_E[3..0],49 outMIN_Z[2..0] : OUTPUT; % Minuten im BCD-Format %50

51 outSTD_E[3..0],52 outSTD_Z[1..0] : OUTPUT; % Stunde im BCD-Format %53 )54

55 56 %***************** Definition der Variablen *********************************%57 VARIABLE58 % D-FlipFlops %59 iFF_DCF_In : DFF; % D-Flipflop zur Synchronisierung des60 DCF-Eingangs %

61 iFF_DCF_Fehler : DFFE;62 iFF_DCF_Sync : DFFE;63 iFF_DCF_Lo : DFFE;

64 iFF_DCF_Hi : DFFE;65 iFF_DCF_BitFehler : DFFE;66

67

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 30

68 % 16-Bit-Zaehler % 69 iZAEHLER_DCF : lpm_counter WITH70 (71 LPM_WIDTH = 16,72 LPM_DIRECTION = "UP"

73 );74

75 % 15-Bit-Zaehler fuer 1-Hz-Takt %76 iZAEHLER_Uhr : lpm_counter WITH

77 (78 LPM_WIDTH = 15,79 LPM_DIRECTION = "UP"80 );

81 82 % Sekunden - Zaehler 0-59 (BCD) %83 iZAEHLER_SEK_E : lpm_counter WITH

84 ( 85 LPM_WIDTH = 4, 86 LPM_DIRECTION = "UP", 87 LPM_MODULUS = 10 88 ); 89 90 iZAEHLER_SEK_Z : lpm_counter WITH 91 ( 92 LPM_WIDTH = 3, 93 LPM_DIRECTION = "UP", 94 LPM_MODULUS = 6 95 );.96 97 % Minuten - Zaehler 0-59 (BCD) % 98 iZAEHLER_MIN_E : lpm_counter WITH 99 (100 LPM_WIDTH = 4,101 LPM_DIRECTION = "UP",102 LPM_MODULUS = 10103 );104105 iZAEHLER_MIN_Z : lpm_counter WITH106 (107 LPM_WIDTH = 3,108 LPM_DIRECTION = "UP",109 LPM_MODULUS = 6110 );111112 % Stunden - Zaehler 0-23 (BCD) %113 iZAEHLER_STD_E : lpm_counter WITH114 (115 LPM_WIDTH = 4,116 LPM_DIRECTION = "UP",117 LPM_MODULUS = 10118 );119120 iZAEHLER_STD_Z : lpm_counter WITH121 (122 LPM_WIDTH = 2,123 LPM_DIRECTION = "UP",124 LPM_MODULUS = 4125 );126127128 % 37-Bit-Schieberegister %129 iSR_DCF : lpm_shiftreg WITH130 (131 LPM_WIDTH = KONST_ANZ_SR + 1132 );133134135 % Zustandsmaschine fuer die DCF-Dekodierung %136 iZM_DCF : MACHINE OF BITS (q[2..0])137 WITH STATES

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 31

138 (139 z0 = B"000",140 z1 = B"001",141 z2 = B"010",142 z3 = B"011",143 z4 = B"100",144 z5 = B"101",145 z6 = B"110",146 z7 = B"111"147 );148149150 %***************** Beginn der Schaltungsbeschreibung ************************%151 BEGIN152 % Synchronisation des DCF-Eingangs mit einem D-Flopflop %153 iFF_DCF_In.clk = clock_DCF;154 iFF_DCF_In.d = inDCF_In;155 iFF_DCF_In.prn = VCC;156 iFF_DCF_In.clrn = VCC;157158 % FlipFlops (Takt, Reset und nicht benoetigte Eingaenge) %159 iFF_DCF_Fehler.clk = clock_DCF;160 iFF_DCF_Fehler.prn = reset;161 iFF_DCF_Fehler.clrn = VCC;162163 iFF_DCF_Sync.clk = clock_DCF;164 iFF_DCF_Sync.clrn = reset;165 iFF_DCF_Sync.prn = VCC;166167 iFF_DCF_Lo.clk = clock_DCF;168 iFF_DCF_lo.clrn = reset;169 iFF_DCF_lo.prn = VCC;170171 iFF_DCF_Hi.clk = clock_DCF;172 iFF_DCF_Hi.clrn = reset;173 iFF_DCF_Hi.prn = VCC;174175 iFF_DCF_BitFehler.clk = clock_DCF;176 iFF_DCF_BitFehler.clrn = reset;177 iFF_DCF_BitFehler.prn = VCC;178179 % Zaehler (Takt) %180 iZAEHLER_DCF.clock = clock_DCF;181 iZAEHLER_Uhr.clock = clock_DCF;182183 iZAEHLER_SEK_E.clock = iZAEHLER_Uhr.q[14];184 iZAEHLER_SEK_Z.clock = !iZAEHLER_SEK_E.q[3];185 iZAEHLER_MIN_E.clock = !iZAEHLER_SEK_Z.q[2];186 iZAEHLER_MIN_Z.clock = !iZAEHLER_MIN_E.q[3];187 iZAEHLER_STD_E.clock = !iZAEHLER_MIN_Z.q[2];188 iZAEHLER_STD_Z.clock = !iZAEHLER_STD_E.q[3];189190191 % Schieberegister (Takt) %192 iSR_DCF.clock = clock_DCF;193194195 % Zustandsmaschine %196 iZM_DCF.clk = clock_DCF;197 iZM_DCF.reset = !reset;198199 CASE iZM_DCF IS200 WHEN z0 => % Ausgangszustand (iZAEHLER_DCF loeschen) %201 iZAEHLER_DCF.aclr = VCC;202 IF iFF_DCF_In.q THEN203 iZM_DCF = z1;204 END IF;205206207 WHEN z1 => % iZAEHLER_DCF freigeben (=starten) %

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 32

208 iZAEHLER_DCF.cnt_en = VCC;209 iZAEHLER_DCF.clk_en = VCC;210 IF !iFF_DCF_In.q THEN211 iZM_DCF = z2;212 ELSIF (iZAEHLER_DCF.q[] >= KONSTDCFTIMEOUT) THEN213 iZM_DCF = z7;214 END IF;215216217 WHEN z2 =>218 IF ((iZAEHLER_DCF.q[] >= KONSTDCFLMIN) &219 (iZAEHLER_DCF.q[] <= KONSTDCFLMAX)) THEN % LOW %220221 iZM_DCF = z3;222223 ELSIF ((iZAEHLER_DCF.q[] >= KONSTDCFHMIN) &224 (iZAEHLER_DCF.q[] <= KONSTDCFHMAX)) THEN % HIGH %225226 iZM_DCF = z4;227228 ELSIF ((iZAEHLER_DCF.q[] >= KONSTDCFMINMIN) &229 (iZAEHLER_DCF.q[] <= KONSTDCFMINMAX)) THEN % Min-Wechsel%230231 IF iFF_DCF_Fehler.q THEN232 iZM_DCF = z6;233 ELSE234 iZM_DCF = z5;235 END IF;236 ELSE237 iZM_DCF = z7; % Fehler %238 END IF;239240241 WHEN z3 => % LOW dem Schieberegister hinzufuegen %242 iSR_DCF.enable = VCC;243244 iFF_DCF_Lo.d = VCC; % iFF_DCF_Lo setzen %245 iFF_DCF_Lo.ena = VCC;246 iFF_DCF_Hi.ena = VCC; % iFF_DCF_Hi loeschen %247 iFF_DCF_BitFehler.ena = VCC; % iFF_BitFehler loeschen %248249 iZM_DCF = z0; % Naechster Zustand %250251252 WHEN z4 => % High dem Schieberegister hinzufuegen %253 iSR_DCF.shiftin = VCC;254 iSR_DCF.enable = VCC;255256 iFF_DCF_Hi.d = VCC; % iFF_DCF_Hi setzen %257 iFF_DCF_Hi.ena = VCC;258 iFF_DCF_Lo.ena = VCC; % iFF_DCF_Lo loeschen %259 iFF_DCF_BitFehler.ena = VCC; % iFF_BitFehler loeschen %260261 iZM_DCF = z0; % Naechster Zustand %262263264 WHEN z5 => % Neue Minute und gueltiges Telegramm %265 iFF_DCF_Sync.d = VCC;266 iFF_DCF_Sync.ena = VCC; % iFF_DCF_Sync setzen %267268 iZAEHLER_Uhr.aclr = VCC; % iZAEHLER_Uhr loeschen %269 iZAEHLER_SEK_E.aclr = VCC; % iZAEHLER_SEK_E loeschen %270 iZAEHLER_SEK_Z.aclr = VCC; % iZAEHLER_SEK_Z loeschen %271 iZAEHLER_MIN_E.aload = VCC; % iZAEHLER_MIN_E laden %272 iZAEHLER_MIN_Z.aload = VCC; % iZAEHLER_MIN_Z laden %273 iZAEHLER_STD_E.aload = VCC; % iZAEHLER_STD_E laden %274 iZAEHLER_STD_Z.aload = VCC; % iZAEHLER_STD_Z laden %275276 iZM_DCF = z0; % Naechster Zustand %277

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 33

278279 WHEN z6 => % iFF_DCF_Fehler loeschen %280 iFF_DCF_Fehler.ena = VCC;281 iZM_DCF = z0; % Naechster Zustand %282283284 WHEN z7 =>285 iFF_DCF_Fehler.d = VCC; % iFF_DCF_Fehler setzen %286 iFF_DCF_Fehler.ena = VCC;287288 iFF_DCF_BitFehler.d = VCC;% iFF_DCF_BitFehler setzen %289 iFF_DCF_BitFehler.ena = VCC;290 iFF_DCF_Lo.ena = VCC; % iFF_DCF_Lo loeschen %291 iFF_DCF_Hi.ena = VCC; % iFF_DCF_Hi loeschen %292293 iZM_DCF = z0; % Naechster Zustand %294 END CASE;295296297 % Schieberegister - Zaehler fuer Uhrzeit und Datum %298 iZAEHLER_MIN_E.data[0] = iSR_DCF.q[36];299 iZAEHLER_MIN_E.data[1] = iSR_DCF.q[35];300 iZAEHLER_MIN_E.data[2] = iSR_DCF.q[34];301 iZAEHLER_MIN_E.data[3] = iSR_DCF.q[33];302 iZAEHLER_MIN_Z.data[0] = iSR_DCF.q[32];303 iZAEHLER_MIN_Z.data[1] = iSR_DCF.q[31];304 iZAEHLER_MIN_Z.data[2] = iSR_DCF.q[30];305306 iZAEHLER_STD_E.data[0] = iSR_DCF.q[28];307 iZAEHLER_STD_E.data[1] = iSR_DCF.q[27];308 iZAEHLER_STD_E.data[2] = iSR_DCF.q[26];309 iZAEHLER_STD_E.data[3] = iSR_DCF.q[25];310 iZAEHLER_STD_Z.data[0] = iSR_DCF.q[24];311 iZAEHLER_STD_Z.data[1] = iSR_DCF.q[23];312 iZAEHLER_STD_Z.aclr = iZAEHLER_STD_Z.q[1] & iZAEHLER_STD_E.q[2];313 iZAEHLER_STD_E.aclr = iZAEHLER_STD_Z.q[1] & iZAEHLER_STD_E.q[2];314315316 % Zaehler Uhr - FF Sync %317 iZAEHLER_Uhr.cnt_en = iFF_DCF_Sync.q;318 iZAEHLER_Uhr.clk_en = iFF_DCF_Sync.q;319320321 % Ausgaenge %322 outDCF_Fehler = iFF_DCF_Fehler.q;323 outSEK_Takt = iZAEHLER_Uhr.q[14];324325 outDCF_Sync = iFF_DCF_Sync.q;326327 outDCF_Lo = iFF_DCF_Lo.q;328 outDCF_Hi = iFF_DCF_Hi.q;329 outDCF_BitFehler = iFF_DCF_BitFehler.q;330331 outSEK_E[] = iZAEHLER_SEK_E.q[];332 outSEK_Z[] = iZAEHLER_SEK_Z.q[];333334 outMIN_E[] = iZAEHLER_MIN_E.q[];335 outMIN_Z[] = iZAEHLER_MIN_Z.q[];336337 outSTD_E[] = iZAEHLER_STD_E.q[];338 outSTD_Z[] = iZAEHLER_STD_Z.q[];339340 outANZEIGE_EN = iFF_DCF_Sync.q;341 END;

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 34

Anmerkungen und Erläuterungen zum Design-File:• Das Design-File sieht wie ein Listing eines z.B. C-Programms aus. Es ist aber zu

beachten, dass es sich hier keinesfalls um ein Programm handelt, welchessequentiell (also Schritt-für-Schritt) abgearbeitet wird. Hier handelt es sich um dieBeschreibung einer Schaltung!

• Die Zeilen 1 bis 8 sind Kommentare und dienen der Kurzbeschreibung der Software,den Namen des Entwicklers und einige zusätzliche Informationen. (Anmerkung:Kommentare befinden sich in AHDL zwischen zwei %-Zeichen, z.B. % Kommentar%)

• In den Zeilen 11 und 12 werden die von ALTERA zur Verfügung gestelltenBibliotheken eingebunden. Hier für die verwendeten Zähler (iZAEHLERxxx) und fürdas Schieberegister (iSR_DCF)

• Im Design werden mehrere Konstanten verwendet. (Hier u.a. zur Unterscheidungzwischen den Low- und High-Bits, einem Minutenwechsel, usw.) Konstanten werdenin AHDL mit dem Schlüsselwort CONSTANT definiert. In den Zeilen 16 bis 23 werdenalle in diesem Design verwendeten Konstanten definiert.

• In den Zeilen 29 bis 52 werden alle Ein- und Ausgänge definiert. Hier lautet dieAHDL-Syntax: Name des Ein- oder Ausgangs : Typ; (Als Typ kannverwendet werden: INPUT (für Eingang), OUTPUT (für Ausgang) oder BIDIR (fürbidirektional).

• Die Zeilen 59 bis 65 definieren die verwendeten FlipFlops. Hier lautet die AHDL-Syntax: Name des FlipFlops : FlipFlop-Typ; (Als FlipFlop-Typen stehenz.B, DFF (D-FlipFlop), DFFE (D-FlipFlop mit Freigabe), SRFF (S-R-FlipFlop), SRFFE(S-R-FlipFlop mit Freigabe), JKFF (J-K-FlipFlop), JKFFE (J-K-FlipFlop mit Freigabe)usw. zur Verfügung)

• Die Zeilen 68 bis 125 definieren die verwendeten Zähler. Hier lautet die AHDL-Syntax: Name des Zählers : lpm_counter WITH ( PARAMETERLISTE );(Die Parameterliste beinhaltet zumindest die Anzahl der Bits (LPM_WIDTH). Weiterskönnen hier Parameter wie die Zählrichtung (LPM_DIRECTION), die obereZählgrenze (LPM_MODULUS), usw. definiert werden. Die obere Zählgrenze ist beidieser Anwendung ganz besonders wichtig. Denn der Zähler iZAEHLER_SEK_Z sollbeispielsweise nur von 0 bis 5 zählen. Daher ist für diesen Parameter der Wert 6notwendig. Der folgende Programmausschnitt (Zeilen 90 bis 95) zeigt die Definitionfür diesen Zähler.

90 iZAEHLER_SEK_Z : lpm_counter WITH91 (92 LPM_WIDTH = 3,93 LPM_DIRECTION = "UP",94 LPM_MODULUS = 695 );

• Die Zeilen 129 bis 132 definieren das verwendete Schieberegister (iSR_DCF). Hierlautet die AHDL-Syntax: Name des Schieberegisters : lpm_shiftregWITH ( PARAMETERLISTE ); (Die Parameterliste beinhaltet zumindest dieAnzahl der Bits (LPM_WIDTH). Weiters können hier Parameter wie z.B. dieSchieberichtung (LPM_DIRECTION), usw. definiert werden.

• Die Zeilen 136 bis 147 definieren die verwendete Zustandsmaschine (iZM_DCF).Hier lautet die AHDL-Syntax: Name der Zustandsmaschine : MACHINE OFBITS (Bitanzahl) WITH STATES (Z0 = 0, Z1 = 1, Z2 = 2 usw. );

• Nun beginnt ab Zeile 151 die Beschreibung des Designs vom Bild 12a.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 35

• Die Zeilen 153 bis156 beschreiben die Eingänge des FlipFlops zur Synchronisierungdes DCF-Eingangs. Dieses FlipFlop hat die Bezeichnung iFF_DCF_In. Dieverschiedenen Eingänge eines Objektes werden folgendermaßen angesprochen:

Objekt.Eingang

(z.B. Dateneingang des FlipFlops zur Synchronisierung: iFF_DCF_in.d oderTakteingang des Sekundentakt-Zählers iZAEHLER_Uhr.clock)

Zurück zum FlipFlop zur Synchronisierung des DCF-Eingangs. Gemäß dem Design(Bild 5.12a) ist der Takteingang dieses Flipflops mit dem Systemtakt verbunden,daher lautet die AHDL-Anweisung:

iFF_DCF_In.clk = clock_DCF; (Zeile 153),

Der Dateneingang ist mit dem DCF-Eingang verbunden, die AHDL-Anweisung lautetdaher:

iFF_DCF_In.d = inDCF_In; (Zeile 154)

Sowohl der Set- als auch der Reset-Eingang dieses FlipFlops sind mit VCCverbunden. Die AHDL-Anweisungen lauten daher:

iFF_DCF_In.prn = VCC; (für Set-Eingang; Zeile 155)iFF_DCF_In.clrn = VCC; (für Reset-Eingang; Zeile 156)

• Die Zeilen 159 bis 177 beschreiben die Eingänge der restlichen FlipFlops, mitAusnahme der Dateneingänge. Die Dateneingänge stammen von der Zustands-maschine (iZM_DCF) und werden an anderer Stelle beschrieben. Der System-Resetstammt aus der Hardwarebeschaltung des CPLDs und ist lowaktiv (siehe auchAbschnitt 3). Lowaktiv sind auch die Set und Reset-Eingänge der FlipFlops, sodassdiese direkt mit dem System-Reset verbunden werden können.

• Die Zeilen 180 bis 188 beschreiben die Verdrahtung der Takteingänge für dieZähler. Die Zähler iZAEHLER_DCF und iZAEHLER_Uhr sind mit dem Systemtakt(clock_DCF) verbunden. In AHDL lautet diese Verbindungen daher

iZAEHLER_DCF.clock = clock_DCF; (Zeile 180)iZAEHLER_Uhr.clock = clock_DCF; (Zeile 181)

Die weiteren Zähler (für die Uhrzeit) sind „hintereinander“ geschaltet, d.h. der Takteines Zählers stammt von einem Ausgang des vorhergehenden Zählers. (siehe Bild5.12a) Weiters muss dieser Ausgang negiert werden. Für die Negierung wird inAHDL ein “!“ verwendet. Somit lautet die AHDL-Anweisung für den Takteingang desZählers iZAEHLER_SEK_Z:

iZAEHLER_SEK_Z.clock = !iZAEHLER_SEK_E.q[3]; (Zeile 184)

Anmerkung: Der Zähler iZAEHLER_SEK_E ist ein 4-bit-Zähler. Das heißt er besitztdaher 4 Ausgänge. Die eckige Klammer gibt an welche der 4 Ausgänge benutztwird, wobei beim Zählen mit 0 begonnen wird. [3] bedeutet daher, dass der vierteAusgang benutzt wird.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 36

• Zeile 192 beschreibt die Verdrahtung des Takteingangs für das Schieberegister. AlsTakt für das Schieberegister wird wieder der Systemtakt verwendet.

• Die Zeilen 196 bis 294 zeigen die Umsetzung der Zustandsmaschine (iZM_DCF). ZuBeginn erfolgen die Verdrahtungen für den Systemtakt (clock_DCF, Zeile 196) undfür den Reset (Zeile 197). Der System-Reset stammt aus der Hardwarebeschaltungdes CPLDs und ist lowaktiv (siehe auch Abschnitt 3). Der Reset-Eingang einerZustandsmaschine ist aber highaktiv. D.h. als Reset-Eingang muss der invertierteSystemreset verwendet werden (Zeile 197).

Die Realisierung einer Zustandsmaschine sieht in AHDL wie folgt aus:

CASE Name der Zustandsmaschine ISWHEN Zustand 0 =>

Anweisung1;Anweisung2;…Anweisungn;Übergang zum nächsten Zustand;

WHEN Zustand 1 =>Anweisung1;Anweisung2;…Anweisungn;Übergang zum nächsten Zustand;

WHEN Zustand 2 =>…WHEN Zustand n =>

END CASE;

• Die Zeilen 298 bis 311 zeigen die Umsetzung der Verbindungen zwischen denAusgängen des Schieberegisters (iSR_DCF) und den zu ladenden Zählern für die(mitlaufende) Uhr.

• Die Zeilen 312 und 313 zeigen die Realisierung des UND-Gatters beim Stunden-Zähler (siehe Bild 4.10 und Bild 4.12a). Eine UND-Verknüpfung erfolgt in AHDL mitdem „&“-Symbol. Tabelle 5.1. zeigt die wichtigsten logischen Verknüpfungen:

Verknüpfung SymbolUND &ODER #EXOR $NICHT !

Tabelle 5.1.: logische Verknüpfungen

• Die Zeilen 317 und 318 zeigen die Realisierung der Freigabe für den Sekunden-Takt-Zähler (iZAEHLER_Uhr)

• Die Zeilen 322 bis 340 zeigen die Verdrahtungen aller verwendeten CPLD-Ausgänge. Anmerkung: eine leere, eckige Klammer bedeutet dass diese Anweisungfür alle Ausgänge dieses Namens gilt. Die Zeile 331

outSEK_E[] = iZAEHLER_SEK_E.q[];

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 37

bedeutet daher dass die vier Ausgänge outSEK_E[3..0] mit den vier Ausgängen desZählers iZAEHLER_SEK_E verbunden werden. Diese Anweisung ersetzt daherfolgende vier Anweisungen:

outSEK_E[0] = iZAEHLER_SEK_E.q[0];outSEK_E[1] = iZAEHLER_SEK_E.q[1];outSEK_E[2] = iZAEHLER_SEK_E.q[2];outSEK_E[3] = iZAEHLER_SEK_E.q[3];

Wichtig: Die Indizes von outSEK_E und iZAEHLER_SEK_E müssen natürlich gleichgroß sein. Ansonst tritt beim Kompilieren eine Fehlermeldung aus.

• Die Anweisung END; in Zeile 341 bedeutet das Ende der AHDL-Datei.

Das folgende Bild zeigt einen Ausschnitt des soeben beschriebenen AHDL-Files(Listings)

Bild 5.11.: AHDL-Design-File (Ausschnitt)

Man erkennt sehr gut die farblichen Unterschiede, was die Arbeit und die Fehlersucheerheblich erleichtert. Die folgende Tabelle zeigt einen Ausschnitt• Blau: AHDL-Schlüsselwörter• Schwarz: Name von Elementen (FlipFlops, Zähler, usw.), Ein- und

Ausgängen, Zuweisungen• Grün: Kommentare• Hellgrau: Zeilennummern

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 38

Schritt 3: Systemtakt definierenNach anklicken von „Assignments“ und „Timing Settings…“ gelangt man zum folgendenBild (Bild 5.12).

Bild 5.12.: Timing Requirements & Options

Unter „Category“ den Eintrag „Timing Requirements & Options” auswählen (1)

Unter “Clock Settings” die Option “Settings for individual clock signals” auswählen (2)und die Taste “Clocks…” anklicken.

Bild 5.13.: Eingabebox “Clocks”

Taste “New…”

1

2

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 39

Bild 5.14.: Eingabebox “New Clocks Settings”

Clock settings name: ein beliebiger NameApplies to node: clock_DCF (Wichtig: Dieser Name muss mit dem Systemtakt im AHDL-File übereinstimmen!)Required fmax: Hier gibt man die Taktfrequenz mit der richtigen Einheit an. Hier, beidiesem Projekt handelt es sich um einen 32768-Hz-Takt (Siehe auch Abschnitt 3)Duty cycle (%): Hier lässt man den Standardwert von 50.

Taste „OK“

Bild 5.15.: Eingabebox “Clocks” mit ausgewähltem Systemtakt

Taste „OK“ (2 mal)

Schritt 4: Erste KompilierungNun erfolgt zum ersten Mal eine Kompilierung des Designs. Dies ist jetzt schonnotwendig, damit später (im Schritt 5) allen Ein- und Ausgängen die richtigenPinnummern zugewiesen werden können. Weiters wir beim Kompilieren (wie auch beianderen Programmiersprachen) das Design auf syntaktische Fehler überprüft.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 40

Bild 5.16.: Kompilierung (Start)

Eine Kompilierung wird mit dem violetten Dreieck in der Symbolleiste (siehe Bild 5.16)gestartet.

Bild 5.17.: Kompilierung

Bild 5.17. zeigt die Entwicklungsumgebung während der Kompilierung. Der Bereich„Status“ (1) zeigt den Fortschritt an und der Bereich 2 gibt Auskunft was gemachtwurde. Hier erscheinen auch Warnungen und (syntaktische) Fehler. Wird ein solcherFehler von der Entwicklungsumgebung entdeckt, so wird die Kompilierungabgebrochen. Der Fehler muss natürlich gefunden und behoben werden, gefolgt von

2

1

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 41

einer neuen Kompilierung. Dieser Vorgang muss natürlich so oft wiederholt werden biskeine Fehler mehr auftreten. Warnungen können natürlich schon auftreten. Diesesollten aber nie völlig ignoriert werden. Es sollte immer überprüft werden, ob dieseWarnung „gewollt“ ist, oder ob beim Designentwurf etwas übersehen wurde. Was ichdamit meine, wird hoffentlich gleich klar.

Wurde die Kompilierung erfolgreich durchgeführt, so erscheint der folgende Hinweis(Bild 5.18).

Bild 5.18.: Box „Kompilierung erfolgreich“

Hier, bei diesem Projekt trat beim Kompilieren eine Warnung auf. Bild 5.19. gibtAuskunft über diese Warnung(en) (1). Weiters eine kleine Statistik über die Anzahl derbenötigten Makrozellen und Pins (2).

Bild 5.19.: Kompilierung (Endergebnis)

Da beim Kompilieren eine Warnung aufgetreten ist, sollte diese nun überprüft werden.Bei den Warnungen handelt es sich hier um den Hinweis, dass ein so genannter „RippleCounter“ erzeugt wurde. Dies wurde aber beabsichtigt, da wir ja die freilaufende Uhrtatsächlich als „Ripple Counter“ aufgebaut haben (siehe Bild 4.12a). Diese Warnungkann also ignoriert werden.

1

2

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 42

Schritt 5: Pinnummern zuweisenNach erfolgreicher erster Kompilierung können nun die Pinnummern den Ein- undAusgängen zugeordnet werden. Für diesen Schritt gibt es in Quartus mehrereMöglichkeiten. Den „Pin-Planer“ möchte ich hier vorstellen. Dieser ist gerade bei„kleineren“ CPLDs (so wie hier) sehr übersichtlich.

Nach anklicken von „Assignments“ und „Pin Planer“ gelangt man zum folgenden Bild(Bild 5.20).

Bild 5.20.: Pin Planer

Zur besseren Übersicht sollte man hier in den „Vollbildmodus“ übergehen (1)

Vorgehensweise:1. Aus der Liste „Unassigned Pins“ wählt man einen Pin („Node Name“) durch

einfaches anklicken aus.2. Mit gedrückter Maustaste zieht man diesen nun auf den gewünschten Pin des

CPLDs (mittlerer Bildbereich). Der Mauszeiger zeigt an, ob an dieser Stelle einPin zugeordnet werden kann.

3. Maustaste loslassen. In der Liste „Assigned Pins“ erscheint nun dieser Ein- oderAusgang mit der dazu ausgewählten Pinnummer. Zusätzlich wird dieser in dergrafischen Ansicht (Bildmitte) durch einen ausgefüllten Kreis dargestellt. (Bild5.21. zeigt dies für den Ausgang „outANZEIGE_EN“ ,Pin 16)

1

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 43

Bild 5.21.: Pin Planer

Sind alle Ein- und Ausgänge zugeordnet, so sollte dies dem Bild 5.22 entsprechen.

Bild 5.22.: Pin Planer

Nun sollte wieder in die „gewohnte Ansicht“ zurückgekehrt werden (1)

Schritt 6: Zweite KompilierungZum Abschluss muss die Kompilierung wiederholt werden. (gemäß Schritt 4)

2

1

1

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 44

6. SimulationDer nächste Schritt, nach dem Entwurf und der Eingabe des Designs, ist die Simulation.Dabei wird überprüft ob das Design die geforderten Aufgaben erfüllt.

Das Grundprinzip der Simulation ist, dass man an den Eingängen des Designs sogenannte Eingangsvektoren anlegt, die auch in der Realität auftreten. DiesenEingangsvektor nennt man auch Stimuli. Aus diesen Eingangsvektoren ermittelt dieEntwicklungsumgebung alle Ausgänge des Designs und zeigt diese grafisch an. Darauslässt sich dann erkennen, ob das erstellte Design auch wirklich die gefordertenAufgaben erfüllt.

Für die Simulation gibt es in Quartus mehrere Möglichkeiten. Ich möchte hier einegrafische Methode mit Hilfe eines „Vector Waveform File“ (.vwf) vorstellen.

Schritt 1: Ein Vector Waveform File für dieses ProjekterzeugenDurch anklicken von „File“ und „New…“ wird ein neues File geöffnet. Hier soll nun ein„Vector Waveform File“ geöffnet werden. Dies befindet sich unter „Other Files“ (sieheBild 6.1.)

Bild 6.1.: Waveform File erzeugen

Nach anklicken der „OK“-Taste zeigt Bild 6.2. den „neuen“ Arbeitsbereich. Im neuenFenster erfolgt nun die Eingabe der Eingangsvektoren.

1

2

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 45

Bild 6.2.: Waveform File erzeugen

Ein nützliches Werkzeug ist der so genannte „Node Finder“. Dieser wird wie folgtaufgerufen: „View“ à „Utility Windows“ à „Node Finder“. Man schiebt ihn am Bestenneben den „Projekt Navigator“. Mit Hilfe dieses „Node Finder“ können ganz bequem diezu simulierenden Ein- und Ausgänge ausgewählt werden. Im Filter sollte „Design Entry(all Names)“ ausgewählt werden. Damit können „Komponenten“ innerhalb einesDesigns simuliert werden. Ein Klick auf die Taste „List“ zeigt nun alle auszuwählenden„Komponenten“ (siehe Bild 6.3).

Bild 6.3.: Waveform File erzeugen

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 46

Wichtig: Damit der „Node Finder“ wie der Name schon sagt etwas findet, muss dasDesign kompiliert werden. (Dies erfolgte schon, und ist daher jetzt nicht notwendig!)

Als erstes definieren wir das zu simulierende Zeitfenster. Fürs erste interessiere ichmich ob die Low- und High-Impulse des DCF-Datenstroms richtig ausgewertet werden.Daher ist zunächst mal ein Zeitfenster von, sagen wir mal, 5 Sekunden notwendig.Diese Einstellung erfolgt mit „Edit“ (ganz oben in der Symbolleiste)è „End Time…“

Bild 6.4.: Waveform File erzeugen

Nach der Bestätigung („OK“) sollte der ganz rechte Bereich so eingestellt werden, dassder gesamte Zeitbereich sichtbar ist. Dazu mit der Maus in diesen Bereich klicken àrechte Maustasteà „Zoom“à „Fit in Window“ anklicken.

Als nächsten Schritt wollen wir nun alle Eingangsvektoren definieren. Als erstes ziehenwir „clock_DCF“ mit gedrückter Maustaste vom „Node Finder“ in das Feld rechts nebenden „Node Finder“. Dies ist ja unser Systemtakt, welchen wir schon an anderer Stelledefiniert haben (siehe Schritt 3 im Abschnitt 5). Diesen Takt machen wir nun sichtbar,indem wir auf „clock_DCF“ klickenà rechte Maustasteà „Value“à „Clock…“

Bild 6.5.: Waveform File erzeugen

In dieser Box wählen wir die Option „Clock settings“ (Bild 6.5.) und anschließend „OK“.Nun erscheint ein schwarzer Balken. Das ist schon okay. Denn wir haben hier einenSystemtakt von 32768 Hz. Bei einem Zeitfenster von 5 Sekunden ergeben sich somit 5x 32768 = 163840 Takte. Diese können vom Bildschirm und vom menschlichen Augenicht mehr als einzelne Taktimpulse aufgelöst werden. Es erscheint daher nur mehr einBalken.

Als nächstes definieren wir den Reset-Eingang. Zunächst ziehen wir diesen wieder mitgedrückter Maustaste vom „Node Finder“ in das Feld rechts neben den „Node Finder“.Hier, bei diesem Projekt ergibt sich der Reset aus der Hardware. Beim Einschalten derBetriebsspannung ist der Reset für kurze Zeit Low. Danach, bis zum Ausschalten High.Wir müssen daher für die Simulation dieses Verhalten nachbilden. Dies geschieht amEinfachsten indem man mit der Maus ein Rechteck an der gewünschten Stelle aufzieht.Dieses Rechteck wird hellblau dargestellt, (1) im Bild 6.6. Ein Klick auf „Forcing High“(Symbol in der Toolbar zwischen „Project Navigator“ und „Node Finder“) ändert denhellblauen Bereich in einen High-Pegel (2) im Bild 6.6.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 47

Bild 6.6.: Waveform File erzeugen

Nun zum etwas aufwendigeren Teil. Als nächstes wollen wir den Eingang inDCF_In(also den auszuwertenden DCF-Datenstrom) erstellen. Bild 6.7. zeigt dazu ein Beispiel.Im Ruhezustand ist dieser Eingang High. Nach etwa einer Sekunde erfolgt für etwa100ms ein Low-Impuls. Nach etwa zwei Sekunden ein 200ms langer Low-Impuls undnach drei Sekunden wieder ein 100ms langer Low-Impuls. Zwischen der dritten undvierten Sekunde soll ein kurzer Störimpuls auftreten und nach vier Sekunden wieder ein200ms langer Low-Impuls (siehe Bild 6.7.)

Bild 6.7.: Waveform File erzeugen

12

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 48

Als letztes müssen wir noch die Ausgänge angeben, die uns für diese Simulationinteressieren. Interessant sind hier zunächst nur die Ausgänge outDCF_Lo, outDCF_Hiund outDCF_BitFehler. Interessant ist darüber hinaus auch das Verhalten derZustandsmaschine (iZM_DCF). Bild 6.8. zeigt die so entstandenen „Eingangsvektoren“.Zur besseren Übersicht werden die Ausgänge „zaunartig“ dargestellt.

Bild 6.8.: Waveform File erzeugen

Abschließend muss diese Datei noch gespeichert werden. Ich persönlich lege für dieEingangsvektoren (Stimuli) in einen eigenen Ordner namens „Stimuli“ im Projektordnerab. Also „File“ à “Save“ oder „Save As“ à Bild 6.9. (Wichtig ist hier der Dateityp:„Vector Waveform file“). Nennen wir diese Datei „dcf1“à Taste „Speichern“

Bild 6.9.: Waveform File speichern

Schritt 2: Simulator-EinstellungenNach anklicken von „Assignments“ und „Settings“ gelangt man zum folgenden Bild (Bild6.10).

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 49

Bild 6.10.: Simulator-Einstellungen

In der linken Liste „Simulator“ auswählen (1). Als „Simulation input“ das im Schritt 1erzeugte Waveform File („dcf1.vwf“) (2).Altera empfiehlt weiters die Option „Run simulation until all vector stimuli are used“,„Automatically add pins to simulation output waveforms” und “Simulation coveragereporting” (siehe Bild 6.10.)

Schritt 3: Simulation beginnenDie Simulation wird mit dem Symbol „Start Simulation“ (gemäß Bild 6.11.) gestartet.

Bild 6.11.: Simulation starten

Die Dauer der Simulation hängt davon ab, wie groß die „End-Time“ (siehe Bild 6.4.)gewählt wurde, und natürlich auch von der Leistungsfähigkeit des verwendetenComputers. Hier, dauert die Simulation bei mir ca. 2 Minuten

Konnte die Simulation erfolgreich durchgeführt werden, erscheint ein Hinweis gemäßBild 6.12. Konnte die Simulation nicht erfolgreich durchgeführt werden, so müssennatürlich die Fehler gesucht und behoben werden!

Bild 6.12.: Erfolgreiche Simulation

1

2

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 50

Schritt 4: Simulationsergebnis analysieren

Bild 6.13.: Simulationsergebnis

Im Bild 6.13. erkennt man sehr gut, wie der Eingang (also der DCF-Datenstrom,inDCF_in) ausgewertet wird. Der Ausgang „outDCF_Lo“ wird logisch „1“ nach einemkurzen Impuls (ca. 100ms) und der nächsten steigenden Flanke vom Eingang(inDCF_In), und der Ausgang „outDCF_Hi“ wird logisch „1“ nach einem langen Impuls(ca. 200ms) und der nächsten steigenden Flanke vom Eingang (inDCF_In). Bei einem„ungültigen“ Impuls des Eingangs wird der Ausgang „outDCF_BitFehler“ logisch „1“.

Die erste Simulation war also erfolgreich. Als nächstes wollen wir einen Zeitbereich vonca. 80 Sekunden simulieren, damit wir sehen wie das Design ein komplettes DCF-Telegramm einließt, und ob dann die freilaufende Uhr zu starten beginnt.

Schritt 5: Zweite SimulationWir erzeugen zunächst ein zweites Vector Waveform File. Wir wiederholen also dieSchritte 1 bis 4. Dieses File speichern wir unter „dcf2.vwf“ im Unterordner „Stimuli“. Als„End Time“ geben wir hier 80 Sekunden ein.

Bild 6.14 zeigt dieses Vector Waveform File. Man erkennt bei ca. 10 Sekunden und beica. 70 Sekunden, dass hier keine Impulse vorhanden sind. Diese sind dieMinutenmarken (gemäß dem DCF-Protokoll). Die kurzen und langen Impulse wurden sogewählt, dass beim Simulieren eine sinnvolle Uhrzeit und ein sinnvolles Datumzustande kommen.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 51

Bild 6.14.: Zweite Simulation

Diese Simulation wird etwas mehr Zeit in Anspruch nehmen. Bei mir dauerte dieseSimulation ca. 28 Minuten!

Bild 6.15. zeigt das Simulationsergebnis.

Bild 6.15.: Ergebnis der zweiten Simulation

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 52

Das Simulationsergebnis lässt sich mit der Taste „Full Screen“ (siehe Bild 6.15) zurbesseren Übersicht vergrößern. Bild 6.16. zeigt dasselbe Simulationsergebnis invergrößerter Darstellung.

Bild 6.16.: Ergebnis der zweiten Simulation (vergrößert)

Die Simulation zeigt sehr schön das Verhalten des Designs. Zu Beginn ist der Ausgang„outDCF_Fehler“ gesetzt. Bei Sekunde 10 bleibt die Absenkung des DCF-Datenstroms(Eingang inDCF_In) aus. Es erfolgt also ein Minutenwechsel. Der Ausgang„outDCF_Fehler“ wird zurückgesetzt (gemäß dem Zustandsdiagramm, Bild 4.12b). Nunwerden alle kurzen und langen Impulse des Eingangs („inDCF_In“) ausgewertet. DieAusgänge „outDCF_Lo“ und „outDCF_Hi“ zeigen dies sehr schön an. Interessant wirdes bei Sekunde 70. Hier erfolgt der nächste Minutenwechsel. Da bei den vorher-gehenden 60 Sekunden kein Fehler aufgetreten ist, muss nun die Uhrzeit an denentsprechenden Ausgängen ausgegeben werden. Der Wert für Stunden-Zehner beträgt„1“, für Stunden-Einer beträgt er „9“, für den Minuten-Zähler beträgt er „4“ und derMinuten-Einer-Wert beträgt „7“. Es ergibt sich also eine Uhrzeit von 19:47 Uhr. Weitersmuss auch die Anzeige (Ausgang outANZEIGE_EN) aktiviert werden. DerStatusausgang „outDCF_Sync“ geht ebenfalls von low auf high. Weiters erkennt mansehr gut einen Sekundentakt und der Wert für die Sekunden-Einer-Stelle beginnt mitjedem Sekundentakt hoch zu zählen.

Ist man an weiteren Details interessiert, so kann man natürlich auch Ausschnittegenauer betrachten (Zoom-Funktion).

Die Funktionalität des hier gewählten Designs wird hier also prinzipiell erfüllt. Natürlichkann man noch weitere, größere Zeitfenster (z. B. 2 Minuten) simulieren.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 53

7. ProgrammierenNach erfolgreicher Simulation kann nun das Design in das CPLD geladen werden.Diesen Vorgang bezeichnet man auch als Programmieren.

Zum Programmieren ist neben der Hardware (also der bestückten Platine, gemäßAbschnitt 8) auch noch ein so genanntes Download-Kabel notwendig. Ich verwende hierden so genannten „Byte-Blaster“. Dieser wird von der Herstellerfirma des CPLDs (alsoAltera) hergestellt. Natürlich kann auch ein Nachbau (z.B. aus dem Internet) verwendetwerden. Es muss nur sichergestellt sein, dass der Nachbau funktionell dem originalen„Byte-Blaster“ entspricht. Das Download-Kabel verbindet also den PC (mittels parallelerSchnittstelle) mit der Zielhardware (siehe auch Abschnitt 3).Es ist zu beachten, dass das Download-Kabel richtig an die Zielhardware (hier die DCF-Uhr) angeschlossen wird. Dazu ist Pin 1 der Programmier-Schnittstelle (JTAG-Schnitt-stelle) extra gekennzeichnet.

Die Programmieroberfläche wird mit dem Symbol „Programmer“ gestartet (Bild 7.1.)

Bild 7.1.: Programmieren

Darauf hin öffnet sich die Programmierumgebung gemäß Bild 7.2.

Bild 7.2.: Programmieren

Folgende Einstellungen sollten dabei überprüft werden:• ByteBlasterMV (LPT1)• Mode: JTAG• File: dcf.pof• Device: EPM7128SL84

12

3

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 54

• Program/Configure: Häkchen• Verify: Häckchen• Blank Check: Häkchen

Sind alle diese Einstellungen korrekt, so kann die Programmierung mit der Taste „Start“begonnen werden. Wichtig: Beim Programmieren muss die DCF-Uhr eingeschaltet sein.Ansonst treten die beiden Fehlermeldungen

“Error: JTAG ID code specified in JEDEC STAPL Format File does not match anyvalid JTAG ID codes for device”

und“Error: Operation failed”

auf.

Entwickeln mit CPLDs (am Beispiel einer DCF-Uhr)

Seite 55

8. NachbauanleitungDieser Abschnitt beschreibt den Nachbau der DCF-Uhr. Das Herstellen der Platine wirdhier nicht beschrieben, da hier jeder seine eigene Methode besitzt, außerdem werdenindustriell gefertigte Platinen (auch in der Einzelfertigung und auch für einePrivatperson) immer günstiger, so dass die Eigenfertigung immer mehr abnimmt.

Schritt 1: Platinen herstellenZu diesem Zweck sind im Anhang A die Layouts zu diesem Projekt abgedruckt, welcheüblicherweise seitenverkehrt sind.Selbstverständlich können eigene Platinen entworfen werden, die den eigenenAnforderungen entsprechen.

Achtung: Wird eine eigene Platine entworfen, so sollte folgendes beachtet werden: Eshat sich gezeigt, dass die Kupferfläche unter der Antenne (des DCF-Empfängers)entfernt werden muss. Mit der Kupferfläche war kein DCF-Empfang möglich, bzw. dieAntenne konnte nicht direkt auf der Platine montiert werden. Im Bild 8.1 ist zu erkennen,dass ein erheblicher Teil auf beiden Seiten freigeätzt wurde.

Schritt 2: Platinen bestückenDie Elektronik dieses Projektes wurde auf zwei Platinen aufgeteilt. Das Bestücken einerPlatine ist erst dann sinnvoll, wenn alle für diese Platine benötigten Bauteile vorhandensind. Es sollten generell nur erstklassige und neuwertige Bauteile verwendet werden.Auf Bauteile aus ausgeschlachteten Geräten sollte grundsätzlich verzichtet werden, daihre Funktionalität nicht gewährleistet ist, und eine unnötige Fehlersuche dadurchvermieden werden kann.

Weiters sollte ausreichend Platz und vor allem ausreichend Zeit für die Bestückung derPlatinen vorhanden sein.