Informatik II 7. von-Neumann-Rechner · von-Neumann-Rechner die ALU operiert auf Registerbreite (8,...

Transcript of Informatik II 7. von-Neumann-Rechner · von-Neumann-Rechner die ALU operiert auf Registerbreite (8,...

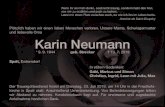

Informatik II

Rainer Schrader

Institut für Informatik

17. November 2014

1 / 88

7. von-Neumann-Rechner

2 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

3 / 88

von-Neumann-Rechner

• die aus den 1940er Jahren stammende von-Neumann-Architektur hat bis heuteihre konzeptionelle Bedeutung nicht verloren

• demgemäß besteht ein Rechner aus

• einer Zentraleinheit (Central Processing Unit): CPU• einem Speicher• einer Ein-/Ausgabe (input/output) Einheit: I/O• sowie Verbindungen zwischen diesen Einheiten: Adressbus und Datenbus

Speicher(ROM, RAM)

CPUCentral

ProcessingUnit

I / OInput

Output

Datenbus

Adressbus

4 / 88

von-Neumann-Rechner

Aufgaben:

• CPU: Ablaufsteuerung, Ausführung von Befehlen

• Speicher: Programme und Daten als Bitfolgen

• I/O: Verbindung zur Außenwelt

• die Struktur des Rechners ist unabhängig von einem speziellen zu lösendenProblem

• sein Verhalten wird allein von dem via I/O in den Speicher geschriebenenProgramm und den dort ebenfalls befindlichen Daten bestimmt

• der Speicher nimmt Programme und Daten in Speicherzellen fester Länge auf,die einzeln adressiert werden können

5 / 88

von-Neumann-Rechner

Struktur einer CPU

DekodiererSteuerwerk

IR

MAR PC

ALU

MBR

MR AL

Datenprozessor Befehlsprozessor

Adressbus

Datenbus

CPU

• mit DatenprozessorALU (Arithmetic Logical Unit): RechenwerkA: Akkumulator-Register (Akku)

L: Flag-Register (z.B. für Additions-Überträge, Ergebnis ist 0, ist negativ)MR: Multiplikationsregister (Erweiterung von A)MBR: (Memory Buffer Register): Puffer für Speicherinhalte

6 / 88

von-Neumann-Rechner

Struktur einer CPU

DekodiererSteuerwerk

IR

MAR PC

ALU

MBR

MR AL

Datenprozessor Befehlsprozessor

Adressbus

Datenbus

CPU

• und BefehlsprozessorIR: Instruktionsregister: aktuell zu bearbeitender BefehlMAR: (Memory Address Register): SpeicheradressePC: (Program Counter): Adresse des nächsten Befehls

7 / 88

von-Neumann-Rechner

• zu jedem Zeitpunkt

• führt die CPU genau einen Befehl aus und• dieser kann höchstens einen Operandensatz bearbeiten „Single

Instruction - Single Data (SISD)“

• Speicherworte können Daten, Befehle oder Adressen sein

• Aufgaben der ALU• Durchführung von arithmetischen oder logischen Operationen:

• 0-Adress-Befehle (z.B. Komplementieren des Akkus) oder• 1-Adress-Befehle (z.B. A← A + MBR)• 2-Adress-Befehle (z.B. A← A + B)

• (in realen Computern gibt es auch 3-Adress-Befehle)

8 / 88

von-Neumann-Rechner

• die ALU operiert auf Registerbreite (8, 16, 32 oder 64 Bits)• die logischen Operationen werden komponentenweise durchgeführt• ebenso die arithmetischen Operationen, wobei Überträge weitergeleitet werden• es reicht daher, die ALU bitweise zu beschreiben

eine (sehr) einfache ALU:

Stufe n− 1Cn−1Cn

Bn−1 An−1

Fn−1

. . . . . .

Bi Ai

Fi

Ci+1 Ci

Stufe i Stufe 0

B0 A0

C1 C0

F0

Funktionsselektor S = (S2, S1, S0,M)

9 / 88

von-Neumann-Rechner

eine (sehr) einfache ALU:

Stufe n− 1Cn−1Cn

Bn−1 An−1

Fn−1

. . . . . .

Bi Ai

Fi

Ci+1 Ci

Stufe i Stufe 0

B0 A0

C1 C0

F0

Funktionsselektor S = (S2, S1, S0,M)

dabei bedeutet:

• Ai ,Bi Inputbits• Fi Ergebnisbit, Ci carry-Bit• M Umschalter (0 = logisch, 1 = arithmetisch)• S0,S1,S2 Funktionsselektoren

10 / 88

von-Neumann-Rechner

Eine (sehr) einfache ALU

Stufe i :

S1

Bi Ai

M

Ci

Fi Ci+1

x

yz

w

∨

∧ ∧ ∧∧

∨

⊕

⊕

∧ ∧

S0 S2

11 / 88

von-Neumann-Rechner

Effekte der Selektoren:

S2 x0 01 Ai

S1 S0 y0 0 00 1 Bi1 0 Bi1 1 1

M z0 01 Ci

logische Operationenarithmetische Operationen

S1

Bi Ai

M

Ci

Fi Ci+1

x

yz

w

∨

∧ ∧ ∧∧

∨

⊕

⊕

∧ ∧

S0 S2

12 / 88

von-Neumann-Rechner

S1

Bi

MCi

Fi

Ci+1

x

y

z

w

∨

∧

∧

∧

∧∨ ⊕ ⊕

∧

∧

S0

S2

Ai

Boolesche Funktionen

FiS2 S1 S0 x y w M = 0 M = 1 Ci+1 für M = 10 0 0 0 0 0 0 Ci 00 0 1 0 Bi Bi Bi Bi ⊕ Ci Bi Ci0 1 0 0 Bi Bi Bi Bi ⊕ Ci Bi Ci0 1 1 0 1 1 1 Ci Ci1 0 0 Ai 0 Ai Ai Ai ⊕ Ci Ai Ci1 0 1 Ai Bi Ai ⊕ Bi Ai ⊕ Bi Ai ⊕ Bi ⊕ Ci Ai Bi ∨ (Ai ⊕ Bi )Ci1 1 0 Ai Bi Ai ⊕ Bi Ai ⊕ Bi Ai ⊕ Bi ⊕ Ci Ai Bi ∨ (Ai ⊕ Bi )Ci1 1 1 Ai 1 Ai Ai Ai ⊕ Ci Ai ∨ Ci

13 / 88

von-Neumann-Rechner

Zusammensetzen der Stufen

A = (An−1,An−2, . . . ,A0)

B = (Bn−1,Bn−2, . . . ,B0)

C = (Cn−1,Cn−2, . . . ,C0)

F = (Fn−1,Fn−2, . . . ,F0)

14 / 88

von-Neumann-Rechner

S1

Bi

MCi

Fi

Ci+1

x

y

z

w

∨

∧

∧

∧

∧∨ ⊕ ⊕

∧

∧

S0

S2

Ai

Logische Mikro-Operationen der ALU (bitweise ausgeführt)

M S2 S1 S0 F Beschreibung0 0 0 0 0 setze alle Bits auf Null0 0 0 1 B übertrage B0 0 1 0 B komplementiere B (1-Kpl)0 0 1 1 1 setze alle Bits auf Eins0 1 0 0 A übertrage A0 1 0 1 A ⊕ B exklusives Oder0 1 1 0 A ⊕ B0 1 1 1 A komplementiere A (1-Kpl)

15 / 88

von-Neumann-Rechner

S1

Bi

MCi

Fi

Ci+1

x

y

z

w

∨

∧

∧

∧

∧∨ ⊕ ⊕

∧

∧

S0

S2

Ai

arithmetische Mikro-Operationen der ALU

M S2 S1 S0 C0 F Beschreibung1 0 0 1 1 B + 1 inkrementiere B1 0 1 0 1 B + 1 2-Kompl. von B1 1 0 0 1 A + 1 inkrementiere A1 1 0 1 0 A + B Addition1 1 1 0 0 A + B Subtraktion A − B (1-Kompl.)1 1 1 0 1 A + B + 1 Subtraktion A − B (2-Kompl.)1 1 1 1 0 A − 1 dekrementiere A

16 / 88

von-Neumann-Rechner

Beispiel 7.1

Erläuterung zu:

M S2 S1 S0 C0 F1 1 1 1 0 A − 1 Dekrementiere A

S1

Bi Ai

M

Ci

Fi Ci+1

x

yz

w

∨

∧ ∧ ∧∧

∨

⊕

⊕

∧ ∧

S0 S2aus dem Schaltplan für Stufe i entnehmen wir

M = 1S2 S1 S0 x y w Fi Ci+1

1 1 1 Ai 1 Ai Ai ⊕ Ci Ai ∨ Ci

insbesondere ist y = 1

17 / 88

von-Neumann-Rechner

M = 1S2 S1 S0 x y w Fi Ci+1

1 1 1 Ai 1 Ai Ai ⊕ Ci Ai ∨ Ci

• es ist y = 1

• die Subtraktion entspricht der Addition des 2-Komplements, also

A − 1 → A + 2-Kompl. von 1 = A + 11 · · · 1• z.B.

0110 0110−0001 → +1111

(1)0101

18 / 88

von-Neumann-Rechner

M = 0 M = 1S2 S1 S0 x y w Fi Fi Ci+1

1 1 1 Ai 1 Ai Ai Ai ⊕ Ci Ai ∨ Ci

• Subtraktion um 1 entspricht der Addition von 1 . . . 1

• zur Erinnerung: für die Summation gilt

si = xi ⊕ yi ⊕ ci

ci+1 = xi yi ∨ ((xi ⊕ yi )ci )

• in der obigen Notation und speziell für yi = 1 folgt

Fi = Ai ⊕ 1⊕ Ci = Ai ⊕ Ci

Ci+1 = (Ai ∧ 1) ∨ ((Ai ⊕ 1) ∧ Ci ) = Ai ∨ (Ai ∧ Ci ) = Ai ∨ Ci

• d.h. der Schaltplan dekrementiert A wie behauptet

19 / 88

von-Neumann-Rechner

Ablauf der Befehlsverarbeitung in der CPU

• Interpretations- und Fetch-Phase:

• bringe Inhalt von PC in das memory address register (MAR)

• bringe Inhalt einer Adresse aus dem Speicher über das memory bufferregister (MBR) in das instruction register (IR)

• der Befehlsdekodierer interpretiert den Befehl

• erkennt, um welchen Befehlstyp es sich handelt

• benötigte Operanden werden über das MAR und MBR zur Verfügunggestellt.

• Execution Phase:• führe den Befehl aus

• aktualisiere PC: PC ← PC + 1 oder PC ← Sprungadresse

• initiiere nächste Fetch-Phase

20 / 88

von-Neumann-Rechner

• in der Realität ist es oft komplizierter

• z.B. müssen Adressberechnungen aufgrund indirekter Adressierungdurchgeführt werden

• bei heutigen Rechnern bestimmt die Kommunikation zwischen CPU undSpeicher wesentlich die Geschwindigkeit (von-Neumannscher Flaschenhals)

21 / 88

von-Neumann-Rechner

Beispiel 7.2 (stark vereinfacht)

• Befehl im IR ist ADD x („Addiere 〈x 〉 zum Akku-Inhalt“)

• jedes Register hat Kontrolleitungen:

• in: übernimm neuen Wert• out: übergib Inhalt• incr: inkrementiere Inhalt um 1

• der Assemblerbefehl ADD x (Assembler wird später behandelt) entsprichtdem Maschinenbefehl

Code für ADD x

22 / 88

von-Neumann-Rechner

• die Dekodierung erfolgt im Steuerwerk, das die entsprechenden Signale setzt• jede Zeile entspricht Signalen in einem Taktzyklus:

FETCH

1 S3; PC-out; MAR-in2 S3; MBR-in; MEM(MAR)-out3 S3; IR-in; MBR-out4 S3; PC-incr; MAR-in (Übernahme von der Adresse von x )5 S3; MBR-in; MEM(MAR)-out (lade x )

EXECUTE{

6 S2; S0; M (Addition)

23 / 88

von-Neumann-Rechner

• das Steuerwerk stößt für jeden Befehl ein Mikroprogramm an

• hier:

PC PC PC MBR MBR MAR MAR IR IRM S3 S2 S1 S0 out in incr out in out in out in …

1 1 1 12 1 13 1 1 14 1 1 15 1 16 1 0 1 1

24 / 88

von-Neumann-Rechner

• die Befehls-Mikroprogramme sind in einem ROM gespeichert

• Prinzip:

Instruktionscode Adressteil

DEKODIERER Auswahl des ersten Mikrobefehls

. . .

. . .

IR

MIKROPROGRAMM-SPEICHER

25 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

26 / 88

von-Neumann-Rechner

• Mikrobefehle bestehen aus Bitfolgen, die geeignet interpretiert werden

• sie erlauben einen direkten Zugriff auf die Hardware

• dazu muss jedoch jeder einzelne Schalter und Schaltweg richtig gesetzt werden

• daher ist das Erstellen von Mikroprogrammen extrem mühsam

• die nächste Abstraktionsebene besteht aus Maschinenbefehlen, die:

• keine Sicht mehr auf einzelne Schaltwerke (Datenprozessor,Adressprozessor, Busse) haben

• auf Ebene der CPU, Register und Speicher agieren• über komplexere Operationen verfügen

27 / 88

von-Neumann-Rechner

• jeder Maschinenbefehl besteht selbst wieder aus einer Bitfolge

• diese Bitfolge wird in ein Mikroprogramm übersetzt und ausgeführt

• zur besseren Verständlichkeit von Maschinenbefehlen werden mnemotechnischeVarianten verwendet

• damit werden Maschinenbefehle zu Assemblerbefehlen

• die Rückübersetzung von Assemblerprogrammen in Maschinenprogramme wirddurch einen Assembler geleistet

28 / 88

von-Neumann-Rechner

Vorteile der Assemblerprogrammierung

• im Vergleich zu Maschinenprogrammierung:

• symbolische Namen für Befehle (ADD, SUB, …)• symbolische Namen für Speicherplätze

• im Vergleich zu Programmieren in einer Hochsprache:

• Zugriff auf alle Einzelheiten der Maschine (z.B. Testen eines Overflowbits),d.h. im Prinzip sind effiziente Programme möglich.

Felder eines Assemblerbefehls

• Label• Operation• Operanden• Kommentar

29 / 88

von-Neumann-Rechner

Beispiele für Assemblerbefehle:

ADD A,B addiere den Inhalt von Register B zu dem von A

MOV A, [4711] kopiere den Inhalt von Register Aauf die Speicherstelle [4711]

Label Befehl setze Label im Programm

DEC A verringere den Inhalt von Register A um 1

JNZ Label falls die letzte Operation 6= 0, springe zu Label

AND A, B bilde das bitweise ∧∧∧ der Register A und B

XOR A, A lösche das Register A auf 0

30 / 88

von-Neumann-Rechner

Beispiel 7.3

Code-Fragment für n = i + j + k auf INTEL Pentium

Label Operation Operanden KommentarFORMUL: MOV EAX, I ; Lade I nach EAX

ADD EAX, J ; Addiere J zu EAXADD EAX, K ; Addiere K zu EAXMOV N, EAX ; Speichere I+J+K in N...

I: DD 2 ; Reserv. 4 Bytes initial. mit 2J: DD 3 ; Reserv. 4 Bytes initial. mit 3K: DD 4 ; Reserv. 4 Bytes initial. mit 4N: DD 0 ; Reserv. 4 Bytes initial. mit 0

31 / 88

von-Neumann-Rechner

Assemblerprogramme erlauben strukturiertes Programmieren:

• durch Makros• durch Prozeduren

• wie üblich durch Deklaration einer Prozedur• und durch eine CALL-Anweisung

32 / 88

von-Neumann-Rechner

Makros

• Makros erlauben eine kompakte Definition sich wiederholenderInstruktionssequenzen, z.B.:

(a)

MOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBX.....MOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBX

=⇒

(b)

SWAP MACROMOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBXEND MACRO

SWAP....SWAP

33 / 88

von-Neumann-Rechner

(a)

MOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBX.....MOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBX

=⇒

(b)

SWAP MACROMOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBXEND MACRO

SWAP....SWAP

• mit der Definition eines Makros wird der zugehörige Text in einer Makro-Tabelleabgespeichert

• bei Benutzung des Makros wird jeder Aufruf durch eine Kopie des Makros ersetzt

• dies geschieht alles während der Assemblierung, d.h. z.B. (a) und(b) produzieren exakt den gleichen Code

34 / 88

von-Neumann-Rechner

Makros können auch Parameter haben, z.B.:

(a)

MOV EAX, PMOV EBX, QMOV Q, EAXMOV P, EBX.....MOV EAX, RMOV EBX, SMOV S, EAXMOV R, EBX

=⇒

(b)

CHANGE MACRO P1, P2MOV EAX, P1MOV EBX, P2MOV P2, EAXMOV P1, EBXEND MACRO

CHANGE P, Q....CHANGE R, S

35 / 88

von-Neumann-Rechner

Laden und Binden (loading and linking)

• Prozeduren werden getrennt übersetzt

• der Code wird in den Hauptspeicher geladen

• dort zusammengebunden

• danach wird der Code ausgeführt

Binden

Quellprozedur 2

Quellprozedur 3

Quellprozedur 1

Übersetzer

Objektmodul 1

Objektmodul 2

Objektmodul 3

Binder

36 / 88

von-Neumann-Rechner

Beispiel 7.4

JUMP TO 200

MOVE P TO X

CALL B

JUMP TO 300

0

100

200

300

400

500

600

700

800

900

1000

MOVE Q TO X

CALL C

JUMP TO 2001100

1200

1300

1400

1500

1600

1700

1800

1900

MOVE R TO X

CALL D

JUMP TO 200

MOVE S TO X

500

400

0

100

200

300

400

0

100

200

300

0

100

200

300

0

100

200

300 Obj

ektm

odul

AO

bjek

tmod

ulB

Obj

ektm

odul

CO

bjek

tmod

ulD

JUMP TO 300

MOVE P TO X

CALL 500

JUMP TO 800

0

100

200

300

400

500

600

700

800

900

1000

MOVE Q TO X

CALL 1100

JUMP TO 13001100

1200

1300

1400

1500

1600

1700

1800

1900

MOVE R TO X

CALL 1600

JUMP TO 1800

MOVE S TO X

500

400

0

100

200

300

400

0

100

200

300

0

100

200

300

0

100

200

300

nach Laden nach Binden

Diesen Vorgang nennt man „Relocation“37 / 88

von-Neumann-Rechner

Aktionen

(1) Konstruktion einer Tabelle aller Objektmodule mit ihren Längen

(2) Zuordnung einer Code-Adresse zu jedem Objektmodul

(3) Addition der Startadresse jedes Moduls zu den Speicheradressen im Modul(„relocation constant“)

(4) Ersetzung der Adressen aller externen Referenzen

38 / 88

von-Neumann-Rechner

Dynamische Relokation

• In „multitasking“ Betriebssystemen (UNIX, Windows, . . .)

• unterbrechen• auf Platte schreiben...• von Platte lesen (idR an einer anderen Adresse als vorher)• weitermachen

• Lösung im INTEL Pentium

• das „run time relocation register“ CS• enthält die Startadresse des momentan laufenden Moduls• Addition von CS zu allen Speicheradressen durch die Hardware

39 / 88

von-Neumann-Rechner

es existieren unterschiedliche Konzepte von Maschinenbefehlen:

CISC- vs. RISC-Architekturen

• CISC (complex instruction set computer)

• RISC (reduced instruction set computer)

• Anfang der 80er Jahre Umschwung zu RISC-Architekturen

• Reaktion auf Wandel in Hardwaregegebenheiten

• bis dahin war der Arbeitsspeicher ein entscheidender Engpass

• langsam• klein• teuer

• durch Caches und schnelleren, größeren, billigerem SpeicherParadigmenwechsel

40 / 88

von-Neumann-Rechner

CISC (complex instruction set computer)

• Ziele:

• Programme sollten kurz gehalten werden können (Speicher knapp)• die Anzahl der Speicherzugriffe zum Laden von Instruktionen sollte klein

sein (Speicher langsam)• Kompatibilität des Binärcodes, Unabhängigkeit von Hardware

• komplexe und viele Maschinenbefehle

• Maschinenbefehle stoßen umfangreiche Mikroprogramme an

• Befehlsformate variieren stark (z.B. zwischen 1 - 32 Byte)

• benutzen wenige Register

• Speicher ist adressierbar, d.h. Operationen greifen direkt auf Speicher zu

• Beispiele: /360, /370 (IBM), VAX (DEC), 80x86 (Intel) bis 80386

41 / 88

von-Neumann-Rechner

RISC (reduced instruction set computer)

• enge Kopplung zwischen Compilern und Hardware (d.h. Verzicht aufKompatibilität)

• wenige, einfache Maschinenbefehle

• Maschinenbefehle entsprechen möglichst einem Mikrobefehl

• Maschinenbefehle möglichst in einem Takt ausführbar

• wenige Befehlsformate, möglichst gleicher Länge

• benutzen viele Mehrzweckregister

• Speicherzugriffe nur über LOAD- und STORE-Befehle

• Beschleunigung durch „Pipelining“(wird später erläutert)

• Beispiele: PowerPC (IBM und Motorola), Sparc (Sun), Itanium (Intel)

42 / 88

von-Neumann-Rechner

Varianten und Erweiterungen

• MMX-Befehle

• Spezialfall von „ single instruction multiple data“(SIMD)

• bei Audio-, Video- oder Graphikdaten können oft verschiedene Daten mit einemBefehl bearbeitet werden

• Beispiel: Pentium (Intel)

• VLIW (very long instruction word)

• Spezialfall von „multiple instruction multiple data“(MIMD)

• mehrere Operationen werden zu Einheiten zusammengefasst und parallelbearbeitet

• Beispiele: Itanium (Intel)

43 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

44 / 88

von-Neumann-Rechner

Speicher

• zur Speicherung werden zwei verschiedene Konzepte verwendet:

• ROM (read only memory): Festwertspeicher „nur lesen“• RAM (random access memory) mit wahlfreiem Zugriff auf jede

Speicherzelle zum Lesen und Schreiben

• ROMs werden häufig eingesetzt, um System-Funktionen aufzunehmen. Siewurden weiterentwickelt als

• PROM (programmable ROM): sie können durch Anlegen von externenSpannungen programmiert („gebrannt“) werden

• EPROM (erasable PROMS): durch UV-Belichtung ist die Programmierungwieder löschbar

• EEPROM (electrically erasable PROMS)

45 / 88

von-Neumann-Rechner

RAM wird in verschiedenen Techniken hergestellt:

• DRAM (dynamic RAM):

• Speicherstellen bestehen nur aus einem Transistor und einemKondensator

• verliert seine Ladung, insbesondere beim Auslesen, und muss daherregelmäßig aufgefrischt werden

• SRAM (static RAM):

• jede Speicherstelle besteht aus einem Flip-Flop und hält seine Ladung• ist schneller und teurer als DRAM, findet Verwendung in Caches

• SDRAM (synchronous DRAM):

• wie DRAM, mit Speicherpartitionierung• gleichzeitiges Lesen eines Block und Auffrischung eines anderen

• DDRAM (double (data) DRAM):

• wie DRAM, Zugriffe erfolgen sowohl über steigende und fallende Flanken

46 / 88

von-Neumann-Rechner

Speicher

RAM-Bausteine werden üblicherweise als Hierarchie nach zunehmender Zugriffszeitund abnehmenden Kosten implementiert:

• Register (SRAM)• Cache:

• enthält eine „Umgebung“ der gerade benötigten Daten• im 100 KB- bis MB-Bereich (SRAM)• eventuell mehrere Cache-Ebenen

• L1-Cache: prozessorintegriert, auf Prozessorchip• L2-Cache: auf Prozessorchip oder -platine mit direkter Verbindung

und Ansteuerung• L3-Cache: auf Motherboard

• Hauptspeicher: im MB- bis TB-Bereich ((DRAM), auch Terabyte = 250 Bytes)

• auf der letzten Hierarchiestufe folgen Hintergrundspeicher:

• Platten, Bänder, Disketten, CDs, DVD’s• Kapazitäten im GB-, TB- und PB-Bereich

47 / 88

Rechnerarchitektur

Busse

Busse stellen die Datenverbindungen zwischen einzelnen Teilen des Rechners her:

• prozessorinterne Busse: Verbindungen zwischen Registern, Steuer- undRechenwerk, L1-Cache und zu externen Bussen

• Prozessorbus: Kopplung zwischen Prozessor und L2-Cache bzw. Koprozessoren

• Prozessor-Speicherbus: zur Datenübertragung zwischen Prozessor undSpeicher

• Systembus: zum Anschluss von Peripherie mit hohen Datenraten• E/A-Bus: zum Anschluss von E/A-Geräten

• evtl. jeweils getrennt nach Aufgaben:

• Datenbus, Adressbus, Steuerbus, Kontrollbus zur Synchronisation

• evtl. Einrichtungen zur Steuerung des Zugriffs auf einen Bus

48 / 88

von-Neumann-Rechner

Ein-/Ausgabeeinheiten

In unserem Konzept kontrolliert die CPU den Speicherzugriff. Daraus ergibt sich u. U.:

• die CPU ist beschäftigt, während ein E/A-Gerät Daten übertragen möchte

• langsame I/O-Geräte blockieren die schnelle CPU

• Ausweg: Endgeräte werden mit zusätzlicher „Intelligenz” ausgestattet

• ein Controller bedient eines oder mehrere Endgeräte

• er verfügt über einen Zwischenspeicher und über Datenleitungen zu denEndgeräten, der CPU und dem Speicher

E/A-Gerät Speicher

E/A-Controller Steuersignale

Daten

49 / 88

von-Neumann-Rechner

Ablauf zum Datenaustausch

• ein Prozess setzt einen I/O-Befehl ab

• die CPU unterbricht den Prozess und markiert ihn als „hold”

• die CPU sendet Kontrollblöcke an den Controller und startet einen anderenProzess

• die Kontrollblöcke enthalten Angaben über Speicheradressen und Datenvolumen

• der Controller puffert die Kontrollblöcke, wenn nötig

• er arbeitet die Aufträge nach geeigneten Strategien ab

• ist ein Auftrag erledigt, sendet er ein „Interrupt”-Signal an die CPU

• die CPU setzt den zugehörigen Prozess auf „wait”

Die Controller übernehmen häufig als I/O-Prozessoren Konvertierungen (intern/extern)und Paritychecks.

50 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

51 / 88

von-Neumann-Rechner

Die Kommunikation zwischen CPU und Speicher bestimmt wesentlich dieGeschwindigkeit ( von-Neumannscher Flaschenhals)

Ausweg: Parallelität

• Differenzierung zwischen Befehlen und Daten, getrennte Busse, getrennteSpeicher, getrennte Caches

• verstärkte Nutzung von parallelen Abläufen (u.a. Controller)

• Mehrprozessorsysteme, Parallelrechner, verteilte Systeme

52 / 88

von-Neumann-Rechner

Ebenen der Parallelität

• Bitebenenparallelität: Verarbeitung ganzer Wörter√

• Befehlsebenenparallelität: parallele Abarbeitung von Befehlen in einemProzessor

• Quasiparallelität: „parallele” Abarbeitung von Threads oder Prozessen aufeinem Prozessor

• Prozessorparallelität: Verwendung mehrerer Prozessoren oder Systeme

53 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

• Pipelining• Parallelrechner• alternative Rechnerkonzepte

54 / 88

von-Neumann-Rechner

nochmal klassische Abarbeitung von Instruktionen:

• Control Unit (CU): bearbeitet die nächste anstehende Instruktion:• holt Befehl• dekodiert Befehl• übergibt die Steuerung an die Memory Unit

• Memory Units (MU): lädt Operanden• berechnet Adressen• lädt Daten in Register• übergibt die Steuerung an die ALU

• Arithmetic Logical Unit (ALU):• führt Operationen aus• übergibt die Steuerung an die MU

• Memory Units (MU): lädt Operanden• berechnet Zieladressen• speichert Ergebnis in Speicher• übergibt die Steuerung an die CU

Alternative: Neuorganisation der sequentiellen Abarbeitung von Befehlsfolgen

55 / 88

von-Neumann-Rechner

Pipelining

• die Idee ist die gleiche wie bei der Fließbandproduktion:

• zerlege den Prozess in Teilprozesse, die etwa gleich lang sind und die vonspeziellen Prozessoren taktsynchron bearbeitet werden.

Beispiel 7.5

• sei M1 ein Rechner, der aus einer ALU, einem Register, einemBefehlsdekodierer besteht

• wir wollen auf M1 eine Folge von n Operationen der Form R = R ◦ xausführen

• dabei sei ◦ eine arithmetische/logische Operation, die den Inhalt von R mitdem Inhalt der Speicherstelle x verknüpft und wieder in R ablegt

• die sequentielle Abfolge sieht dann wie grob folgt aus:

56 / 88

von-Neumann-Rechner

repeat Hardware Takte(1) lade den Befehl Register 1(2) dekodiere Befehl Befehlsdekodierer 1(3) lade Operand Register 1(4) führe Befehl aus ALU 1

until letzte Instruktion

• daraus ergeben sich 4n Takte für n Operationen

• die Maschine M2 enthalte zwei Register: R1 enthalte Instruktionen, R2 enthältDaten

Alu

Register

Register

Befehlsdekodierer

I I I I1 2 3 4

• nach drei Takten liegt mit jedem folgenden Takt ein Ergebnis an• somit benötigt M2 nur n + 3 Takte.

57 / 88

von-Neumann-Rechner

Beispiel 7.6

Addition von Gleitkommazahlen

(1) Vergleich der Exponenten

(2) Exponentenausgleich

(3) Addieren

(4) Normalisieren

58 / 88

von-Neumann-Rechner

Allgemein :

• der Prozess P wird in k Teilprozesse P1, . . . ,Pk zerlegt

• jeder Teilprozess Pi kann auf einer Funktionseinheit Fi bearbeitet werden

• jeder Prozess wird sequentiell von F1, . . . ,Fk bearbeitet, wobei unterUmständen das Ergebnis von Fi an Fi+1 übergeben wird

• verschiedene Teilprozesse zweier Prozesse können gleichzeitig arbeiten

• alle Teilprozesse benötigen möglichst gleiche Zeitdauer

benötigte Zeit: k − 1 + nvorher: k · n

}Beschleunigungsfaktor: kn

k−1+n ; k

59 / 88

von-Neumann-Rechner

Vektorrechner (SIMD)

• bis zu k (z.B. k = 64, k = 128) Komponenten eines Vektors werdengleichzeitig bearbeitet.

• Idee:• funktionale Teile beziehungsweise Pipelines der ALU werden k -fach

installiert.

• Vektorregister: k -fache Länge

• längere Vektoren werden in Blöcke der Länge k zerlegt.

60 / 88

von-Neumann-Rechner

Beispiel 7.7

Addition von 2 Vektoren A = B + C

• seien A,B,C Vektoren der Länge n,• die Elemente B1 + C1, . . . ,Bk + Ck werden gleichzeitig addiert• auf A1, . . . ,Ak abgespeichert,• danach die Elemente Bk+1 + Ck+1, . . . ,B2k + C2k

• usw.

• Bei einigen Dialekten von Programmiersprachen können Vektoren wie Variablenangesprochen werden,

• etwa A = B + C , wobei A,B,C als Vektoren definiert sind

61 / 88

von-Neumann-Rechner

• genauer: die k Elemente werden nicht zeitsynchron bearbeitet, sondern leichtzeitversetzt (um etwa 1 Takt verschoben)

• zusätzlich entstehen setup-Zeiten, die länger sind als bei Skalar-Befehlen

• damit ergibt sich das folgende Bild:

S

S

S

E1

E2

E3

E1

E2

E3

S

• und den folgenden typischen zeitlichen Verlauf:

n

t

• ; Verlängerung bei kleinen n.

62 / 88

von-Neumann-Rechner

Verkettung (Chaining)

• seien A,B,C Vektoren der Länge n.• die Befehlsfolge

(1) for i = 1 to n(2) A(i) = (A(i) + B(i))C(i)(3) end for

• kann in zwei Vektorbefehle umgewandelt werden: A = A + B undA = AC (komponentenweise)

63 / 88

von-Neumann-Rechner

• wir zerlegen den Prozess in folgende Teilprozesse:Zeit

t1 transferiere Daten zu Addierpipeline 1add berechne Summe in Addierpipeline 6t2 transferiere Ergebnis nach A 1t3 transferiere Daten zu Multiplikationspipeline 1mult berechne Produkt in Multiplikationspipeline 7t4 transferiere Ergebnis nach A 1

• Im zeitlichen Verlauf ergibt sich folgendes Verhalten:

t4t1 t2Add Multt3

• Der Vorgang benötigt somit 7 + k + 8 + k = 15 + 2k Takte.

64 / 88

von-Neumann-Rechner

• Verkettung (chaining) ermöglicht es, den Output der ersten Pipeline direkt zumInput der zweiten Pipeline zu machen.

• Die zwei Befehle werden also als ein einziger aufgefasst:

t4t3t2Add Multt1

• Chaining benötigt nur noch 16 + k Takte.

65 / 88

von-Neumann-Rechner

Superskalare Architektur

• paralleler Betrieb von Pipelines

• Differenzierung in ganzzahlige und Gleitpunktoperationen, Adressberechnungenund Speicherzugriffe

• gegenwärtig bis zu 10 Pipelines in einem Prozessor

66 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

• Pipelining• Parallelrechner• alternative Rechnerkonzepte

67 / 88

von-Neumann-Rechner

Rechnerorganisation

• wir haben uns bisher mit einem einfachen Aufbau beschäftigt

CPU

Speicher

• sie findet sich in klassischen PCs, Workstations und Mainframes

68 / 88

von-Neumann-Rechner

• daneben existieren parallele Versionen• die wichtigsten sind:• SIMD (Single Instruction - Multiple Data)

. . .

. . . CPU n

Speicher 1

CPU 1 CPU 2

Speicher nSpeicher 2

macht dasselbe

Kommunikationsnetzwerk

CPUJede aktive

• eine Instruktion wird auf n Prozessoren mit unterschiedlichen Datenausgeführt(→ Datenparallelität)

• z.B. Connection-Maschine (bis 1990, wurde dann durch MIMD Architekturabgelöst), Cell Processor der Playstation-3

69 / 88

von-Neumann-Rechner

Beispiel 7.8

• x86-Prozessoren mit SSE (Streaming SIMD Extension)

• 128-Bit Register für z.B. vier 32-Bit Gleitkommazahlen• Ausführung von arithmetischen Operationen gleichzeitig für 4 Werte

a1, a2, a3, a4

SIMD EinheitInstruktion: ADDPS

b1, b2, b3, b4

a1 + b1, a2 + b2, a3 + b3, a4 + b4

70 / 88

von-Neumann-Rechner

Beispiel 7.9 (Graphikprozessoren)

• früher: festprogrammierte Funktionalität

• ab 2001: kleine Shader-Programme für erweiterte Funktionalität

• Ab 2003: komplexere Programme möglich

⇒ erste Implementierung von Nicht-Graphikalgorithmen für Graphikkarten

• heute: relativ frei programmierbar über Schnittstellen (wie OpenCL, CUDA,Stream SDK)

⇒ General-Purpose computation on Graphics Processing Units (GPGPU)

71 / 88

von-Neumann-Rechner

Beispiel 7.9 (Graphikprozessoren)

• Vorteile: hohe Rechenleistung, schneller Speicher, niedriger Preis

• Nachteil: Algorithmen müssen parallelisiert und stark an die Architekturangepasst werden

• Beispiel: NVIDIA’s Fermi Architektur (2010)

• 512 Kerne organisiert in 16 Multiprozessoren (mit 32 Kernen)• theoretische Leistungen für 32-bit Gleitkommazahlen: > 1 TFLOP/s

(Billionen Gleitkommazahl-Operationen pro Sekunde)• Speicherbandbreite ca. 170 GByte

72 / 88

von-Neumann-Rechner

Beispiel 7.9 (Graphikprozessoren)

• Ausführung von Instruktionen auf einem Multiprozessor in sog. Warps.• alle Kerne führen die aktuelle Instruktion des Warps mit den ihnen zugewiesenen

Daten aus (SIMD-Prinzip).

Instruktion: ai + bi

. . .

Kern 1 Kern 2 Kern n. . .

a1 + b1 a2 + b2 an + bn

73 / 88

von-Neumann-Rechner

Beispiel 7.9 (Graphikprozessoren)

• bedingte Sprünge (if-Anweisungen) möglich

• aber Probleme bei z.B.:

if ai > 0 then ai + bi else ai − bi

• Instruktionspfad divergiert:

• einzelne Kerne müssen ai + bi ausführen,• andere aber ai − bi

• Lösung: Sequentielle Ausführung von ai + bi und ai − bi⇒ weniger Durchsatz, da doppelte Zeit benötigt wird.

74 / 88

von-Neumann-Rechner

• MISD (Multiple Instruction - Single Data)

• auf einem Datensatz werden gleichzeitig verschiedene Operationen ausgeführt

• nicht in kommerziellen Rechnern umgesetzt

• MIMD (Multiple Instruction - Multiple Data)

• unabhängige CPUs mit gemeinsamem Speicher und/oder dediziertem Speicher

. . .

Speicher

CPU 1 CPU 2 CPU n

CPUsunabhängige

75 / 88

von-Neumann-Rechner

• in Mehrkernprozessoren, z.B.:

• AMD Athlon, Opteron, Phenom• Intel Xeon, Itanium

• mehrere getrennte Prozessoren• getrennte L1- und L2-Caches• u.U. gemeinsame L3-Cache und Busse

76 / 88

von-Neumann-Rechner

• z.B. in Cheops: 841 Knoten (u.a. verschiedene Xeon-Varianten), 9712 Kerne,35,5 TByte Arbeitsspeicher,

am RRZK seit November 2010

Quelle: RRZK Uni Köln

77 / 88

von-Neumann-Rechner

• es gibt aber auch einige wenige Maschinen mit massiver Parallelität undmehreren 1000 Prozessoren

• z.B. Earth Simulator (5120 Prozessoren), BlueGene (16250 Prozessoren)

• z.B. Tianhe-2 (32.000 Prozessoren + 48.000 Co-Prozessoren)

• z.B. JUQUEEN Forschungszentrum Jülich: 28,672 Prozessoren, 458.752 Kerne,448 Terabyte Hausptspeicher

Quelle: FZ Jülich78 / 88

von-Neumann-Rechner

Parallelrechner

• mehrere (evtl. auch unabhängig voneinander zu betreibende) Prozessoren• eventuell ein Masterprozessor• eng gekoppelt• sowohl eindeutig zugeordnete als auch gemeinsame Speicher (distributed oder

shared memory)• Kommunikation über gemeinsame Speicher, Punkt-zu-Punkt-Verbindungen oder

Busse

79 / 88

von-Neumann-Rechner

Parallelrechner

Zwei Extreme (shared memory / distributed memory):

P

P

P

P

Netzwerk

Speicher

I/O

Speicher

Speicher

Speicher

und

Speicher

Speicher

Speicher

I/O

I/O

I/O

Speicher

I/OP

P

P

P

Netzwerk

80 / 88

von-Neumann-Rechner

• Ziel: ein Job soll schneller bearbeitet werden, indem er auf verschiedeneProzessoren aufgeteilt wird

• Speedup: parallele Zeitsequentielle Zeit

• der Geschwindigkeitszuwachs durch den Einsatz von k Prozessoren kannhöchstens k betragen

• (Ausnahmen: verteiltes Suchen, Cache-Effekte durch Verteilung der Daten)• im allgemeinen entstehen folgende Probleme:

• Zeitverlust durch Overhead (Synchronisation, Kontrolle, etc.)• Zeitverlust durch Kommunikation• Effizienzverlust durch unbalancierte Auslastung

• im Extremfall kann eine Erhöhung der Prozessorzahl zu einer Verlängerung derBearbeitungszeit führen

• theoretische Analysen beziehen sich meist auf dieses Modell (PRAM)• problematisch ist hier die Auflösung von Schreibkollisionen

81 / 88

von-Neumann-Rechner

verteilte Systeme

• unabhängige, über ein Netz kommunizierende Systeme• ohne zentrale Steuerung• lose gekoppelt• wirkt für Nutzer möglichst wie ein Rechner (Transparenz)• erweiterbar um weitere Systeme• möglichst mit Lastausgleichsmechanismen

Transparenz:• der Name einer Ressource ist für alle Rechner gleich• der Zugriff auf lokale und entfernte Ressourcen ist gleich• der Nutzer sieht i.A. nicht, auf welchem Rechner er arbeitet

82 / 88

von-Neumann-Rechner

grid computing• gemeinsame Nutzung gemeinsamer Ressourcen

• keine zentrale Steuerung

cloud computing

• Trennung von Anbieter und Nutzer

• IT-Infrastruktur wird als Dienstleistung angeboten

• hochskalierbar, zentral verwaltet

• stellt Hardware, Betriebssysteme, Anwendungssoftware bis zu komplettenProzessen bereit

83 / 88

von-Neumann-Rechner

Gliederung

• Konzept• Assembler• Komponenten• Parallelität

• Pipelining• Parallelrechner• alternative Rechnerkonzepte

84 / 88

von-Neumann-Rechner

Klassifizierung von parallelen Architekturen

• es existieren verschiedene Ansätze für parallele Architekturen• bis auf die erste Architektur befinden sich alle noch im Experimentier- bzw.

Konzeptstadium.

von-Neumann-Architekturen• klassische, kontrollgesteuerte Rechner, die auf verschiedene Weisen gekoppelt

sind.

Datenflussarchitektur• Programminstruktionen werden direkt ausgeführt, sobald die Operanden zur

Verfügung stehen (unabhängig von der Instruktionsreihenfolge)

85 / 88

von-Neumann-Rechner

Beispiel 7.10

• als Teil eines Programms sei z auszurechnen, wobei z gegeben ist durchz = (x + y )(x − y )

• dann kann z berechnet werden, sobald die Werte von x und y bekannt sind

• zur Umsetzung dieser Architektur muss der Datenfluss kontrolliert werden

• dies wird mittels Datenflussgraphen versucht

• befinden sich heute noch im Experimentierstadium

86 / 88

von-Neumann-Rechner

Reduktionsmaschinen

• im Unterschied zu den datengetriebenen Datenflussarchitekturen gehen dieReduktionsmaschinen anforderungsgetrieben vor

• Programme werden als geschachtelte Anwendungen von Funktionen aufArgumente augefasst

• eine Reduktionsmaschine führt eine solche Funktionsauswertung erst danndurch, wenn ihr Ergebnis von der nächst höheren Ebene der Schachtelungangefordert wird

• dabei können unabhängige Teile parallel ausgeführt werden

87 / 88

von-Neumann-Rechner

Quantencomputer

• Versuch, Berechnungen mittels Spinsystemen durchzuführen

• eher noch Theorie, wenige Experimente

• Details evtl. am Schluss der Vorlesung

DNA-Computing

• der Versuch, Berechnungen mittels biochemischer Reaktionen durchzuführen

• als Rechner eher Theorie, als Speicher potentielle Anwendung

• Details am evtl. Schluss der Vorlesung

88 / 88