lsi-11

Transcript of lsi-11

-

8/14/2019 lsi-11

1/5

----------------------------------------------------------------| || || Digital Equipment Corporation || || L SSSSS III 1 1 || L S S I 11 11 || L S I 1 1 |

| L SSSSS I XXX 1 1 || L S I 1 1 || L S S I 1 1 || LLLLLLL SSSSS III 111 111 || || LSI-11 MICROPROCESSOR Instruction Set Summary || || || || || || || |

| || || || || || ||XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX||XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX||XXXXX X XXX XXX XXXXXXXX XXX XXX XX XXXX XXXXXXXX XXX XXX||XXXXX X XXXXXXXX XXXXXXXX XXXXXXXX XX XXXX XXXXXXXX XXX XXX||XX X XXX XXX XX XX XXX XXX X XXX XX XX XXX XXX||X XX X XXX XXX X XX X XXX XXX XX XXXX XXXXX X XXX XXX||X XX X XXX XXX X XX X XXX XXX XX XXXX XX X XXX XXX|

|X XX X XXX XXX X XX X XXX XXX XX XXXX X XX X XXX XXX||XX X XXX XXX XX X XXX XXX XXX XX XX X XXX XXX||XXXXXXXX XXXXXXXX XXXXX X XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX||XXXXXXXX XXXXXXXX XX XX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX||XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX|| || || || || || || || |

| || || || || || || || || || || |

-

8/14/2019 lsi-11

2/5

| || || || || || || || |

| ||Written by Jonathan Bowen || Programming Research Group || Oxford University Computing Laboratory || 8-11 Keble Road || Oxford OX1 3QD || England || || Tel +44-865-273840 || ||Created August 1981 ||Updated April 1985 ||Issue 1.1 Copyright (C) J.P.Bowen 1985|

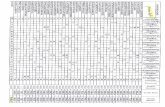

--------------------------------------------------------------------------------------------------------------------------------|Mnemonic |Opcode|NZVC|Description |Notes ||---------+------+----+--------------------------+-------------||ADCb d |B055DD|****|Add Carry |d=d+C ||ADD s,d |06SSDD|****|Add |d=s+d ||ASH s,r |072RSS|****|Arithmetic Shift |r=r*2^s (EIS)||ASHC s,r |073RSS|****|Arithmetic Shift Combined | (EIS)||ASLb d |B063DD|****|Arithmetic Shift Left |d=d*2 ||ASRb d |B062DD|****|Arithmetic Shift Right |d=d/2 ||BCC a |1030XX|----|Branch if Carry Clear |If C=0 ||BCS a |1034XX|----|Branch if Carry Set |If C=1 ||BEQ a |0014XX|----|Branch if Equal |If Z=0 |

|BGE a |0020XX|----|Branch if Greater or Equal|If NxV=0 ||BGT a |0030XX|----|Branch if Greater Than |If Zv{NxV}=0 ||BICb s,d |B4SSDD|**0-|Bit Clear |d=d&{~s} ||BISb s,d |B5SSDD|**0-|Bit Set (OR) |d=dvs ||BITb s,d |B3SSDD|**0-|Bit Test (AND) |d&s ||BHI a |1010XX|----|Branch if Higher |If CvZ=0 ||BHIS a |1030XX|----|Branch if Higher or Same |If C=0 ||BLE a |0034XX|----|Branch if Less or Equal |If Zv{NxV}=1 ||BLT a |0024XX|----|Branch if Less Than |If NxV=1 ||BLO a |1034XX|----|Branch if Lower |If C=1 ||BLOS a |1014XX|----|Branch if Lower or Same |If CvZ=1 ||BMI a |1004XX|----|Branch if Minus |If N=1 ||BNE a |0010XX|----|Branch if Not Equal |If Z=1 |

|BPL a |1000XX|----|Branch if Plus |If N=0 ||BPT |000003|----|Breakpoint Trap |Vector at 14 ||BR a |0004XX|----|Branch |PC=PC+2*XX ||BVC a |1020XX|----|Branch if Overflow Clear |If V=0 ||BVS a |1024XX|----|Branch if Overflow Set |If V=1 ||CALL d |0047DD|----|Call subroutine | (= JSR PC,d)||CCC |000257|0000|Clear all Condition Codes |{C,N,V,Z}=0 ||CLC |000241|---0|Clear Carry |C=0 ||CLN |000250|0---|Clear Negative |N=0 ||CLRb d |B050DD|0100|Clear |d=0 ||CLV |000242|--0-|Clear Overflow |V=0 |

-

8/14/2019 lsi-11

3/5

|CLZ |000244|-0--|Clear Zero |Z=0 ||CMPb s,d |B2SSDD|****|Compare |s-d ||COMb d |B051DD|**01|Complement |d=~d ||DECb d |B053DD|***-|Decrement |d=d-1 ||DIV s,r |071RSS|****|Divide |r=r/s (EIS)||EMT t |1040TT|----|Emulator Trap |Vector at 30 ||FADD r |07500R|**00|Floating Add | (FIS)||FDIV r |07503R|**00|Floating Divide | (FIS)|

|FMUL r |07502R|**00|Floating Multiply | (FIS)||FSUB r |07501R|**00|Floating Subtract | (FIS)||HALT |000000|----|Halt | ||INCb d |B052DD|***-|Increment |d=d+1 ||IOT |000004|----|Input/Output Trap |Vector at 20 ||JMP d |0001DD|----|Jump |PC=d ||JSR r,d |004RDD|----|Jump to Subroutine |r=PC,PC=d ||MARK n |0064NN|----|Mark stack |RTS aid ||MFPS d |1067DD|**0-|Move From Processor Status|d=PS (byte)||MOVb s,d |B1SSDD|**0-|Move |d=s ||MTPS s |1064SS|****|Move To Processor Status |PS=s (byte)||MUL s,r |070RSS|**0*|Multiply |r=r*s (EIS)||NEGb d |B054DD|****|Negate |d=-d |

|NOP |000240|----|No Operation | ||RESET |000005|----|Reset external bus | ||RETURN |000207|----|Return from subroutine | (= RTS PC)||ROLb d |B061DD|****|Rotate Left |d={C,d}{C,d} ||RTI |000002|----|Return from Interrupt |{PC,PS}=(SP)+||RTS r |00020R|----|Return from Subroutine |PC=r,r=(SP)+ ||RTT |000006|----|Return from interrupt |Inhibit T-bit||SBCb d |B056DD|****|Subtract Carry |d=d-C ||SCC |000277|1111|Set all Condition Codes |{C,N,V,Z}=1 ||SEC |000261|---1|Set Carry |C=1 ||SEN |000270|1---|Set Negative |N=1 ||SEV |000262|--1-|Set Overflow |V=1 |

|SEZ |000264|-1--|Set Zero |Z=1 ||SOB r,a |077RNN|----|Subtract One and Branch |PC=PC-2*NN ||SUB s,d |16SSDD|****|Subtract |d=d-s ||SWAB d |0003DD|**00|Swap Bytes | ||SXT d |0067DD|-*0-|Sign Extend |d=0 or -1 ||TRAP t |1044TT|----|Trap |Vector at 34 ||TSTb d |B055DD|**00|Test |d ||WAIT |000001|----|Wait for interrupt | ||XOR r,d |074RDD|**0-|Exclusive OR |d=dxr |--------------------------------------------------------------------------------------------------------------------------------|Mnemonic |Opcode|NZVC|Description ||---------+------+----+----------------------------------------|

| | B| |0 for word, 1 for byte (1 bit) || | DD| |Destination field (6 bits) || | N| |Number (3 bits) || | NN| |Number (6 bits) || | R| |Register (3 bits, R0-5/SP/PC) || | SS| |Source field (6 bits) || | TT| |Number (8 bits) || | XX| |Offset (8 bits, -128 to +127) ||----------------+----+----------------------------------------|| PSW |-*01|Flag unaffected/affected/reset/set || | |Priority interrupt (Bit 7) |

-

8/14/2019 lsi-11

4/5

| T | |Trace trap (Bit 4) || N |N |Negative (Bit 3) || Z | Z |Zero (Bit 2) || V | V |Overflow (Bit 1) || C | C|Carry (Bit 0) ||---------------------+----------------------------------------|| r |Register (mode 0) || (r) |Register deferred (mode 1) |

| @r | ditto || (r)+ |Auto-increment (mode 2) || @(r)+ |Auto-increment deferred (mode 3) || -(r) |Auto-decrement (mode 4) || @-(r) |Auto-decrement deferred (mode 5) || nn(r) |Index (mode 6) || @nn(r) |Index deferred (mode 7) || #nn |Immediate (mode 2, r=PC) || @#nn |Absolute (mode 3, r=PC) || nn |Relative (mode 6, r=PC) || @nn |Relative deferred (mode 7, r=PC) ||---------------------+----------------------------------------|| Rn |General purpose Register (16-bit, n=0-5)|

| SP |Stack Pointer (16-bit, R6) || PC |Program Counter (16-bit, R7) || PS |Processor Status (16-bit) ||---------------------+----------------------------------------|| a |Relative address || b |Blank or B for word or byte operand(s) || d |Destination || n |Register Number (0 to 5) || nn |16-bit expression (0 to 65535) || r |Register (Rn,SP,PC) || s |Source || t |Trap number || + |Arithmetic addition |

| - |Arithmetic subtraction || * |Arithmetic multipication || / |Arithmetic division || ^ |Arithmetic exponent || & |Logical AND || ~ |Logical NOT || v |Logical inclusive OR || x |Logical exclusive OR || |Rotate right || { } |Combination of operands ||---------------------+----------------------------------------|| DEC |Digital Equipment Corporation |

| EIS |Extended fixed point Instruction Set || FIS |Floating point Instruction Set || LSI |Large Scale Integration || PSW |Processor Status Word ||---------------------+----------------------------------------|| 000 |Reserved vector || 004 |Time-out/system error vector || 010 |Illegal and reserved instruction vector || 014 |BPT instruction vector || 020 |IOT instruction vector || 024 |Power fail vector |

-

8/14/2019 lsi-11

5/5

| 030 |EMT instruction vector || 034 |TRAP instruction vector || 060 |Console input device vector || 064 |Console output device vector || 100 |External event line interrupt vector || 244 |FIS vector (optional) || 160000-177776 |Device addresses |----------------------------------------------------------------

![[Guide] & [Worklog] - Enigmabox virtuell · [Worklog] - [User Review] VPN Gateway Enigmabox - virtualisiert auf dem Prüfstand Einleitung: Hi ... 8 GB Speicher (flat) an LSI parallel](https://static.fdokument.com/doc/165x107/5f070fe57e708231d41b1cc5/guide-worklog-enigmabox-virtuell-worklog-user-review-vpn-gateway.jpg)