Prof. Dr. J. Reichardt haw hamburg Prof. Dr. B. Schwarz...

Transcript of Prof. Dr. J. Reichardt haw hamburg Prof. Dr. B. Schwarz...

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-1

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3 U bersicht zum üC 8052 ..................................... 3-23.1 Hardware-Architektur.......................................... 3-3

3.2 Speicherorganisation............................................ 3-7

3.2.1 Universalregister ............................................... 3-8

3.2.2 Special Function Register ................................. 3-9

3.3 Externer Speicher............................................... 3-10

3.4 Zeitgeber 2 Betriebsarten................................... 3-13

3.5 Integrierte serielle Schnittstelle ......................... 3-16

3.5.1 Register der seriellen Schnittstelle ................. 3-17

3.5.2 Abla ufe im Sendebetrieb des Modus 1 .......... 3-19

3.5.3 Abla ufe im Empfangsbetrieb des Modus 1.... 3-22

3.6 Aufbau des Assembler-Codes........................... 3-26

3.7 Befehlsubersicht des –C 8051 Assemblers........ 3-32

3.8 8052 Interrupt Organisation............................... 3-33

3.8.1 Interrupt Freigabe und Priorita t....................... 3-33

3.8.2 Interrupt Flaggen und Ausfuhrung.................. 3-35

3.8.3 Interrupt Vektoren........................................... 3-37

3.8.4 Programmbeispiel ........................................... 3-38

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-2

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3 U bersicht zum üC 8052• Der erste MCS-51 mit 60000 Transistoren wurde von Intel 1980 angekundigt. Eine Vielzahl von neuen Mitglie-

dern wurden der MCS-51 Familie zugefugt, die insbesondere als embedded controllers fur closed-loop Anwen-dungen in geregelten Prozessen mit A/D-Umsetzerschnittstellen entwickelt wurden. Die Verfugbarkeit der 8051-Varianten wird durch Zweithersteller (Siemens, Philips, SGS-Thompsen) unterstutzt.

• Von Siemens z. B. werden in der C500 Familie 20 Varianten mit der folgenden Kernarchitektur angeboten:

ð Versionen mit 12/24/40 MHz Taktfrequenz

ð Maximal 8 kB ROM Programmspeicher

ð 256 Byte RAM incl. Funktionsregister

ð Vier 8 Bit Ports

ð Drei 16 Bit Zeitgeber als up-counter

ð Eine universelle synchrone/asynchrone Receiver/Transmitter (USART) Schnittstelle

ð Sechs Interruptquellen ( 2 extern/4 intern) mit zwei Prioritatsebenen

• Der Weltmarkt der 8 Bit Mikrocontroller umfasste 1998 mit 14 Herstellern 5,036 Milliarden US Dollar. DieMarktanteile der 16 Bit üCs machten 1998 2,6 Milliarden US Dollar aus.

• Der auf dem XS95 Board verfugbare üC 8032 ist eine ROM lose Version des Zweitherstellers OKI. Als Pro-gramm- und Datenspeicher ist ein 32 kB SRAM angeschlossen. Das CPLD XC95108 ist in den Adressbus und dieSRAM-Ansteuerung eingebunden.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-3

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

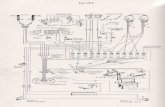

3.1 Hardware-Architektur

Bild 3-1: Blockdia-gramm des ü C8052 [9]

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-4

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

U bersicht zu den Portpins und Steuersignalen

• Port 0: Fur das System mit externem Programmspeicher wird Port 0 als gemultiplexter Daten- und

Adressbus verwendet (D0-D7 u. A0-A7).

• Port 1: Die 8 Portpins stehen als I/O Schnittstellen frei zur Verfugung. Es sind keine alternativen Pinfunktio-

nen zu beachten. Aufgrund der direkten Kopplung des Port 1 mit dem XC95108 CPLD und den her-ausgefuhrten Boardanschlussen sind die Signaltreiberrichtungen im VHDL-Code und Assembler-Code aufeinander abzustimmen.

• Port 2: Die oberen 8 Adressbits (A7-A14) werden uber Port 2 ausgegeben, sodass 32 kB adressierbar sind.

Alle Pins ko nnen vom CPLD gelesen werden.

• Port 3: Die Portpins sind mit den Funktionen der Hardwarearchitektur zweifach belegt. In der XS95 Board-

Anwendung sind folgende Funktionen relevant:

Bit/Pin-Nr. Name Bit Adresse Funktion

P3.1/13 TXD B1H Serielle Sendeleitung desUART

P3.6/18 ¬WR B6H Schreibfreigabe fur ext. Da-tenspeicher

P3.7/19 ¬RD B7H Lesefreigabe fur ext. Daten-speicher

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-5

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

• ¬PSEN: Mit dem Steuersignal Program Store Enable wird der externe Programmspeicher freigegeben.U berlicherweise wird der Pin ¬PSEN mit dem Output Enable (¬OE) Eingang eines EEPROMsverbunden, damit die Programmbytes gelesen werden ko nnen. Das Signal ¬PSEN wird vom üC wah-rend des Befehl-Holzyklus auf low getaktet.

• ALE: Der üC 8051 setzt das Signal Address Latch Enable zum Demultiplexen des Adress- und Datenbussesein. Wenn das Port P0 als Datenbus arbeitet, soll das Signal ALE die unteren 8 Adressbitswahrend der ersten Halfte eines Speicherzyklus in ein externes Latch ubernehmen. Danach ist dasPort P0 frei fur die Daten, die in der zweiten Zyklushalte zum Speicher ubertragen werden. Bei Zu-griffen auf den Programmspeicher nimmt das Latch die untere Halfte des 16 Bit breiten Programm-zahlers PCL auf. Im Fall von Datentransfers werden die A0-A7 Leitungen von der unteren Halfte desDatapointers DPTR belegt.

• ¬EA: Ist das Eingangssignal External Access Enable auf high gelegt, wird das Programm bis zu denAdressen 1000H bzw. 2000H aus dem internen ROM-Bereich ausgefuhrt. Bei der ROM-losen üC Va-riante 8032 des XS95 Boards ist ¬EA mit Masse verbunden, sodass bei der Befehlsabarbeitung auto-matisch die erforderlichen ¬PSEN und ALE Signalverlaufe erzeugt werden.

• ¬WR: Das Schreibsteuersignal latched die Datenbytes von Port 0 in den externen Datenspeicher.

• ¬RD: Das Lesesteuersignal gibt die Ausgange des externen Datenspeichers frei, sodass der Datenbus mit Speicherbytes belegt wird.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-6

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Ein-/Ausgabeleitungen Port 1

Bild 3-2: Quasi-bidirektionale Ein/Ausgabeleitung von Port P1 [11]

• Quasibidirektionale Datenubertragung ohne Tri-State Zustand. Ausgangs-High-Pegel werden durcheinen internen Pull-up Widerstand (40 kΩ) erzeugt.

• Bei Dateneingabe muss im Latch eine “1– stehen,damit mit ¬Q = 0 der Feldeffekt-Transistorhochohmig wird. Ein Systemreset setzt alle Portlat-ches, sodass die Anschlusse als Eingange wirken ko n-nen. Mit SETB P1.i lassen sich einzelne Eingangslei-tungen gezielt vorbereiten. Mit MOV P1,#0FFH wirddas Port 1 komplett zum Eingang. Datentransferbe-fehle (z. B. MOV C,P1) lesen den Pin. Read-modify-write Instruktionen lesen den Latchausgang.

• Aufgrund eines Ausgabebefehls CLR P1.3 ubernimmtdas Latch die “0–. Der Ausgang ¬Q = 1 schaltet denFET durch und der Pin wird uber 150 Ω mit Masseverbunden. Um Kurzschlusse zu vermeiden, darf diesnicht bei Portpins erfolgen, die als Eingange verwen-det werden.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-7

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.2 Speicherorganisation

Bild 3-3: Adressierbarer Speicher-bereich der ü C 805x Derivate[11].

• Die üC 805x haben separate Adressraume fur Programmcode (ROM) und Datenspeicher (RAM). Fur Pro-grammcode werden 64 kB unterstutzt, die untersten 4 kB bzw. 8 kB sind auf dem Chip, der Rest ist extern. Zusatzlichzum on-chip RAM werden 64 kB externer Datenspeicherbereich unterstutzt

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-8

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.2.1 Universalregister

• Der untere Block des internen RAMs ist in drei Bereiche gegliedert, die direkt oder indirekt adressierbar sind:

4 Registerbanke a 8 Register (R0 ” R7), einen auch bitweise adressierbaren Abschnitt mit 16 Byte und einen 80Byte tiefen RAM Bereich.

• Nach einem Reset sind die unteren 8 Register an den Adressen 00H-07H verfugbar. In 1-Byte MOV-Befehlenwerden die Register mit Ri angesprochen. Die Wahl der Registerbanke kann im Program Status Word (PSWim Special function Register) mit zwei Bits PSW.3 u. PSW.4 verandert werden. Alle 32 Register lassen sich auchdurch ihre Adresse ansprechen, wobei jedoch 2-Byte Befehle beno tigt werden.

• 128 bitadressierbare Speicherplatze liegen zwischen den Byteadressen 20H und 2FH. Diese Bits lassen sich mitBefehlen direkt manipulieren (SETB 2BH). Die oberen 80 Byte liegen zwischen 30H bis 7FH.

• Die 128 Byte der oberen Halfte des internen Datenspeicherbereiches ist nur indirekt adressierbar (80H ” FFH).Diese Einschrankung ist erforderlich, da unter den gleichen Adressen die nur direkt adressierbaren 128 Bytedes Special Function Registers angesprochen werden.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-9

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.2.2 Special Function Register

Bild 3-4: Interner RAM-Bereich des ü C 8051 [9]

Die 128 Byte Special Function Register enthaltenStatusregister und die Steuerregister fur die inte-grierten Peripheriefunktionen. Diese Register sindnur direkt bzw. auch bitadressierbar.

• ACC Accumulator

• PSW Program Statusword

• IP Interrupt Priority

• Pi Port Register

• IE Interrupt Enable

• DPTR Data Pointer

• SP Stack Pointer

Serial Interface:

• SBUF Serial Data Buffer

• SCON Serial Port Control

Timer 2:

• T2CON Control Register (Adresse C8HEX)

• RC2L Reload Register Low Byte (CA HEX)

• RC2H Reload Register High Byte (CB HEX)

• TL2 Timer 2 Value Reg. Low Byte (CD HEX)

• TH2 Timer 2 Value Reg. High Byte (CC HEX)

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-10

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.3 Externer Speicher

Bild 3-5: Anschluss des externen Programm und Datenspeichers [9]

¬WR ¬WE

¬RD

SRAM

• Das XS95-Board bietet einen 32 kBSRAM Speicher gemeinsamen fur denProgramm- und den Datenbereich.

• Das Signal ¬PSEN wird zum Lesenvon Befehlen und das Signal ¬RD zumLesen von Daten angesteuert. Damitbeide Zugriffe des Controllers alterna-tiv wirksam werden ko nnen, wird der¬OE Eingang des SRAMs uber einUND-Gatter mit den Steuersignalenverbunden (vgl. Bild 3-6).

• Das haufig angegebene Adress-Latch istdurch ein flankengesteuertes Register zu er-setzen, damit ein durchgangig synchronesSystem entsteht (vgl. Bild 3-6). Furdiese Koppelfunktionen ist im VHDL-Design eine separate Komponente vorzuse-hen, die ALE als Clock-Enable nutzt (vgl. Bild 3-7).

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-11

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Bild 3-6: Hardware-Interfacing zwischen den Komponenten des XS95-Boards. Ansteuerung des externen SRAMs.

üC 8052

SRAM

CPLD XC95108CLK

P9 P10 P21XTAL1

RESETP46 P45 P10

RSTP70

TXD P3.1P12

P13¬PSEN

P32

P32¬RD P3.7

P19

¬WR P3.6P18

¬WE

P24-31A8 -A15 P2.0 ” P2.7

A8 -A15

A0/D0 ” A7/D7 P0.0 ” P0.7

D0 ” D7

P20ALE

P33

8

CLK

RESET

8A0 ” A7

¬OEP62

¬CEP65

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-12

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Bild 3-7: Timing zu einem Befehlsabruf aus einem externen Programmspeicher [11].

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-13

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.4 Zeitgeber 2 Betriebsarten

• Der Zeitgeber 2 ist ein 16-Bit Zeitgeber/Zahler der als Zeitgeber oder Zahler arbeitet. Drei Betriebsmodi sindwahlbar:

‚ 16-Bit nachladbarer Frequenzteiler (inkrem. oder dekrem.) erzeugt periodische Interrupts (auto-reload)

‚ Auslesen des 16-Bit Zahlerstandes bei einem bestimmten Ereignis: Zeitintervallmessung (capture mode)

‚ Baudratengenerator fur die serielle Schnittstelle (UART)

• Die Betriebsmodi werden uber Bits des Special Function Register angewahlt SFR T2CON (C8HEX ):

• RCLK (Receive Clock Enable) = 1: Die serielle Schnittstelle nutzt die U berlaufpulse des Zeitgebers 2 als Empfan-gertaktsignal (UART Betriebsmodi 1 und 3).

• TCLK (Transmit Clock Enable) = 1: Die serielle Schnittstelle nutzt die U berlaufpulse des Zeitgebers 2 als Sender-taktsignal (UART Betriebsmodi 1 und 3).

• TR2 (Start/Stop Control) = 1: Der Zeitgeber 2 wird gestartet.

• C/¬T2 (Zeitgeber or Counter select): C/¬T2 = 0 Freigabe der Zeitgeberfunktion (interner Takt = Quarz/12).C/¬T2 =1 Freigabe der Ereigniszahlerfunktion (nega. Flanke)

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-14

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Timer overflow

Bild 3-8: Zeitgeber 2 als Baudraten-Generator fu r den Receiver RX und den Transmitter TX des UART [11] .

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-15

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

• Der Zeitgeber 2 wird durch Setzen der Bits TCLK und/oder RCLK im SFR Register T2CON als Baudratenge-nerator angewahlt (MOV T2CON,#10H;). In diesem Betriebsmodus des Zeitgebers 2 verursacht ein U berlaufdes Zahlerregisters TH2 ein Nachladen der Zahlerregister TH2 und TL2 mit den Inhalten der VorladeregisterRC2H und RC2L, die vom Anwender beschrieben werden (MOV RC2H,#0FEH; MOV RC2L,#0C8H;).

• Die Baudrate der seriellen Schnittstelle (Betriebsmodi 1 und 3) wird durch die U berlaufrate des Zeitgebers 2nach folgendem Zusammenhang bestimmt:

Modi 1, 3 Baudrate = (Zeitgeber 2 U berlaufrate)/16

• Die Zahlerregister (T2H,T2L) des Zeitgebers 2 werden im Betrieb als Baudratengenerator mit jedem Zu-standswechsel Si → Si+1 inkrementiert (fOSC /2). Die Zeitgeber 2 U berlaufrate bestimmt sich deshalb zu:

Zeitgeber 2 U berlaufrate = (fOSC /2)/(216 -(RC2H, RC2L)

Darin ist (RC2H, RC2L) der Inhalt der Nachladeregister RC2H and RC2L als 16-Bit Integerwert.

• In diesem Betriebsmodus wird das Zeitgeberuberlaufflag TF2 bei einem U berlauf des TH2 Registers nicht ge-setzt uns es wird kein Interrupt erzeugt. Deshalb muss der Interrupt des Zeitgebers 2 auch nicht disabled wer-den (Bit mit Index 5 im SFR Register IE: ET2).

• Es ist zu beachten, dass die Zahlerregister TH2 und TL2 nicht gelesen oder beschrieben werden sollen, wennder Zeitgeber eingeschaltet ist (TR2 =1). Die Nachladeregister RC2x durfen im laufenden Betrieb gelesen wer-den, sollten aber nicht beschrieben werden, da der Zugriff zeitgleich mit einem U berlauf-Nachladevorgang er-folgen ko nnte. Turn Zeitgeber 2 off ( CLR TR2;) before accessing the Zeitgeber 2 or RC2x registers.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-16

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.5 Integrierte serielle Schnittstelle

Bild 3-9: Blockdiagramm des ü C-UART [9]

internal üC 8 bit bus

• Vollduplex-Modus: Senden und Empfangenist gleichzeitig mo glich.

• Die Empfangerhardware ist doppelt gepuffert(double buffered): Der empfangene Datenrah-men wird zum Lesen gespeichert, wahrend einneuer Datenrahmen empfangen wird. Der ge-speicherte Datenrahmen muss gelesen wordensein, bevor der zweite Rahmen komplett ist.

• Der Zugriff auf das Sende- und das Empfangs-register erfolgt uber das gleiche SFR Register:SBUF Register (Adresse 99HEX).

• Ein Schreibvorgang auf das SBUF Registerladt den Sendespeicher und startet automatischden Sendevorgang.

• Ein eintreffendes Startbit lo st mit dem High-Low-U bergang am RXD-Pin (P3.0) den Emp-fangsvorgang aus.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-17

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Bild 3-10: Serielles Datenprotokoll und Transmit-Interruptbit [9].

3.5.1 Register der seriellen Schnittstelle

• Das Steuer- und Statusregister der seriellen Schnittstelle ist das Special Function Register SCON. Dieses Regi-ster enthalt ausser den Modusbits auch die Interruptbits TI and RI.

TI(SCON.1)

• Im Betriebsmodus 1 sendet derUART einen Datenrahmen mit 10Bits: Startbit, 8 Datenbits mit demLSB zuerst und ein Stopbit.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-18

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

• SM0,SM1 (Serial port operating mode selection bits): 0 1 Modus 1 - 8-Bit UART mit variabler Baudrate.

• REN (Enable receiver of serial port): Freigabe des seriellen Empfangs. Muss mit Software gesetzt und ruckge-setzt werden.

• TI (Serial port transmitter interrupt flag): TI wird von der Hardware im Modus 0 am Ende des 8ten Datenbitsgesetzt. In den anderen Modi wird TI zu Beginn des Stopbits automatisch gesetzt. TI muss von der Softwaregelo scht werden. Durch U berwachung von TI ko nnen zyklische Sendevorgange gesteuert werden.

• RI (Serial port receiver interrupt flag): RI wird von der Hardware im Modus 0 am Ende des 8ten Datenbits ge-setzt. In den anderen Modi wird RI in der Mitte des Stopbits automatisch gesetzt. RI muss von der Softwaregelo scht werden.

• RB8 (Serial port receiver bit 9): Im Modus 1 ist RB8 das empfangene Stopbit. In den Modi 2 und 3 ist RB8 das9te Datenbit, das empfangen wurde.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-19

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK3.5.2 Ablaufe im Sendebetrieb des Modus 1

• 10 Bits werden uber TXD gesendet oder uber RXD empfangen: Ein Startbit (Low), 8 Datenbits (LSB zuerst)und ein Stopbit (High). Beim Empfang geht das Stopbit ins RB8 Bit des SCON Registers. Die Baudrate wirdvon der U berlaufrate des Zeitgebers 1 (Empfang) oder von der des Zeitgebers 2 (Senden) bestimmt, oder vonbeiden, falls im Vollduplexbetrieb gearbeitet wird. Das Timing des Sendebetriebs ist in Bild 3-11 dargestellt.Ein vereinfachtes Blockdiagramm des UART-Senders zeigt Bild 3-12.

• Der Sendevorgang wird von einem Assembler-Befehl gestartet, der das SBUF (send buffer) Register als Ziel be-nutzt. Das –Write to SBUF’ Signal ladt ein Stopbit (‘1‘) in die 9te Sende-Schieberegisterposition und signali-siert der Sendesteuerung TX am Start-Eingang, dass eine U bertragung angefordert wird.

• Der Sendevorgang beginnt mit dem nachsten U berlauf des Modulo 16 Zahlers (divide-by-16 counter), der mitder Zeitgeber 2 U berlaufrate getaktet wird. Das U berlaufsignal TX Clock erzeugt den Pegelwechsel von¬SEND. Die Pulse der Datenbits sind also auf den Modulo 16 Zahlerausgang und nicht auf das –Write toSBUF’ Signal synchronisiert.

• Die U bertragung startet mit der Aktivierung des Signals ¬SEND, das das Startbit (Low) an den TXD-Ausgangbringt. Eine Pulsbreite spater wird das Steuersignal DATA aktiv, sodass das Ausgangsbit D0 des Sendeschiebe-registers an den Sendeausgang TXD gelangt. Mit dem nachsten TX Clock U berlaufsignal erscheint der ersteSchiebeimpuls Shift und das nachste Bit D1 wird ubertragen.

• Wahrend die Datenbits Di aus dem Senderegister SBUF rechts herausgeschoben werden, nimmt das SBUF Re-gister von links Nullen (D = —0—) auf. Wenn das MSB (D7) des Datenbytes am Ausgang des SchieberegistersSBUF erscheint, steht die zu Beginn in die 9te Position geladene —1— links vom MSB eine Position vor dem Aus-gang. Alle 6 SBUF-Bits links davon sind mit —0— besetzt.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-20

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

• Aufgrund dieser Bedingung signalisiert der Zero Detector an die Sendesteuerung TX, dass nur noch ein letzterSchiebevorgang (8ter) zu erfolgen hat. Dieser tritt auf mit dem 10ten U berlauf (TX Clock) des Modulo 16 Zah-lers nach Aktivierung des –Write to SBUF– Pulses. Damit wird dann das Stopbit —1—zum Ausgang TXD gescho-ben, was vom TI Signal angezeigt wird. Der nachste (11te) Schiebeimpuls Shift deaktiviert ¬SEND und DATA,sodass eine —1— am TXD Ausgang erhalten bleibt.

Bild 3-11: Timing des Sendevorgangs der seriellen Schnittstelle im Betriebsmodus 1 [11]

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-21

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Bild 3-12: Blockdiagramm der Senderkomponente des UART im Betriebsmodus 1 [11]

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-22

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.5.3 Ablaufe im Empfangsbetrieb des Modus 1

• Die Empfangskomponente erhalt im Betriebsmodus 1 die U berlaufrate des Zeitgebers 2 als Taktsignal, das ei-nen Modulo 16 Zahler taktet, der mit seinem U berlauf entsprechend der Senderbaudrate die RX Clock Pulseliefert (vgl. Bild 3-13; Bild 3-14).

• Ein 1 ” 0 ” U bergang am Dateneingang RXD startet den Empfangsvorgang. Zu diesem Zweck wird der Eingangmit einer Frequenz abgetastet, die dem 16fachen der Sender-Baudrate entspricht. Nachdem dem Start Eingangder Empfangssteuerung ein Signalubergang (Startbit) signalisiert wurde, erfolgt unmittelbar ein Reset des Mo-dulo 16 Zahlers und der Wert 1FFHex wird ins 9 Bit breite Empfangsschieberegister geladen. Mit dem erkann-ten Beginn des Startbits ist der Empfanger auf den Senderbitstrom synchronisiert worden.

• Die 16 Zahlzustande des Modulo 16 Zahlers teilen die Pulsbreite der empfangenen Datenbits in 16tel. In denZahlzustanden 7, 8 und 9 tastet der Bit Detector die Pegel am RXD Eingang ab. Derjenige Pegel wird danachals Datenbit akzeptiert und von rechts nach links ins Schieberegister aufgenommen, der mindestens zweimalerkannt wurde. Diese Majoritatsauswahl dient der Rauschunterdruckung.

• Wenn zu Beginn nach dem 1 ” 0 U bergang vom Bit Detector kein Low-Pegel festgestellt wird, dann geht dieEmpfangsschaltung zuruck in den Anfangszustand, in dem das Polling des 1 ” 0 U berganges erfolgt. Mit die-sem Schritt werden falsche Startbits eliminiert. Liegt ein korrektes Startbit vor, dann wird dieses von rechts insSchieberegister getaktet und der Empfang des restlichen Rahmens schreitet fort.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-23

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

• Wahrend die Datenbits von rechts geladen werden, erscheinen —1—sen am linken Schieberegisterausgang. Sobalddas Startbit (—0—) dort erscheint, wird der Empfangssteuerung (RX Control) signalisiert, nur noch einen weite-ren Schiebevorgang (10tes Shift)) durchzufuhren, das Empfangspufferregister SBUF sowie RB8 im SCON mit—1—zu laden und das Empfangsinterruptbit RI zusetzen.

• Das Signal zum Laden des SBUF Registers und des RB8 Bits im sowie zum Setzen des RI Bits wird nur danngeneriert, wenn zum Zeitpunkt des letzten Shift Pulses die beiden folgenden Bedingungen erfullt sind:

1) RI = 0 ; RI muss nach dem letzten empfangenen Byte durch die Software gelo scht worden sein.

2) Das empfangene Stopbit ist ‘1‘ .

• Wenn eine der Bedingungen nicht erfullt ist, geht der empfangene Rahmen unwiederbringbar. Sofern beideBedingungen erfullt sind, ubernimmt RB8 das Stopbit, das Datenbyte geht uber in SBUF und RI wird aktiviert.Unabhangig davon, ob die Bedingungen erfullt sind, wechselt die Empfangsschaltung in den Anfangszustand, indem das Polling des 1 ” 0 U berganges am RXD Eingang erfolgt.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-24

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Bild 3-13: Timing des Empfangsvorgangs der seriellen Schnittstelle im Betriebsmodus 1 [11]

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-25

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Bild 3-14: Blockdiagramm der Empfangerkomponente des UART im Betriebsmodus 1 [11]

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-26

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.6 Aufbau des Assembler-Codes

• Es wird empfohlen, den Assembler-Code mit einem konsistenten Aufbau zu entwerfen, gerade auch dann wennder Code schrittweise entwickelt wird. Generell sollten die Abschnitte des Codes in folgender Reihenfolge ange-ordnet sein:

ð Code-Segment- und Daten-Segment-Deklarationen fur die verschiedenen Speicherbereiche:

DATA interner Speicher adressierbar mit direkter Adressierung (00Hex ” 7F Hex)

IDATA interner Speicher adressierbar mit indirekter Adressierung (00Hex ” 7F Hex),

(00Hex ” FFHex) im üC 8052

XDATA externer Datenbereich

ð Equate Direktiven fur Symbole und Konstanten

ð Code Segment mit:

v Initialisierung der Peripheriekomponenten (z. B. T2CON, SCON)

v Hauptprogramm

v Subroutinen

v Daten-Konstantendefinitionen (DB Define Byte und DW Define Word)

ð Code-Abschnitt mit Interrupt-Serviceroutinen

ð END Direktive

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-27

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

• Code- und Datensegmente sind separiert, da der Code in vielen Fallen mit ROMs oder EEPROMs gespeichertwird und Daten in RAM-Speichern immer gelesen und geschrieben werden. Hinzu kommt, dass der Mikrocon-troller verschiedene RAM-Bereiche fur Daten zur Verfugung stellt, die bei der Adressierung unterschiedenwerden mussen.

• Datenkonstanten und Strings, die durch DB und DW Direktiven definiert sind geho ren zum Codesegment, dadiese als nicht veranderbare Daten zum Assembler-Instruktionen eines Programms geho ren.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-28

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Simple Source Code Template for A51 Assembler$NOMOD51 ; disable predefined 8051 registers

$INCLUDE (REG52.INC) ; include CPU definition file (for example, 8052)

;------------------------------------------------------------------------------------------------------

;Segment and variable declarations

;DATA SEGMENT--Reserves space in DATA RAM

;The internal data space accessible by direct addressing : 00 HEX ” 7F HEX

;------------------------------------------------------------------------------

data_seg_name SEGMENT DATA ; relocatable segment for DATA RAM.

RSEG data_seg_name ; switch to this data segment

data_variable: DS 1 ; reserve 1 Bytes for data_variable

data_variable1: DS 2 ; reserve 2 Bytes for data_variable1

;------------------------------------------------------------------------------------------------------

;IDATA SEGMENT--Reserves space in IDATA RAM

;The entire internal data space accessible by indirect addressing: 00 HEX ” 7F HEX,

; 00 HEX ” FF HEX on the 8052

;------------------------------------------------------------------------------

idata_seg_name SEGMENT IDATA ; relocatable segment for DATA RAM.

RSEG idata_seg_name ; switch to this data segment

idata_variable: DS 1 ; reserve 1 Bytes for idata_variable

idata_variable1: DS 2 ; reserve 2 Bytes for idata_variable1

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-29

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK;------------------------------------------------------------------------------

; XDATA SEGMENT--Reserves space in XDATA RAM The external data space

;------------------------------------------------------------------------------

xdata_seg_name SEGMENT XDATA ; relocatable segment for XDATA RAM

RSEG xdata_seg_name ; switch to this xdata segment

xdata_variable: DS 1 ; reserve 1 Bytes for xdata_variable

xdata_array: DS 500 ; reserve 500 Bytes for xdata_array

;-------------------------------------------------------------------------------

; ABSOLUTE XDATA SEGMENT--Reserves space in XDATA RAM at absolute addresses.

; ABSOLUTE segments are useful for memory mapped I/O ( address bus is connected to other devices)

;------------------------------------------------------------------------------

XSEG AT 8000H ; switch absolute XDATA segment @ 8000H

XIO: DS 1 ; reserve 1 Bytes for XIO port

XCONFIG: DS 1 ; reserve 1 Bytes for XCONFIG port

;------------------------------------------------------------------------------

; BIT SEGMENT--Reserves space in BIT RAM

;The bit space; overlapping byte locations 20 HEX ” 2F HEX of the internal data space

;------------------------------------------------------------------------------

bit_seg_name SEGMENT BIT ; segment for BIT RAM.

RSEG bit_seg_name ; switch to this bit segment

bit_variable: DBIT1 ; reserve 1 Bit for bit_variable

bit_variable1: DBIT4 ; reserve 4 Bits for bit_variable

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-30

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK;------------------------------------------------------------------------------

; Add constant (typeless) numbers here.

;------------------------------------------------------------------------------

typeless_number EQU 0EDH ; assign 0ED HEX

typeless_num1 EQU typeless_number - 8 ; evaluate typeless_num1

;------------------------------------------------------------------------------

; Provide an LJMP to start at the reset address (address 0) in the main module.

; After a reset the program counter PC is loaded with 0000HEX .

;------------------------------------------------------------------------------

CSEG AT 0 ; absolute Segment at Address 0

LJMP start ; reset location (jump to start)

;------------------------------------------------------------------------------

; CODE SEGMENT--Reserves space in CODE ROM for assembler instructions.

;------------------------------------------------------------------------------

code_seg_name SEGMENT CODE

RSEG code_seg_name ; switch to this code segment

;------------------------------------------------------------------------------

; Insert your assembly program here. Note, the code below is non-functional.

;------------------------------------------------------------------------------

start: ORL IE,#82H ; enable interrupt system (Zeitgeber 0)

SETB TR0 ; enable Zeitgeber 0

repeat_label: MOV A,data_symbol;

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-31

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIKADD A,code_table; direct addressing

CALL code_symbol

MOV DPTR,#xdata_symbol

MOVX A,@DPTR

MOV R1,A

PUSH AR1

CALL sub_routine1

POP AR1

ADD A,R1

JMP repeat_label; end of main program body

;

code_entry: CALL code_symbol

RET

sub_routine1: NOP

RET

; Data constants in program storage space

code_table: DB typeless_number

DB —string‘ ,‘c‘ ,‘h‘ ,00H

;------------------------------------------------------------------------------

; The END directive is ALWAYS required.

;------------------------------------------------------------------------------

END ; End Of File

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-32

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.7 Befehlsubersicht des üC 8051 AssemblersMnemonic Description Mnemonic Description Mnemonic Description

JB bit,relJNB bit,relJBC bit,rel

jump if bit setif bit not setjump if bit set then clear

Arithmetic OperationsADD A,sourceADD A,#dataADDC A,#sourceADDC A,#dataSUBB A,sourceSUBB A,#dataINC AINC sourceDEC ADEC sourceINC DPTRMUL ABDIV ABDA A

add source to A

add with carry

subtract from Awith borrowincrement

decrement

increment DPTRmultiply A & Bdivide A by Bdecimal adjust A

Data TransferOperationsMOV A,sourceMOV A,#dataMOV dest,AMOV dest,sourceMOV dest,#dataMOV DPTR,#datal6MOVC A,@A+DPTRMOVC A,@A+PCMCVX A,@RiMOVX A,@DPTRMOVX @Ri,AMOVX @DPTR,APUSH directPOP directXCH A,sourceXCHD A,@Ri

move sourceto destination

move from code memory

move from data memory

push onto stackpop from stackexchange bytesexchange low order digits

Program BranchingACALL addr11LCALL addr16RETRETIAJMP addr11LJMP addr16SJMP relJMP @A+DPTRJZ relJNZ relCJNE A,direct,relCJNE A,#data,relCJNE Rn,#data,relCJNE @Rn,#data,relDJNZ Rn, relDJNZ direct,relNOP

call subroutine

return from subroutinereturn from interruptjump

jump if A = 0jump if A not = 0compare and jump if notequal

decrement and jump if notzerono operation

Logical OperationsANL A,sourceANL A,#dataANL direct,AANL direct,#dataORL A,sourceQRL A,#dataOAL direct,AORL direct,#dataXRL A,sourceXRL A,#dataXRL direct,AXRL direct,#dataCLR ACPL ARL ARLC ARR ARRC ASWAP A

logical AND

logical OR

logical XOR

clear Acomplement rotate A Ieftthrough Crotate A rightthrough Cswap nibbles

Boolean VariableManipulationCLR CCLR bitSETB CSETB bitCPL CCPL bitANL C,bitANL C,/bitORL C,bitORL C,/bitMOV C,bitMOV bit,CJC relJNC rel

clear bit

set bit

complement bit

AND bit with CAND NOT bit with COR bit with COR NOT bit with Cmove bit

jump if C setjump if C not set

LEGENDRn register addressing using RO R7direct 8-bit internal address (OOH-FFH)@Ri indirect addressing using RO or R1source any of [Rn,direct,@Rn]dest any of [Rn,direct,@Rn]#data 8-bit constant included in instr.#data 16 16-bit constantbit 8-bit direct address of bitRel signed 8-bit offsetaddr11 11-bit address in current 2k pageaddrl6 16-bit address

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-33

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.8 8052 Interrupt Organisation

ð Sechs Interruptquellen stehen zur Verfugung: zwei externe Interrupts, drei Timer-Interrupts und der Interruptder seriellen Schnittstelle.

ð Alle Interrupts sind nach dem Systemreset inaktiv und mussen einzeln freigegeben werden (Register IE 0A8Hex)

3.8.1 Interrupt Freigabe und Prioritat

ð Jede Interruptquelle muss jeweils separat mit einem speziellen Freigabebit des Interrupt Enable (IE) Registers imSFR aktiviert werden. Zusatzlich ist ein globales Freigabebit EA (IE.7) zu beachten, mit dem alle Interrupts freige-schaltet werden.

Bit Symbol Bitadresse Beschreibung: 1 gesetzt = Interrupt aktiv

IE.0 EX0 A8H Externer 0 Interrupt, P3.2 low aktiv (B2H)

IE.1 ET0 A9H Timer 0 Interrupt

IE.2 EX1 AAH Externer 1 Interrupt, P3.3 low aktiv (B3H)

IE.3 ET1 ABH Timer 1 Interrupt

IE.4 ES ACH Interruptquellen des DUART (TI und RI)

IE.5 ET2 ADH Timer 2 Interupt

IE.6 - AEH Nicht definiert

IE.7 EA AFH Globale Freigabe fur alle Interrupts

Zwei Bits mussen fur jeden Inter-rupt gesetzt werden:

;Im jeweiligen Programmabschnitt

SETB ES ; Freigabe des DUART

SETB EA ; Allgemeine Freigabe

; oder

MOV IE,#10010000; Initialisierung

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-34

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

ð Jedem Interrupt kann individuell eine von zwei Anforderungsprioritaten zugeordnet werden. Diese Rangfolgeerlaubt es einem Interrupt der Prioritat 1 eine laufende Interrupt Service Routine (ISR) der Prioritat 0 zu unter-brechen. Die Bearbeitung der unterbrochenen ISR wird erst fortgesetzt, wenn die Behandlung des Interrupts mitder Priortat 1 abgeschlossen ist. Die Bearbeitung des Hauprogramms wird erst nach Abschluss beider ISRs wiederaufgenommen.

ð Die Interrupt Prioritaten werden uber das bitadressierbare Register IP an der Adresse 0B8Hex des Special Func-tion Registers (SFR) gesteuert:

ð Wenn zwei Interrupts der glei-chen Prioritatsebene gleichzeitigauftreten, dann wird uber einefestgelegte sogenannte PollingSequenz entschieden welcher In-terrupt als erster bedient wird:

Extern 0, Timer 0, Extern 1,

Timer 1, DUART, Timer 2

Bit Symbol Bitadresse Beschreibung: 1 gesetzt = ho here Prioritat

IP.0 PX0 B8H Externer 0 Interrupt, P3.2 low aktiv (B2H)

IP.1 PT0 B9H Timer 0 Interrupt

IP.2 PX1 BAH Externer 1 Interrupt, P3.3 low aktiv (B3H)

IP.3 PT1 BBH Timer 1 Interrupt

IP.4 PS BCH Interruptquellen des DUART (TI und RI)

IP.5 PT2 BDH Timer 2 Interupt

IP.6 - - Nicht definiert

IP.7 - - Nicht definiert

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-35

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.8.2 Interrupt Flaggen und Ausfuhrung

ð Zu jedem Interrupt geho rt eine Flagge, die gesetzt wird, wenn das zugeho rige Ereignis in der Peripheriekompo-nente oder an dem extenen Anschluss aufgetreten ist. Unabhangig von der jeweiligen Interruptfreigabe (IE Pro-grammierung) sind die Flaggen durch die Software lesbar (z.B. JB TI, Label).

ð Ein Interrupt des DUART resultiert aus der ODER-Verknupfung des Empfangs- (Receive RI) mit dem Sendein-terrupt (Transmit TI). Interrrupts des Timer 2 werden durch einen Timer-U berlauf mit TF2 oder ein externesEingangsbit EXF2 erzeugt.

Interrupt Flagge SFR Register und Bitposition

Extern 0 IE0 TCON.1 (timer control reg. 88Hex)

Extern 1 IE1 TCON.3

Timer 1 TF1 TCON.7

Timer 0 TF0 TCON.5

DUART TI SCON.1

DUART RI SCON.0

Timer 2 TF2 T2CON.7 (8052)

Timer 2 EXF2 TECON.6

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-36

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

Wenn ein Interrupt auftritt, den die CPU akzeptiert, wird die Bearbeitung des Hauptprogrammes unterbrochenund folgende Schritte werden vom üC automatisch durchgefuhrt:

ð Die momentane Befehlsbearbeitung wird zu Ende gefuhrt.

ð Der Programmzahlerstand (Progam Counter PC) wird auf den Stack (interner RAM-Bereich) gespeichert.

ð Der aktuelle Interruptstatus wird intern gespeichert.

ð Alle Interrupts mit gleicher Prioritat werden blockiert.

ð Der Programmzahler PC wird mit der speziellen Vektoradresse des jeweiligen Interrupts geladen.

ð Die Interrupt Service Routine ISR wird ausgefuhrt. Die Interrupt Flaggen des Timer 2 und des DUART mussenvon der Anwendersoftware zuruckgesetzt werden.

ð Die ISR wird mit einem RETI Befehl abgeschlossen.

ð Der alte PC Stand wird aus dem Stack gelesen und der vorherige Interruptstatus wird restauriert.

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-37

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.8.3 Interrupt Vektoren

ð Wenn ein Interrupt akzeptiert ist (Prioritat ho her als ein ggf. aktiver Interrupt), wird ein sogenannter InterruptVektor in den PC geladen.

ð Dieser Vektor ist die festgelegte Anfangsadresse einer ISR, die der jeweiligen Interruptquelle zugeordnet ist.

ð Fur die einzelnen Interrrupts stehen also im unterenProgrammspeicherbereich 8 Byte pro Quelle fur jedeISR zur Verfugung.

ð Aufgrund dieses geringen Speicherberumfanges, en-pfiehlt es sich, an der jeweiligen Stelle nur einenSprungbefehl zu platzieren, der mit seinem Label aufden tatsachlichen ersten Befehl einer ISR zeigt.

ð Um diesen unteren Programmspeicherbereich nicht mit dem Hauptprogramm zu belegen, sollte nach einem Reset,der den PC auf die Adresse 0000H setzt, nur ein Sprungbefehl z.B. LJUMP 0030H ausgefuhrt werden.

Interrupt Flagge Vektor Adresse

System Reset RST 0000H

Extern 0 IE0 0003H

Timer 0 TF0 000BH

Extern 1 IE1 0013H

Timer 1 TF1 001BH

DUART TI oder RI 0023H

Timer 2 TF2 oder EXF2 002BH

Prof. Dr. J. ReichardtProf. Dr. B. Schwarz UART - CPLD 95108 - C 8052

B. Schwarz 3-38

haw hamburgFACHBEREICH ELEKTROTECHNIK

UND INFORMATIK

3.8.4 Programmbeispiel

CSEG at 0; Code segment

ORG 0000H

LJMP MAIN ;Reset entry point

ORG 000BH

LJMP TI0ISR

ORG 0023H

LJMP DUATISR

ORG 002BH

LJMP TI2ISR

ORG 0030H ; Above interrupt vectors

MAIN: MOV T2CON,#010H; Ti. 2 mode 1 , TR2 = 0

...

TI0ISR: CPL P1.0

RETI

DUATISR: CLR TI

RETI

TI2ISR: CLR TF2

RETI

END