Schreib-Lese-Speicher (RAM) 1antriebstechnik.fh-stralsund.de/1024x768/Dokumen...Koppelelemente...

Transcript of Schreib-Lese-Speicher (RAM) 1antriebstechnik.fh-stralsund.de/1024x768/Dokumen...Koppelelemente...

Schreib-Lese-Speicher (RAM) 1

8. Halbleiterspeicher

Speicher sind spezielle sequentielle Schaltungen. Sie dienen dazu,große Mengen von Informationen (Daten, Programme) zu speichern.Speicher sind adressierbar.

Halbleiterspeicher werden vorwiegend bei Rechnern eingesetzt.

Um möglichst viele Informationen auf einem Chip speichern zu können,müssen

• Bauelemente geringste Abemessungen haben,

• die Anzahl der Bauelemente pro Speicherzelle gering sein und

• der Verdrahtungsaufwand klein sein.

Man unterscheidet

RAM: random access memorySchreib-Lese-Speicher

ROM: Read only memoryNur-Lese-Speicher

(PLD: Programmable logic devicesProgrammierbare Logikanordnungen)

RAM unterteilen sich in

SRAM: Static RAM (getaktete Flip Flop)

DRAM: dynamic RAM (Speicherung von Ladung in Kapazitäten)

2 Halbleiterspeicher

Bei RAM geht die Information bei Abschalten der Betriebsspannungenverloren: Sie sind flüchtige Speicher.

ROM unterscheidet man nach den Programmiermöglichkeiten:

PROM programmable ROM (einmalige Programmierung) ( and OPT [one time programmable] )

EPROM erasable PROM (mehrmalige Programmierung beim Kunden,UV löschbar, elektr. progr.)

EEPROM electrically erasable PROM (mehrmals beim Kundenprogrammierbar, elektrisch lösch- und programmierbar)

ROM sind nicht flüchtige Speicher

(PLD beinhalten zwei matrixartige Strukturen. Je nachdem, welcheMatrix programmierbar ist, unterscheidet man zwischen

FPLA: fieldprogrammable logic array (beide Matrizen können vomKunden programmiert werden)

PAL: programmable logic array (nur die erste Matrix kann vomKunden programmiert werden))

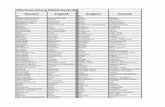

Mikroelektronische Speicher

RAM PLDROM

SRAM DRAM PROM EPROM EEPROM PAL FPLA

(8.1)

(8.1.1) (8.1.2)

(8.2)

(8.2.1) (8.2.2) (8.1.3)

Schreib-Lese-Speicher (RAM) 3

8.1. Schreib-Lese-Speicher (RAM)

8.1.1. Statische Schreib-Lese-Speicher (SRAM)

Struktur eines statischen RAM

CE

WE

OE

Tak

tste

ueru

ngA

dres

sene

inga

ng

Zei

lend

ecod

er

und

-tre

iber

Spa

lten-

dec.

Matrix

Spaltendecoder und -auswahl

LSV LSV LSV

...WL

A0

A1

An-1

... BL, BL

Daten-Ein-Ausgabe-Puffer

DQ0 DQ1 DQ7

UDD (5 V)

USS (Masse)

Ao - AN-1 : Adressensignale für 2N adressierbare Speicherwörter

DQj : Bidirektionale Dateneingänge (D) und Datenausgänge (Q)

UDD : Versorgungsspannung (5 V)

USS : Versorgungsspannung (Masse)

4 Halbleiterspeicher

CE : Chip Enable, Steuersignal für die Chipauswahl im Speichersystem(Low = aktiv) CE: HIGH: Signaleingänge unterbrochen, Datenaus-gänge hochohmig

WE : Write-Enable (Low aktiv)Steuersignal für Lese- oder Schreibvorgang

OE : Output-Enable (Low aktiv) Aktivierung der Datenausgänge

WL : Wortleitungen

BL : Bitleitungen

LSV : Lese-Schreib-Verstärker

< Aufbau Matrix

Speicherzelle

6-Transistor CMOS-Speicherzelle

TA TA

12

WL(VDD+US)

BL BL

VDD

Schreib-Lese-Speicher (RAM) 5

Speichern

WL: LOW Flip Flop abgeschaltet, der einmal eingestellteSpeicherzustand bleibt erhalten (z.B. Knoten 1 HIGH,Knoten 2 LOW) ⇒ Speicherzustand

Lesen

WL: HIGH Auswahltransistoren TA werden leitend. Knoten 1 wird mitBL und

(VDD +US) Knoten 2 mit BL verbunden. (Beispiel: BL wird aufgeladenBL wird entladen)

Damit wird die Information auf die Bitleitungen übertragen.Über die Spaltenadresse wird ein Bitleitungspaar mit demLeseverstärker verbunden und dem Datenausgangstreiberzugeführt.

⇒ Lesen

Anschließend WL : LOW

Schreiben

Bitleitungen werden mit dem Schreibverstärker verbunden. DieInformation wird auf das Bitleitungspaar übertragen.

WL : HIGH Die Auswahltransistoren werden leitend. Die Informationwird in die Zelle übertragen (Beispiel: BL = 0, BL = HIGH

⇒ Knoten 1 : Low

Knoten 2 : HIGH)

Anschließend WL : LOW

Typischer Lesezyklus

Bei CE = HIGH werden alle Signaleingänge unterbrochen und dieDatenausgänge hochohmig. Mit der H/L-Flanke von CE wird der

(VDD + US)

6 Halbleiterspeicher

Schaltkreis aktiviert (≤ 1,5 V), d.h. Adresseneingänge und Steuer-eingänge geöffnet und die anliegenden Adressen zwischengespeichert.

Je nach Zustand von WE und OE sind die Datenein- und -ausgängeaktiv. WE ist im High-Zustand.

Adressengesteuertes Lesen (OL = LOW)

Ai

1,5V

1,5V

1,5V

H

L

L

L

H

H

CE

OE

DQitd

td

hochohmig hochohmig

Ausgangsdatengültig

Adressen gültig Adressen gültig

Adr.+Steuerug geöffnet

Datenausgangaktiv

Output-enable-Zugriffszeit

tZykluszeit

0,8V

2,4V

Ai

1,5V

H

L

Adressen gültig

DQiAusgangsdatengültig

0,8V

2,4V

Zykluszeit

vorherigeAusgangsdaten

td1 td2

Schreib-Lese-Speicher (RAM) 7

Zeitsteuerung: Adressenübergangsdekoder

ADT = address transition detection

Jeder Adresseneingang wird mit seinem verzögertenWert verglichen. Aus allen ADTi Signalen wird ein ADTSignal generiert, das Adresse gültig übermittelt.

Typischer Schreibzyklus

OE = High

Ai

1,5V

H

L

Adressen gültig nächste Adresse

1,5V

1,5V

L

L

H

H

CE

WE

t CLCL

DQi

H

LDatenbusgeterennt

Datenbus getrennt

Schreiben ein

Schreibenabgeschlossen

Schreiben aus

Eingangsdaten gültig

8 Halbleiterspeicher

8.1.2. Dynamische Schreib-Lese-Speicher

DRAM

Speicherzelle (Eintransistorzelle)

Technologische Realisierung (bis 4 MBit)

WL(0,VDD+US)

BL(0,VDD)

VDD

UB

G

TA

SiO2

VDDWL(G)BL

Al

n+

p-Silizium

MOS -Transistor TA MOS -Kondensator

Schreib-Lese-Speicher (RAM) 9

Technologische Realisierung (ab 4 Mbit)

Schreiben

WL = HIGH, TA leitend, BL = VDD, 0

Beim Schreiben wird der Kondensator CS auf die Potentialdifferenz US =

VDD – URL aufgeladen:

LOW : US = VDD (UBL = 0)

n+n+

Poli-SiBL WL

p - Si

p+ - SiSiO2-Si3N4-SiO2

(ONO)

WL

BL

G

USCS

10 Halbleiterspeicher

HIGH : US = 0 (UBL = VDD)

Lesen

WL = HIGH, TA leitend

CS entlädt sich in die Bitleitung mit der Kapazität CBL

Lesen: Auswahl von UBL beim Lesen

)( BLSBLBLSS CCUCUUC +=⋅+⋅

BLS

BLBLSS

CCCUUC

U+

⋅+⋅=

CBL = 10 CS

Symmetrischer Spannungshub für

US = 0 und US = VDD

Auswahl von UBL ?

US = 5 V UBL + ∆U = U

US = 0 V UBL - ∆U = U

Es ergibt sich beim Lesen:

2DD

BL

VU =

BL

SDD

BLS

SDD

CCV

CCCV

U22

≅+

=∆

Bei UDD = 5 V und CS = 0,1 CBL ergibt sich: ∆U = 250 mV

1. Spannungsänderung an der Bitleitung ist gering, daher relativ großer

Aufwand für den Leseverstärker notwendig.

Schreib-Lese-Speicher (RAM) 11

2. Spannung über CS verändet sich beim Lesen (zerstörendes Lesen)

d.h. das gelesene Signal muß im selben Zyklus, d.h. solange TA

leitend ist, wieder eingeschrieben werden.

3. Deshalb muß jede Bitleitung über einen separaten Leseverstärker

verfügen.

4. Wegen Leckströmen nimmt die Ladung CS mit der Zeit ab. Es muß

alle 2 ms ... 8 ms eine Refreshperiode eingeleitet werden, d.h. alle

WL müssen einmal aufgerufen werden.

Beispiel: 1 M Bit DRAM 512 Zeilen

512 Refreshzyklen alle 8 ms Zykluszeit für den Refresh 200 ns Zeitbedarf Refresh: 512 x 0,2 µs = 0,1024 ms also 1,3 % der Betriebszeit

Struktur des DRAM (64 k Bit)

RAS row address select, Low, Zeilenadresse gültig

CAS colum address select, Low, Spaltenadresse gültig

Matrix 128x256

256 Lese

Matrix 128x256

Spaltenauswahl

Spaltendekodierer

Zei

lend

ekod

iere

r

Adress-puffer

Adress-puffer

TimingandControl

DIpuffer

DOpuffer

RAS

CAS

A0

A7

RASCASWERFSH

VDD

USS

12 Halbleiterspeicher

Bis zum 256 k Bit-Niveau wurde fast ausschließlich die „x1“ Organisation

angewendet, d.h. in jedem Aufruf wird nur 1 Bit ein- oder ausgegeben.

DI DateneingangDO DatenausgangWE write enable, Lese-Schreib-Steuerung

RFSH Refreshsteuerung

8.2. Halbleiter – Festwertspeicher

( Nur – Lese – Speicher, ROM – Read – only – Memories )RAM: Wahlfreier ZugriffROM: Fester Zusammenhang zwischen Eingangsvariablen (Adressen)und Ausgangsgrößen (gespeicherte Information)ROM≈elektrische ZuordnerVorteile von ROM:- Nichtflüchtigkeit- Gleicher bzw. höherer Integrationsgrad- Vergleichbarer Arbeitsgeschwindigkeit

Anwendungsgebiete:- Codeumsetzter- Mikroprogrammspeicher- Initialisierungsprogramme- Interpreter- Dateien ( Sprachübersetzung, Zeichengewratoren)

Einteilung der Halbleiterfestwertspeicher:

bipolare Festwertspeicher MOS-Festwertspeicher

markenpro- elektrisch pro- erasable PROM electricallygrammierbar grammierbar (UV-löschbar) erasable PROM ROM PROM EPROM EEPROM

Halbleiterfestwertspeicher

Halbleiter – Festwertspeicher 13

Schematischer Aufbau eines Halbleiterfestwertspeicher – Schaltkreises

(1 Mbit, 128k x 8Bit )

8.2.1. Markenprogrammierbare ROM

Bei diesen Festwertspeichern wird bei der Herstellung festgelegt, welcheKoppelelemente zwischen Wort – und Bitleitung eingeschaltet bzw.ausgeschaltet sind. Dazu wird eine Marke verwendet, diekundenspezifisch erstellt wird.Eine Änderung durch den Anwender istnach der Herstellung nicht mehr möglich.Eine Realisierung erfolgt heuteüberwiegend in MOS – Technik. Deshalb wird im Rahmen dieserVorlesung nur auf diese Realisierungsvariante eingegangen.

ADRESSENREG ISTER

ZE ILENDEKOD.

M ............ A T R I X1024 1024 1024 x x x 128 128 ............ 128

LV/SPALTENDEKODER

LV/SPALTENDEKODER

LV/SPALTENDEKODER

WL 0

1023

.

.

....

0

90 127 0 127 0 127

BL10

16

. . .

STEUEREINHEIT DATENAUSGABEREGISTER

............A10

A16

. . .

A9

A0

CE OE D7D0

VSS

VDD

14 Halbleiterspeicher

Typische Anordnung:

A) Programmierung durch Schwellspannungsverschiebung der

Transistoren nmT

V...V.ULOWBL S 150=≈ , Transistor leitet, wenn WL HIGH ist

VUHIGHBL S 5>≈ Transistor sperrt

VUS 5> wird erreicht durch zusätzliche Inplantation oder durch Ersetzendes dünnen Gateoxides durch das dickere Feldoxid )VU( S 51>

ZE ILENDEKOD IERER

SPALTENDEKODIERER

1

n

VDD VDD

WL1

WLn

T11

Tn1 Tnm

T1m

BLmBL1 ......

......

......

......

......

......

Halbleiter – Festwertspeicher 15

B) Programmieren durch Weglassen des Kontaktfensters zur Drain –Elektrode (Unterbrechung von BL zum Drainanschluß der Transistoren

nmT )

8.2.2. Elektrisch programmierbare ROM (PROM)

PROM werden vielfach wie EPROM hergestellt. Das Quarzfenster wirdweggelassen. Siehe Abschnitt. 8.2.3.

R: Poly – Si – Widerstand, hochohmig weil nicht dotiert. Eine hoheStromdicht beim programmieren führt zu einer Temperaturerhöhung unddamit zu einer As – Diffusion in den Widerstand. Es ergibt sich eineWiderstandsverringerung um 3 Zehnerpotenzen.

Programmierstrom < 10mA bei 10V, t < 5 µs

Es werden spezielle Programmiergeräte benötigt.

n+n+

PolySi: As dotiert

pR(0,2 - 0,6 µm)

R

WL

BL

16 Halbleiterspeicher

8.2.3. EPROM

PRINZIP: Speicherung der Ladung auf einer Gate – Elektrode, dieisoliert, d.h. vollständig in 2SiO eingebettet ist. Weil dieses Gate keinenelektrischen Anschluß hat, d.h. es weist ein schwebendes Potential auf,wird es „floating Gate“ genannt.

Durch das Aufladen des „floating Gate“ wird eine Verschiebung derSchwellspannung SU erreicht:

)Q(fUS =

Damit können die Leitungseigenschaften eines Transistors verändertund eine Programmierung erreicht werden.Die eingebrachte Ladung ist über 10 Jahre stabil.Eine Entfernung der Ladung des floating Gates ist mit elektrischenSignalen nicht möglich. Dies kann mit einer UV – Bestrahlung des Gateserreicht werden.Das Oxid wird mittels dieser energiereichen Strahlung ionisiert und dieLadung kann sich mit dem Substrat ausgleichen.Eine Löschung ist nur für den gesammten Schaltkreis möglich.Löschzeit : 3 - ... 20 min.UV – Licht: gHnm254=λ - DampflampeBeleuchtungsstärke: 210 cm/mW

Prinzipieller Aufbau (N – Kanal - EPROM -Zelle)

n+ n+

p - Si

WL

AL

SiO2

Poly-Si2Steuergate

Poly-Si1Floatieruggate

BLDrain

AL

MASSE

SiO2

Source

Halbleiter – Festwertspeicher 17

Transistorkennlinie:

Lesen: WL: HIGH (z.B. 4,3V)

nicht programmiert, Zelle leitend „1“

programmiert, Zelle gespert „2“

Programmieren:

Durch eine hohe Drain – Source – Spannung und eine hoheProgrammierspannung am Steuergate werden im leitenden Kanal„heiße“ Elektronen erzeugt, von denen ein Teil, unterstützt durch diepositive Spannung am Steuergate die Barriere zum „Floating Gate“überwinden können und dieses aufladen.

WLBL

"2"

4,3VUS1<1,5V US2= 7V UGS, UWL

"1"

gelöscht programmiert ID

18 Halbleiterspeicher

Beispiel: (1,2 µm, d Gate Oxi=30nm,dzw – Oxid=35nm

Die hohe elektronische Feldstärke beschleunigt die Elektronen. Siedurchtunneln das Oxid, wenn ihre Energie ausreichend ist. DieElektronen bauen sich ein Oxid – Poly – Si – Interface als festeLadungen ein. Die Schwellspannung steigt.

n+n+

+13V

+7V

-

--

_ _ _ _ _

n+ n+

ortsfeste negative Ladungen

Halbleiter – Festwertspeicher 19

Blockschaltbild eines EPROM

mk =2

nl =2

p: Wortlänge, Aufrufbreite )D...D( p 10 −

ADRESSENPUFFER

ADRESSENPUFFER

X-DEKODER

. . .

.

. . .

.

Y- DEKODER

DO DI

D0

m x nMatrix

l

X0

Xm-1

k

. . .

. . .

.

. . . . . .

. . . . . .

. . .

. . .

Y0 Yn-1

. . .

Dp-1. . . . . .

Al+k-1

m x n Matrix

XP

OEUPP

A0

Al-1

Al

UCC

20 Halbleiterspeicher

870 => pD...D

6426 == m

6426 == n

m x n = 4096

m x n . p = 32 k Bit

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

SS

UCC

A8

A9

A11

OE/UPP

A10

CE

D7

D6

D5

D4

D3

Halbleiter – Festwertspeicher 21

8.2.4. EEPROM

Elektrisch löschbare Festwertspeicher (electrically erasable PROM)erfordern eine Möglichkeit Elektronen in einen Speicherbereich zuinjizieren und von dort mittels elektrischer Signale wieder zu extrahieren.

MNOS – Speicher (Metall – Nitrid – Oxid – Semiconductor)Speichertransistor:

n+n+ n nn+

p - Wanne

n - Substrat

TA MNOS

BL WL 1 PWL PBL p-Wanne

Poly Si

AlAl

Si3N4

N-MOSFET *1 Metall-Nitrid-Oxid-SemicondactorAuswahltransistor (MNOS) Speichertransistor

MNOS

TA

BLPBLWL

PWL . . .

. . .

. . .

. . .

22 Halbleiterspeicher

Nichtprogrammiert:

Im nichtprogrammierten Zustand hat der NMOS - Transistor. einenegative Schwellspannung

VUSO 4−= (Eigenleitend)

Programmieren:

Es wird eine hohe Spannung an das Gate des ausgewählten MNOS -Transistors gelegt während Source, Drain und P – Wanne auf Massebleiben.

Durch die hohe Feldstärke zwischen Gate und Kanal (eigenleitend)können Elektronen aus dem Kanal durch das dünne Gateoxid (1,7 nm)zur Oxid – Nitrid – Grezfläche gelangen (tunneln) und sich dort alsortsfeste Ladungen festsetzen. Dadurch verschiebt sich dieSchwellspannung des Transistors zu höheren Werten

VUU SpSO 4+=→ (selbstsperrend)

PWL

PBL

UPWL>16V

n n-

MASSE

UP=+16V

Halbleiter – Festwertspeicher 23

Löschen:

VUU SSP 40 −=→

Schreiben:

8 Zellen benachbarter Zellen sind in getrennt ansteuerbaren P – Wannen

untergebracht. Zum unterbinden der Programmierung der Zellennichtausgewählter Bitleitungen muß die PBL dieser Spalten an einehohe Spannung VUi 16= gelegt werden.

Anschluß Löschen Programmieren

selektiert nicht selektiert selektiert nicht selektiert

P LL 0 Up Up 0

P BL Ui Ui 0 oder Ui Ui

P-Wanne Up 0 0 0

Lesen:

Beim Lesen sind PWL und PBL auf Masse

PWL = 0, PBL = 0

n n

-

Ui=+10V UP=+10V

PWL

PBL

UPWL>16V

>+10V=Ui >+10V=UP

24 Halbleiterspeicher

Die ausgewählte Zelle ist leitend, wenn sie nicht programmiert ist : „0“.

Sie ist nicht leitend, wenn sie programmiert ist: „1“.

Zustand MNOS – Ttransistor

Programmiert

nicht programmiert

gesperrt, kein Stromfluß

leitend, Stromfluß

Alternative Zellen für EEPROM:

Floating Gate EEPROM:

Schreiben: pph VS =

Drain auf hND

Tunnelstrom in das Gate ⇒ “1“ geschrieben

„0“ – Schreiben umgekehrt

n+ n+n n+

Steuergatefh

10-20nm

p - SiFloating AuswahlGate TransisrorTransistor TA

Halbleiter – Festwertspeicher 25

Flash – EEPROM (blitzartig)

• Schreibgeschwindigkeit mehrere MByte/s

• Anzahl zulässiger Schreib/Lese Vorgänge: > 510

• Einsatz: Speicherkasten, elektronische Kameras, Chip – Karten.

Programmieren: z.B. mst,s,VUp 110019 ≤µ=(Bitweise) VUsp 7+> Drain pU≅ Steuer Drain pU≅ Source V0≅

n+nn+

Source SiO2 Drain

Steuer-Gate

n+n+

p

-

19V

19V