Technische Informatik I (SS 2006) 1 Teil 4: Prozessoren 4c: Entwicklung.

-

Upload

evert-ratz -

Category

Documents

-

view

109 -

download

0

Transcript of Technische Informatik I (SS 2006) 1 Teil 4: Prozessoren 4c: Entwicklung.

Technische Informatik I (SS 2006) 1

Teil 4: Prozessoren

4c: Entwicklung

Technische Informatik I (SS 2006) 2

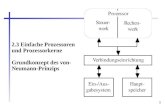

Von-Neumann-Rechner

John von Neumann hatte photografisches Gedächtnis hielt Vorlesung über Quantentheorie in Princeton 1943-45 Arbeit am Manhattan Projekt Los Alamos 1944 Buch über Spieltheorie 1946 „von Neumann-Rechner“

= Programm und Daten werden binär codiert und liegen in dem selben Speicher

1903-1957

Technische Informatik I (SS 2006) 3

auch Intel 80x86 SISD = single instruction single data

> SIMD, MISD und MIMD sind nicht von-Neumann Typ Prinzip

später: HARVARD Architektur (z.B. für DSPs)Programm- und Datenspeicher werden getrennt

Von-Neumann-Rechner

Technische Informatik I (SS 2006) 4

IBM

Aus Hollerith-Unternehmen hervorgegangen Herman Hollerith 1860-1929

Erfinder der Lochkarten(angewandt bei der Volkszählung 1890/91,dauerte 4 Wochen statt 7 Jahre) 1896 Tabulating Machine Company 1911 für 1,21 Mill. $ verkauft an

Computing Tabulating Recording Company (CTR) mit Sitz im Staat New York

1924 firmierte sich die CTR um in International Business Machines Corporation (IBM)

Stieg 1981 in das PC-Geschäft ein (Intel 8088, 20 MB Festplatte) Betriebsystem wurde in Auftrag gegeben.

1984 IBM PC-AT (Advanced Technology) (Intel 80286, 40 MB Festplatte)

Technische Informatik I (SS 2006) 5

IBM Deep Blue

Höhepunkt der RISC Architektur 1997 IBM RS/6000 RISC Architektur „SP“ = parallelisiert Garry Kasparov besiegt mit 3.5 zu 2.5 Spielen 200 million Züge pro Sekunde

oder50 Milliarden Positionen pro Sekundein 3 min (3 min = erlaubt für einen Zug)

Technische Informatik I (SS 2006) 6

Jack Tramiel, geboren 1929

gründet 1958 Commodore Ltd. zunächst Herstellung von Schreibmaschinen

(und größter Büromöbelhersteller in Kanada) 1969 Taschenrechner

C108, 8-bit, 4 Grundrechenartenbasierend auf Texas Instruments Chips(Texas Instruments Taschrenrechner nach 1972)

kauft 1976 von MOS TechnologyHalbleiterproduzenten(um unabhängig zu sein)

Technische Informatik I (SS 2006) 7

Commodore

C64programmierbar in BASIC

AMIGA, erster Homecomputer mit eingebauten DSPsfür Sounderzeugung

Amiga 1000, 1985,7.15909 MHz Motorola 68000 Prozessor

Prozessor austauschbar !(z.B. 6800068030)

1984 Tramiel verlässt CBM danach finanzielle Probleme

(Konkurrenz von IBM) 1994 Konkurs Reste 1995 von ESCOM gekauft

(1996 ebenfalls Konkurs)

Technische Informatik I (SS 2006) 8

Atari

Nolan Bushnell Erfinder von Pong

(Videospielkonsole) 1972 Atari gegründet 1976 Verkauf an Time Warner 1978 erste Heimcomputer 1982 Pac-Man 1984 von Tramiel gekauft 1996 aus dem Markt verdrängt

Technische Informatik I (SS 2006) 9

1985 Atari 520ST512kB Memory

1986 Atari 1040ST1024kB Memory

Prozessor Motorola 680008 MHz

Arbeitsspeicher von dem Speichercontrollerchip "MMU" verwaltet

erster Heimcomputermit MIDI

Atari

Technische Informatik I (SS 2006) 10

Apple

1976 gegründet von Steven Jobs + Steven Wozniak 1976 Apple I (MOS 6502 Prozessor wie in Z80,

8KByte Speicher Apple II (Farbe, 4-64kByte)

Casettenspeicher 1977 mit Diskette

1980 Apple III Finanzielles Desaster

1981 Steven Wozniak verunglückt 1984 Macintosh

Prozessor Motorola 68000 Graphische Oberfläche, mit Menüs

1998 iMac PowerPC Prozessor als resultat der

aim (apple, ibm, motorola) Allianz iPod

Technische Informatik I (SS 2006) 11

Ende Teil 8

Technische Informatik I (SS 2006) 12

Example:

4195835/3145727,

(discovered by Tim Coe of Vitesse Semiconductors) The correct value is

= 1.33382

while the Pentium's floating-point unit computed

= 1.33374

a relative error of 0.006%. One can easily test a Pentium using Microsoft's Windows and this example:

Use the Windows calculator in scientific mode to divide Coe's numbers and compare to the numbers above.

Beantwortung von Fragen: Intel Pentium Floating Point Unit Bug

Technische Informatik I (SS 2006) 13

How did all this get into the news? Thomas Nicely is a math professor at Lynchburg College, a school about

Willamette's size in Virginia. In summer/fall 1994, he was computing the sum of the reciprocals of a large collection of prime numbers on his Pentium-based computer. Checking his computation, he found the result differed significantly from theoretical values. He got correct results by running the same program on a computer with a 486 CPU, and finally he tracked the error to the Pentium itself. After getting no real response to his initial queries to Intel, and after checking his facts, Nicely posted a general notice on the Internet asking for others to confirm his findings. Magazine interviews and ultimately a CNN interview followed.

Intel publicly announced that "an error is only likely to occur [about] once in nine billion random floating point divides", and that "an average spreadsheet user could encounter this subtle flaw once in every 27,000 years of use."

Beantwortung von Fragen: Intel Pentium Floating Point Unit Bug

Technische Informatik I (SS 2006) 14

Beantwortung von Fragen: Intel Pentium Floating Point Unit Bug

Within a month IBM halted shipment on Pentium-based computers (which comprised only a small percentage of IBM's computer production) and announced that "Common spreadsheet programs, recalculating for 15 minutes a day, could produce Pentium-related errors as often as once every 24 days."

Intel's policy, when it first publicly admitted the problem around November 28 of 1994, was to replace Pentium chips only for those who could explain their need of high accuracy in complex calculations. (Being a math professor seemed to help.)

By late December Intel capitulated and announced a free replacement Pentium for any owner who asked for one.

Technische Informatik I (SS 2006) 15

SUN

Andreas von BechtolsheimBundessieger jugend Forscht (Physik 1974 – Fußball WM in BRD !)

1976 nach Stanford Idee: Rechner der Uni vernetzen

(baute Hardware dafür)S.U.N.= Stanford University Network

1982 Gründung von SUN mit Joy, Kholsa, McNealy

Entwicklung von SunOS, SPARC (=RISC Prozessor)

JAVA

Technische Informatik I (SS 2006) 16

ARM

Entwicklungprojekt (1983) von Acorn Computers ARM = Acorn Risc Machine Befehlssatz teilweise an 6502 angelehnt 1990: Gründung mit Apple etc.:

ARM = Advanced Risc Machineswww.arm.com

Lizenznehmer: Motorola, Intel, TI, … 1985-1998 im Besitz vo Olivetti Bsp. Cortex A-8

verbraucht bei 600 MHz nur 300 mW (!) Hoher Anteil im "Kleingeräte"-Bereich:

PDA, Mobiltelefone, Smartphones, in jedem iPodin jedem Tom Tom 300 GPS Navigationssystemin jedem Nintendo DS

Technische Informatik I (SS 2006) 17

DIGITAL

DEC = Digital Electronics Company gegründet 1957 von Ken Olsen und Harlan Anderson 1963 PDP-5, 12-bit 1976 VAX, 32-bit

(virtual address extension) 1998 verkauft an COMPAQ 2002 COMPAQ verkauft

an Hewlett-Packard

Technische Informatik I (SS 2006) 18

DIGITAL

DEC ALPHA Plattform 21264 Prozessor, z.B. DS-10 700 MHz in 1999 Haupt-Unterschiede zu Intel 8086:

64-bit Architektur keine Adressarithmetik der CPU

(d.h. die CPU rechnet keine Adressen aus)und nur LOAD/STORE darf auf memory zugreifen(„pseudo“ 64 bit = Tsunami-D Chip, Scheduler für 2 x 32 bit)

out-of-order-executionCPU verändert die Reihenfolge der letzten 80 instructionen für Optimierung> temporäre Register (renaming !)

RISC

Technische Informatik I (SS 2006) 19

Echtzeit-Rekonstruktion (t100 ms)von Au+Au Kollisionen

48 ALPHA DS-10 CPUs für sqrt() Operationen

Faktor ~1.7 schneller als Pentium(sqrt op-code)

Software:Track Finder(Erkennung von Teilchenspuren mit ~45 Punkten pro 1 Spur,~6000 Spuren pro1 Kollision)

Beispiel für eine Anwendung einer DEC ALPHA Farm:der STAR Level-3 Trigger

Technische Informatik I (SS 2006) 20

Beispiel für eine Anwendung einer DEC ALPHA Farm:der STAR Level-3 Trigger

1999 2003

Technische Informatik I (SS 2006) 21

Erste RHIC Kollisionen, 20.06.2000

Technische Informatik I (SS 2006) 22

Cray

1972 von Seymour Cray gegründet Supercomputer

Ziel: Rechenleistung im TFLOPS-Bereich (1 TFLOPS = 1012 Gleitkommarechnungen pro Sekunde)

1976 Cray-1, 160 MFLOPS, 64 Bit, Speichergröße 8 MB cycle time 12,5 ns entsprechend einer für die damalige Zeit enorm hohen Taktfrequenz von 80MHz

in BRD: FZ Jülich, Cray-2, 1989

Technische Informatik I (SS 2006) 23

Cray-2

Boards permanent „schwimmend“in nicht-leitender Kühl-FlüssigkeitPer-Flour-Carbon

Geschwindigkeit übernicht Taktfrequenz !nicht Multi-Prozessor !sondernVektor-Register !64 Werte auf einmald.h. in einem Taktzykluskann eine Rechenoperationmit allen 64 Werten auf einmal durchgeführt werden

spätere T3D benutzte DEC ALPHA Prozessoren

Technische Informatik I (SS 2006) 24

Was ist dies ?

Technische Informatik I (SS 2006) 25

Connection Machine

Daniel Hillis, geb. 1956 Thinking Machines

1983 gegründet Technologietransfer von MIT

1-bit Prozessoren(1 bit prozessiert pro Taktzyklus)

CM-265,536 Prozessoren

Hypercube Topologie !(Verbindungen in 4-dim)

Operating System UNIX Programmierung in LISP

(heute benutzt in emacs Editoren) 65,6 GFlops

Technische Informatik I (SS 2006) 26

Was ist RISC, was ist CISC ?

CISC = complex instruction set computer (z.B. Intel Pentium)RISC = reduced instruction set computer (z.B. DEC Alpha)

Jeder Prozessor hat mindestens 4 elementare Operationen pro 1 Befehl auszuführen: Daten vom Speicher holen Daten dekodieren (d.h. übersetzen, was für ein Befehl gemeint ist) Befehl ausführen Daten in die Register oder den Speicher zurück schreiben.

Für jede Stufe braucht ein Prozessor mindestens einen Taktzyklus, meistens aber mehr.

Wichtig: 1.) Die Daten vom Speicher zu holen dauert lange.

Speicherbausteine sind langsam im Vergleich zu einem Prozessor. 2.) Je mehr und je komplexere Befehle ein Prozessor hat,

desto länger dauert das Dekodieren

Technische Informatik I (SS 2006) 27

CISC

CISC Das Dekodieren dauert hier länger,

da der Code kein einheitliches Format hat, Als Ausgleich ist die Funktionalität der einzelnen Befehle höher,

d.h. „die Befehle können mehr“ (so daß weniger Befehle ausgeführt werden müssen,um die gleichen Aufgaben zu erfüllen)

Nebenbemerkung: aber der Code ist kürzer (d.h. weniger kB Binärcode pro Programm, und damit geringerer Speicherzugriff)

Viele Register sind wegen der Forderung nach kurzem Code nicht möglich. Die komplexen Befehle werden im Chip in einfachere Instruktionen zerlegt. Dafür gibt es Mikrocode (ROM auf dem Chip).

Auch die einzelnen Funktionseinheiten sind sehr mächtig, z.B. indem es Hardware Multipliziereinheiten gibt, die zwar schnell sind, aber auch viele Transistoren benötigen.

Technische Informatik I (SS 2006) 28

RISC

RISC Vorteil #1: viele Register Die Daten können in diesen gehalten werden.

Damit fallen die Angaben von Speicheradressen bei den meisten Befehlen weg.

Idealerweise gibt es nur einen Befehl, der direkt mit dem Speicher kommuniziert(load/store bzw. read/write) Alle anderen Befehl arbeiten mit Registern und sind so schnell.

RISC Prozessoren verfügen je nach Typ zwischen 32 und 256 Registern, die universell benutzt werden können.

CISC Typen wie der Motorola 680x0 oder Intel 80x86 haben 16 bzw. 12 Register.

Technische Informatik I (SS 2006) 29

RISC

RISC Vorteil #2: einheitliches Befehlsformat

(bzw. einheitlich Befehllänge) Es gibt verschiedene Befehle in einem Prozessor.

Manche benötigen Daten, andere keine. Bei einem CISC Prozessor wie dem 80386 kann ein Befehl z.B. so aussehen:ein byte, noch ein byte, und noch ein byte (oder vielleicht auch nicht),und weitere Daten können angehängt sein,selbst als „Bruchstücke“ ein 8 Bit, 16 oder 32 Bit Wert oder ein Offset – in dem folgenden Byte, Wort oder Doppelwort

Das macht das Dekodieren kompliziert. Mit anderen Worten:

Man kann nicht einfach jedes Byte stur nach demselben Schema dekodieren, denn es könnte sich auch um Daten oder den zweiten Teil eines Befehles handeln.

Technische Informatik I (SS 2006) 30

RISC

NebenbemerkungSo weit, so gut, aber:das Problem existiert prinzipiell auch bei RISC. JEDOCH versucht man es dort zu minieren durch Vorhersagen über das Ende des Befehles.

Beispiel: Jeder Befehl sollte exakt 6 Bytes lang sein: entweder im Format:

Befehl (1 Byte), Registernummer (1 Byte), Daten (immer 32 Bit) - für Befehle die vom und in den Speicher schreiben.

oder Befehl (1 Byte), Registernummern 1,2,3 (je 1 Byte), 2 Bytes ohne Daten

- für Befehle die mit Registern arbeiten. Maximal 3 Register werden bei Operationen wie add (Reg1=Reg2+Reg3) als Angabe benötigt. Es gibt aber auch Befehle mit nur einem oder gar keinem Register als Angabe.

Technische Informatik I (SS 2006) 31

RISC

Damit ist jeder Befehl 6 Bytes lang Auf den ersten Blick sieht dies nach Platzverschwendung aus:

Man brauchte bei 16 Bit Werten z.B. keine 32 Bits für Daten und bei den Registerbefehlen sind immer mindestens 2 Bytes nicht belegt.

Aber es gibt 2 große Vorteile: 1.) Das erste Byte ist immer ein Befehl, und das zweite ein Register,

man kann diese automatisch dekodieren. d.h. man muß sich keine Gedanken machen (wie bei CISC) was im zweiten Byte stecken könnte.

Technische Informatik I (SS 2006) 32

RISC

2.) der wichtigere Vorteil aber: Der nächste Befehl fängt garantiert 6 Bytes weiter an. Warum ist dies wichtig? Etwa zeitgleich mit RISC setzte man Pipelines in Mikroprozessoren ein. Pipelines holen die Daten, und fangen schon mal an zu dekodieren(während alles andere weiterläuft) Die Länge einer Pipeline gibt man in Stufen an. Bsp. Intel 80486: 5 stufige Pipeline, z.B. 5 Befehle in unterschiedlichen Stadien der Dekodierung im "Fluß". Wenn nun die Ausführungszeit des einfachsten Befehls 5 Takte beträgt, so kann eine solche Pipeline bei jedem Takt einen Befehl fertig dekodiert anbieten (weil die Dekodierung ja bereits in der Pipeline stattfand) und so die Performance steigern.

Technische Informatik I (SS 2006) 33

CISC vs. RISC

CISC Prozessoren müssen sich viel einfallen lassen, um die verschiedenen Kombinationsmöglichkeiten in einer Pipeline zu dekodieren. Die Pipelines sind dort lang, weil es so viele Möglichkeiten gibt (so ähnlich wie Schach) und man deswegen mehr Stufen braucht.

RISC Prozessoren wissen dagegen genau wo der nächste Befehl beginnt und können mehr automatisieren. Die Pipeline ist kürzer. Das ist vor allem von Vorteil, wenn ein Sprung im Programm kommt, denn dann stimmen alle Daten in der Pipeline nicht mehr (!).

Hat CISC gesiegt ? Nein. Heute mehr RISC als CISC.

Zwar CISC in Intel, aber Intel ist nicht alles:Druckerkontroller, in PDAs (RISC wegen des geringeren Stromverbrauchs wegen weniger Transistoren), in Spielkonsolen, und im zahllosen Elektronikbauteilen im Auto. (Ein Mittelklassewagen besitzt zwischen 13 und 30 Mikroprozessoren, die meisten als Embedded Systems).