Zinc Oxide Thin Film Transistors by Radio Frequency ... · Zinc Oxide Thin Film Transistors by...

Transcript of Zinc Oxide Thin Film Transistors by Radio Frequency ... · Zinc Oxide Thin Film Transistors by...

Zinc Oxide Thin Film Transistors by

Radio Frequency Magnetron Sputtering

(Zinkoxid-Dünnschichttransistoren

mittels Hochfrequenz-Magnetron-

Kathodenzerstäubung)

Der Technischen Fakultät

der Friedrich-Alexander-Universität Erlangen-Nürnberg

zur Erlangung des Grades

DOKTOR – INGENIEUR

vorgelegt von

Jiaye HUANG

aus Shanghai

Als Dissertation genehmigt von

der Technischen Fakultät der

Friedrich-Alexander-Universität Erlangen-Nürnberg

Tag der mündlichen Prüfung:

Vorsitzende des Promotionsorgans:

Gutachter:

20.10.2014

Prof. Dr.-Ing. Marion Merklein

Prof. Dr. rer. nat. Lothar Frey

Prof. Dr.-Ing. Peter Wellmann

v

Abstract

The major goal of this work is to investigate the electrical and morphological characteristics of single ZnO thin film transistors (TFTs) and construct basic logic circuits based on ZnO TFTs. In this work, zinc oxide (ZnO) thin films are fabricated by RF magnetron sputtering method. The working principle of ZnO TFTs with respect to traditional silicon MOSFETs is discussed and a model combining MOSFET with accumulation channel and JFET with insu-lated gate is included to understand the electrical behavior of ZnO TFTs. During sputtering processes, the influence of sputtering parameters on the sputtering rate is investigated. Sput-tering parameters include oxygen flow rate, total pressure, sputtering power, and substrate-to-target distance. Effects of these sputtering parameters on the ZnO electrical characteris-tics such as bulk resistivity are also analyzed. Morphological and electrical characteristics of ZnO TFTs after post deposition annealing in both oxygen and forming gas atmosphere in the temperature range of 400°C to 500°C are investigated. The ZnO layer after annealing shows polycrystalline morphology and the grain size tends to increase with increasing temperature in both oxygen and forming gas atmosphere. The threshold voltage decreases and the satu-ration mobility increases with increasing temperature in both cases. The correlations be-tween ZnO layer properties and electrical characteristics after annealing are investigated. With the decrease in the interface trap density and grain boundary trap density, the threshold voltage and turn-on voltage of the ZnO TFTs decrease while the saturation mobility increas-es after both oxygen and forming gas annealing. Besides the reduction of trap density, incor-porated hydrogen during forming gas annealing acts as shallow donors and thus ZnO TFTs in forming gas annealing show an even higher mobility and lower threshold voltage than the TFTs annealed at same temperature in oxygen. ZnO TFTs are also demonstrated in this work to construct NMOS enhancement load inverters. The inverter gain increases with sup-ply voltage and is limited by the off currents in single ZnO TFTs. An additional modification mask with the possibility to modify the ZnO active channel layer through different annealing steps or ion implantation is included in this work and a boost in inverter gain is realistic with the integration of the modification mask to realize NMOS depletion load inverters.

vii

Zusammenfassung

Das wichtigste Ziel dieser Arbeit war es, die elektrischen und morphologischen Merkmale von ZnO-Dünnschichttransistoren (TFTs) zu untersuchen und grundlegende Logik-Schaltungen auf Basis von ZnO-TFTs zu konstruieren. In dieser Arbeit wurden Zinkoxid (ZnO)-Dünnschichten mittels RF-Magnetron-Kathodenzerstäubungs-Verfahren hergestellt. Das Funktionsprinzip von ZnO-TFTs wird im Vergleich zu herkömmlichen Silizium-MOSFETs diskutiert und ein Modell zur Kombination eines MOSFETs mit Akkumulationskanal und eines JFETs mit isoliertem Gate wird beschrieben, um das Stromverhalten in ZnO-TFTs zu verstehen. Bezüglich der Sputterverfahren wird der Einfluss der Prozessparameter auf die Sputterrate untersucht. Sputterparameter beinhalten Sauerstoffdurchfluss, Gesamtdruck, Sputterleistung und Abstand zwischen Substrat und Target. Die Auswirkungen dieser Sputterparameter auf die elektrischen Eigenschaften des ZnO, wie spezifischer Widerstand, werden ebenfalls analysiert. Morphologische und elektrische Eigenschaften von ZnO-TFTs nach der Temperung in Sauerstoff- und Formiergasatmosphäre im Temperaturbereich von 400 °C bis 500 °C werden untersucht. Die ZnO-Schicht weist nach der Temperung polykristalline Morphologie auf und die Korngröße nimmt sowohl unter Sauerstoffatmosphäre als auch unter Formiergasumgebung mit steigender Ausheiltemperatur zu. Die Einsatzspannung verringert sich und die Sättigungsbeweglichkeit erhöht sich mit zunehmender Temperatur in beiden Fällen. Der Zusammenhang zwischen ZnO-Schichteneigenschaften und elektrischen Eigenschaften nach der Temperung wird beschrieben. Mit der Abnahme der Haftstellendichte verringern sich die Einsatzspannung und die Einschaltspannung der ZnO-TFTs, während die Sättigungsbeweglichkeit nach der Sauerstoff- und Formiergastemperung steigt. Neben der Reduzierung der Haftstellendichte wird während der Formiergastemperung Wasserstoff in das ZnO eingebaut, der als flacher Donator wirkt. Somit zeigen in Formiergas getemperte ZnO-TFTs eine höhere Beweglichkeit und niedrigere Einsatzspannung als bei gleicher Temperatur in Sauerstoff getemperte Proben. Des Weiteren wird in dieser Arbeit die Konstruktion von NMOS-Invertern mit Anreicherungs-Lasttransistoren demonstriert. Das Inverteramplitudenverhältnis erhöht sich mit der Versorgungsspannung und wird durch die Off-Ströme in einzelnen ZnO-TFTs beschränkt. Eine weitere Maskenebene mit der Möglichkeit, den aktiven ZnO-Kanal des Last- oder Schalttransistors durch zusätzliche Temperschritte oder Ionenimplantation zu ändern, wird in dieser Arbeit beschrieben. Mit der Integration der Modifikationsmaske erscheint die Realisierung eines NMOS Verarmungs-Last Inverters und eine Erhöhung des Inverteramplitudenverhältnisses realistisch.

ix

Acknowledgments

I would like to express my gratitude to my supervisor at the Friedrich-Alexander-University Erlangen-Nuremberg, Prof. Dr. Lothar Frey, for granting me the opportunity to carry out the research presented in this work, as well as for his guidance during my research and writing of this thesis. I would also like to thank Prof. Dr. Peter Wellmann for his careful co-examination on this thesis.

I would also like to thank the head of the technology department at the Fraunhofer IISB, Dr. Anton Bauer, for his support during my research project.

Special thanks go to the printed electronics group at the Fraunhofer IISB and the chair of electron devices at the Friedrich-Alexander-University Erlangen-Nuremberg. Without support and guidance from all the members in this group I would not be able to conduct this research and successfully complete my thesis. Big thanks go to Dr. Michael Jank for his care and support for my research work. I am very grateful to him for his discussion about experimental results and his corrections for the thesis. I would also express my sincere gratitude to all my colleagues in the group including Dr. Martin Lemberger, Dr. Susanne Oertel, Anke Haas, Erik Teuber, Dr. Simon Lukas, Dr. Sabine Walther, Sebastian Polster, Sebastian Weis, and Bern-hard Meyer.

Besides, I would like to thank all the colleagues with whom I had the pleasure to work with. In particular, I would like to thank Christian Strenger, Dr. Johannes Laven, Dr. Azinwi Fet, Dr. Vincent Lorentz, Sieglinde Elsesser, Angela Meixner, Dr. Elke Meißner, Dr. Volker Häublein, Christian Heilmann, Martin Heilmann, Stefan Knopf, Erich Pauer, Herbert Hofmann, Anette Daurer, Dr. Joachim vom Dorp, Dr. Holger Schwarzmann, Dr. Tobias Erlbacher.

Big love and many thanks go to my father Guoliang Huang, my mother Lexin Zhang for their support, patience and love during my thesis. Without them I would never be able to success-fully complete my thesis.

xiii

Contents

1 Introduction ........................................................................................................................ 1

2 Theory ................................................................................................................................. 7

2.1 Material properties of ZnO ............................................................................................ 7

2.1.1 General properties of ZnO as a semiconductor .................................................. 8

2.1.2 Defects and impurities in ZnO ............................................................................ 9

2.1.3 P-doping in ZnO ............................................................................................... 13

2.2 Thin film transistors .................................................................................................... 15

2.2.1 Comparison of Si MIS capacitors and ZnO MIS capacitors ............................. 15

2.2.2 Comparison of Si MOSFETs and ZnO thin film transistors .............................. 23

2.2.2.1 MOSFETs theory ................................................................................. 23

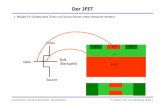

2.2.2.2 Junction FET theory ............................................................................ 27

2.2.2.3 ZnO thin film transistors ....................................................................... 30

2.3 Sputtering as a thin film deposition method ............................................................... 33

2.3.1 Basic sputtering mechanisms ........................................................................... 33

2.3.1.1 Direct current (DC) sputtering .............................................................. 35

2.3.1.2 Radio frequency (RF) sputtering ......................................................... 36

2.3.1.3 Magnetron sputtering ........................................................................... 37

2.3.1.4 Reactive sputtering .............................................................................. 37

2.3.2 Effects of processing parameters on the properties of sputtered ZnO layers .. 38

2.4 Logic circuits ............................................................................................................... 40

3 Experimental methods ..................................................................................................... 49

3.1 Sputtering equipment ................................................................................................. 49

3.2 Test structures ............................................................................................................ 51

3.3 Physical characterization methods ............................................................................. 54

3.3.1 Ellipsometry ..................................................................................................... 54

3.3.2 Atomic force microscopy ................................................................................. 56

3.3.3 Scanning electron microscopy ......................................................................... 56

3.3.4 Transmission electron microscopy .................................................................. 57

3.3.5 X-ray diffraction ............................................................................................... 58

xiv CONTENTS

3.4 Electrical characterization methods ............................................................................ 58

3.4.1 Electrical characterization ................................................................................ 58

3.4.2 Evaluation of electrical characterization results ............................................... 60

3.4.3 Extraction of electrical parameters .................................................................. 62

4 Results and discussions ................................................................................................. 63

4.1 Influence of sputtering parameters on properties of ZnO films ................................... 63

4.1.1 Influence of sputtering parameters on the deposition rate of ZnO films .......... 63

4.1.2 Influence of sputtering parameters on electrical characteristics of ZnO TFTs 66

4.2 Effects of annealing on morphological changes of ZnO layers .................................. 71

4.3 Effects of annealing on electrical characteristics of ZnO TFTs .................................. 79

4.3.1 Shadow mask design ...................................................................................... 79

4.3.2 Effects of forming gas annealing ..................................................................... 80

4.3.3 Effects of oxygen annealing ............................................................................ 82

4.3.4 Comparison of oxygen and forming gas annealing ......................................... 84

4.4 Inverter characterization ............................................................................................. 89

4.4.1 Characterization of the inverter ....................................................................... 89

4.4.2 Perspective of realization of depletion-load NMOS inverters .......................... 93

5 Conclusion and outlook .................................................................................................. 97

Bibliography ....................................................................................................................... 101

List of symbols ................................................................................................................... 117

List of abbreviations .......................................................................................................... 123

Index .................................................................................................................................... 125

List of own publications .................................................................................................... 127

Curriculum vitae ................................................................................................................. 129

1

Chapter 1

Introduction

Since the realization of the first metal-oxide-semiconductor field-effect transistor (MOSFET) by D. Khang and M. Atalla from Bell Labs in 1959 [Kha63], there have been tremendous in-novations and inventions for semiconductor devices. Shortly after the invention of MOSFET, C. Sah and F. Wanlass from Fairchild Laboratory developed the first logic circuit combining p-channel and n-channel MOS transistors in a complementary symmetry circuit configuration in 1963, which is known as the first CMOS device [Wan63]. The idea of integrated circuit (IC) was first presented by J. Kilby in 1958 [Kil76]. With the invention of CMOS technologies and the concept of IC, it is possible to integrate thousands of MOSFETs on chips with the size of a thumbnail. The development of the IC is described by Moore’s law which states that the number of transistors which can be placed on one single integrated circuit doubles approxi-mately every two years [Moo65]. Moore’s law holds true with the continuous improvement in semiconductor fabrication technology and consistent reduction in the dimensions of the sem-iconductor devices. The two important factors in semiconductor industry are the performance of the device such as the switching speed in the IC and the cost of the production. In order to achieve increasing device performance with decreasing fabrication cost, the focus of silicon technology lies strongly on application fields with high integration density and high power density such as dynamic random-access memory (DRAM) and processors. The technology node and minimum dimensions for high performance logic and memory is defined by experts within the framework of the International Technology Roadmap for Semiconductors [Itr11]. State-of-the-art semiconductor technology features a 40 nm half-pitch for DRAM and logic devices and a 22 nm gate length, which is defined as 22 nm technology node [Itr11].

In silicon technology, important process steps with high temperatures are used to achieve different goals. High quality field oxide is grown at up to 1000°C and annealing after ion im-plantation to reduce the implantation damage involves a process temperature as high as about 1100°C. These high temperature processes hinder the application of a large amount of substrates which can only endure a much lower process temperature, such as glass sub-strates, papers, and plastic foils. With the versatility of the applications involved in semicon-ductor technology, substrates compatible with low process temperatures play a more and more important role in the semiconductor fabrication technology, such as in printed electron-ics and transparent electronics. In order to meet the increasing demands in these applica-

2 CHAPTER 1: INTRODUCTION tions, thin film transistors (TFTs) which can be deposited on both silicon substrates and other substrates mentioned above are developed and fabricated. The first actual realization of a TFT was reported by P. Weimer in 1961 and fabricated by depositing cadmium sulphide (CdS) as a channel layer via vacuum evaporation [Wei62]. In

the early 1970’s, Brody et al. reported a successful realization of a 6×6 inch 20 lines-per-inch liquid-crystal display (LCD) panel based on TFT pixel drivers [Bro73]. It consisted of 14000 interconnected thin film transistors in which cadmium selenide (CaSe) was deposited as the active channel layer. CdSe TFTs exhibit high electron mobility and high speed operation, however, some serious problems have been revealed such as stability and toxicity problems [Ohs89]. In spite of many successful demonstrations of CdSe TFT LCDs, good candidates have been found out due to the stability and toxicity problems. Amorphous silicon (a-Si) thin film was proved to provide p-n junctions by compensating dangling bonds with hydrogen in 1975 [Spe75]. Since the first demonstration of a-Si:H TFT by LeComber et al. [Lec79] in 1979, there has been continuous improvement in a-Si:H TFT fabrication process and its ap-plication in LCD industry. Another important semiconductor material for TFTs is polycrystal-line silicon (poly-Si). Although amorphous silicon TFTs are widely used in active-matrix ad-dressed LCDs, poly-Si TFTs have better electrical characteristics than amorphous silicon TFTs, including higher mobility and lower photocurrent [Ser89]. The Poly-Si TFT reported by Serikawa et al. [Ser89] has an excellent mobility of about 350 cm2/Vs. However, the poly-Si TFTs have anomalous leakage currents, which decrease the on/off current ratio of the drain current [Ong82]. Rising costs of materials and manufacturing as well as increasing focus on more environmentally friendly electronics materials have triggered the development of organ-ic based electronics. Koezuka et al. [Koe87] reported the first organic field-effect transistor by utilizing polythiophene as an active semiconducting material in 1987. Organic TFTs have the advantage of reducing the processing temperature and fabrication cost compared to a-Si TFTs and offer the possibility of roll-to-roll manufacturing [Gel10, Bra09]. Nevertheless, the relatively low mobility (< 1 cm2/Vs ) and inferior bias stability of organic TFTs may limit their practical applications in flexible electronics [Mat99, Str09]. Although TFTs matured later than silicon integrated circuits, the TFT technology has ex-panded into a huge industry based on display applications with amorphous and polycrystal-line silicon as the incumbent technology in recent years [Str09]. A-Si TFTs, poly-Si TFTs, and organic TFTs mentioned above have been widely studied and used in the technology. How-ever, each of these three types of TFTs has its own drawbacks, such as the relatively low mobility and inferior bias stability of a-Si and organic TFTs [Mat99, Str09], and high thermal budget (> 450°C) as well as an expensive crystallization and doping process for fabrication of poly-Si TFTs [Ser02, Jeo07a]. Therefore, metal oxide TFT technology has recently gained considerable attention due to its high mobility, low temperature capability, good transparency to visible light, and relatively low fabrication cost [Jeo11]. Metal oxide TFTs can be fabricated without crystallization and intentional doping process and, therefore, they may replace poly-Si TFTs which have a high fabrication cost [Jeo11]. The state-of-the-art electrical characteris-tics such as field-effect mobility , threshold voltage and subthreshold slope of some common metal oxide TFTs are summarized and compared in table 1.1.

3

Table 1.1 A comparison of important electrical characteristics for various metal oxide TFTs including zinc oxide (ZnO), gallium indium zinc oxide (GIZO), hafnium indium zinc oxide (HIZO), and aluminum tin zinc indium oxide (AT-ZIO) TFTs [Joe11].

Oxide semi-conductor

Field-effect mobility (cm2/Vs)

Threshold voltage (V)

Subthreshold slope (V/dec)

On/off cur-rent ratio

Reference

ZnO 27 19 1.39 3 × 105 [For04]

IGZO 12 1.4 0.20 1 × 108 [Yab06]

IGZO 19.3 0.59 0.35 1.5 × 107 [Jeo07b]

HIZO 10 -4.7 0.23 108 [Kim09] AT-ZIO 31.9 -0.2 0.07 2 × 109 [Yan10]

Due to the excellent electrical performances of metal oxide TFTs, not only academia but also major companies in consumer electronics market, like LG or Samsung, have drawn consid-erable attention to the development of commercial products using metal oxide TFTs technol-ogy and concept [Pea12]. One of the most promising applications is flexible displays. Sam-sung has produced the first 22’’ transparent LCD panels which are utilized for advertising in shop windows and outdoor billboards, as shown in Fig. 1.1 (a) [Www12]. Ito et al. [Ito08] from Toppan Printing have developed a 4’’ full-color electronic paper with a resolution of 200 pix-

els per inch (ppi) and a QVGA resolution (640 × 480 pixels). Park et al. of Samsung Mobile Display [Par09] have reported a 6.5’’ flexible full color top emission AMOLED display on a

polyimide substrate with 160×RGB×272 pixels, shown in Fig. 1.1 (b).

(a) (b) Figure 1.1: (a) Transparent LCD display produced by Samsung [Www12] and (b) images displayed by a 6.5’’ flexible full color top emission AMOLED display. The display is bent to a curvature approximately 2 cm [Par09]. Figure 1.1 (b) is reproduced with permission from [Par09]. Besides the explosive development of metal oxide TFTs in flexible displays, circuit applica-tions have also confirmed the superior electrical characteristics provided by metal oxide TFTs. Their dynamic operation characteristics have been examined by using benchmark circuits such as ring oscillators and display pixel circuits [Kam10]. Canon has developed a fast five-stage ring oscillator using amorphous IGZO TFTs featuring a 419 kHz oscillation under a 18 V supply voltage [Ofu07]. Canon also successfully demonstrated OLED pixel driv-

4 CHAPTER 1: INTRODUCTION ing at a frame rate of 120 Hz [Hay07]. Görrn et al. demonstrated operation of transparent OLED pixels using amorphous zinc tin oxide (a-ZTO) TFTs [Gör06]. Both flexible displays and circuit applications require high-density integrated metal oxide TFTs. When scaling down the size of individual TFTs, short channel effects [Tau98] which mostly relate to the decrease of the threshold voltage with decreasing channel length are examined for metal oxide TFTs. Song et al. [Son08] from Samsung Advanced Institute of Technology have successfully demonstrated amorphous IGZO TFTs with short channel lengths of 50 nm without suffering from short-channel effects. An indium zinc oxide (IZO) TFT with a short channel length of 1 µm and drain-to-source distance of 2.5 µm has been fabricated by RF magnetron sputtering at room temperature [Wan08]. The device has a high-frequency operation of up to 180 MHz [Wan08]. This property of down scalability to a chan-nel length of 1 µm or even shorter without suffering from short channel effects makes metal oxide TFTs very promising for applications in integrated high-density memory devices [Kam10].

Among the metal oxide semiconductor materials investigated up to now, ZnO has been wide-ly investigated due to its wide band gap, large and easy availability, and its compatibility with semiconductor fabrication technology. The first ZnO field-effect transistor was announced by Boesen et al. in 1968 utilizing lithium doped single crystal of ZnO [Boe68]. ZnO thin films can be fabricated by different techniques such as chemical vapor deposition (CVD) [Tik80, Kas81] or molecular-beam epitaxy [Hei07, Dad04]. The most common method for depositing ZnO thin films is magnetron sputtering [Hac94, Gar98]. Compared to other methods, magne-tron sputtering has the advantage of depositing homogeneous ZnO thin films at room tem-perature and better control of film stoichiometry and resistivity by optimizing sputtering pa-rameters. By using magnetron sputtering at room temperature, Fortunato et al. [For05] have demonstrated a fully transparent ZnO thin film transistor which exhibits a high saturation mo-

bility of about 20 cm2/Vs and a high on/off drain current ratio of 2 × 105. This work focuses on thin film transistors and their applications based on radio frequency (RF) magnetron sputtered ZnO thin films. ZnO thin films are sputtered at room temperature from a ZnO target. Oxygen is used as a reactive gas during magnetron sputtering and ZnO TFTs are fabricated by using defined test structures. Chapter 2 first discusses the general properties of ZnO including intrinsic defects and impurities in ZnO and their roles for n- and p-type doping. Later on in chapter 2, comparison and common models for classical MOSFETs and ZnO TFTs are followed by the discussion of sputtering mechanisms and the working principle of basic logic circuits. In chapter 3, the sputtering equipment used in this work is introduced. Basic test structures as well as physical and electrical characterization methods for ZnO thin films and TFTs are also included in chapter 3. Chapter 4 first investi-gates the dependence of sputtering rate and the electrical properties of fabricated ZnO TFTs on the sputtering parameters such as oxygen flow rate, RF sputtering power, total pressure, and substrate-to-target distance. A thorough discussion about post deposition annealing ef-fects on ZnO thin films and TFTs is conducted. The structural changes in ZnO films after an-nealing in oxygen or forming gas including crystallinity, residual stress, and grain size are investigated by X-Ray Diffraction (XRD), scanning electron microscopy (SEM), transmission electron microscopy (TEM), and atomic force microscopy (AFM). Furthermore, the effects of post deposition annealing in both oxygen and forming gas atmosphere on electrical charac-

5

teristics of ZnO TFTs are demonstrated. This helps understanding the different roles of oxy-gen and hydrogen in ZnO thin films. Last but not least, an enhancement NMOS inverter which consists of two ZnO TFTs as load and driver transistors is realized. Although optimiza-tion for better inverter performance is necessary in future work, this shows the potential of ZnO TFTs in circuit applications. Chapter 5 makes the conclusion for the work and future perspectives and possible optimization are also given in order to further expand the material properties of ZnO and its applications such as in transparent electronics and flexible dis-plays.

7

Chapter 2

Theory

2.1 Material properties of ZnO Being initially considered as a substrate for GaN and related alloys, the availability of high-quality large bulk single crystals, the strong luminescence demonstrated in optically pumped lasers, and the prospects of gaining control over its electrical conductivity have led a large number of research groups to turn their interest on ZnO as an optoelectronic or electronic material in its own right [Jan09a]. The high electron mobility, high optical transmittivity and high conductivity, high electromechanical coupling coefficients, wide and direct band gap, and large exciton binding energy make ZnO attractive for a wide range of devices, including light-emitting diodes, optically pumped lasers, transparent conducting oxides and TFTs, and piezoelectric devices [Özg10]. In many respects, ZnO is considered to be a good alternate to GaN for device applications due to its relatively low production cost and superior optical properties [Özg10]. Comparing to GaN, ZnO has a huge advantage of availability of large single crystals [Jan09a]. GaN is usually grown on sapphire with a large lattice mismatch of ~16%, which leads to an extremely high concentration of extended defects (106-109 cm-2) [Nak00]. The epitaxy of ZnO films on native substrates can lead to ZnO layers with reduced concentration of extended defects and, consequently, better performance in electronic and photonic devices [Loo01, Özg05, Oga05, Nic05, Jag06]. Another big advantage of ZnO over GaN is the amenability to wet chemical etching, which is particularly favourable in the device design and fabrication process [Loo01, Jan09a]. Due to these advantages, ZnO gradually becomes superior to GaN and replaces it in the device applications. However, problems con-cerning the reproducibility and the stability of p-type doping remain to be the most difficult obstacle to realizing bipolar ZnO-based devices [Özg10]. In the following section, the general properties of ZnO involving several characteristics which make ZnO a very attractive candidate for semiconductor device applications are first intro-duced. Then the source of unintentional n-type doping in ZnO and possible methods as well as remaining challenges in achieving p-type doping are discussed.

8 CHAPTER 2: THEORY

2.1.1 General properties of ZnO as a semiconductor ZnO is an II-VI compound semiconductor whose bonding status lies at the border of covalent bonding and ionic bonding with an ionicity value of 0.616 in the Phillips scale [Phi70]. There are three possible crystal structures of ZnO, namely wurtzite, zinc blende, and rock salt. At ambient conditions, the thermodynamically stable phase is the wurtzite structure [Özg05]. Besides the wurtzite structure, ZnO is also known to crystallize in the zinc blende structure or the rock salt structure, which is shown in Fig. 2.1. The zinc-blende ZnO structure can be stabilized only by growth on substrates with corresponding crystal structures such as GaAs(001) [Ash00], and the rock salt structure is only obtained at relatively high pressures [Des98]. The wurtzite structure has a hexagonal unit cell with two lattice parameters, and , and belongs to the space group of or P63mc. The values of lattice parameters = 3.252

and = 5.213 are reported by Reynolds [Rey96].

Figure 2.1: Schematic description of different ZnO crystal structures: (a) the rock salt struc-ture, (b) the zinc blende structure. O atoms are shown as grey spheres and Zn atoms as black spheres. Only one unit cell is illustrated for clarity [Jag06]. ZnO has a direct and wide band gap in the near-UV spectral region [Vog95]. The band gap of ZnO is 3.44 eV at low temperatures and 3.37 eV at room temperature [Man95]. For com-parison, the respective values for wurtzite structure GaN are 3.50 eV and 3.44 eV [Mad96]. Owing to its direct wide bandgap, ZnO has been widely used in short wavelength optoelec-tronic applications, including light-emitting diodes, laser diodes, and optical waveguides [Lu06]. Some of the optoelectronic applications of ZnO overlap with that of GaN while ZnO has some advantages over GaN including the availability of fairly high-quality ZnO bulk sin-gle crystals and a large exciton binding energy (~ 60 meV) [Özg05]. This large exciton bind-ing energy indicates that efficient excitonic emission in ZnO can persist at room temperature or even at higher temperatures [Rey96, Bag97]. The sustainable excitonic emission and re-combination therefore enables lasing applications. In summary, the large exciton binding energy makes ZnO one of the most promising materials for optical devices and applications

2.1 MATERIAL PROPERTIES OF ZNO 9

that are based on excitonic effects [Jan09a]. However, ZnO still faces strong competition when faced with GaN. One of the disadvantages of ZnO over GaN is the less maturity in terms of devices. GaN device technology is much more mature as GaN-based very high-performance electronic and optical devices have already been commercialized [Özg10]. ZnO can be fabricated both as large single crystals and polycrystalline thin films depending on its detailed applications and relevant characteristics. Single crystals can be grown by dif-ferent methods including hydrothermal growth [Sek00], vapour-phase transport [Loo97], and pressurized melt growth [Rey04, Nau05]. Deposition of ZnO thin films can be realized by using chemical vapour deposition (CVD) [Tik80, Kas81] or molecular-beam epitaxy [Hei07, Dad04]. The most common method for depositing ZnO thin films is magnetron sputtering [Hac94, Gar98]. Comparing with the methods used for fabrication of single ZnO crystal bulks, magnetron sputtering has an advantage of fabricating ZnO thin films at low temperatures or even at room temperature [For05]. Besides the low temperature processing conditions pro-vided by magnetron sputtering, thin film transistors (TFTs) with sputtered ZnO thin films are often reported to have high mobility values and high / ratios. Fortunato et al. [For05]

have reported a high saturation mobility of about 20 cm2/Vs for the ZnO TFTs fabricated by radio frequency (RF) magnetron sputtering. Carcia et al. [Car03] have demonstrated a trans-parent ZnO TFT fabricated by magnetron sputtering near room temperature with the device on/off ratio > 106. The same research group has later reported the realization of ZnO TFTs on a flexible Kapton substrate with a saturation mobility of about 50 cm2/Vs [Car05]. Regard-ing to the fabrication of ZnO thin films, the amenability to wet chemical etching provides the possibility to structure the ZnO layer with ease. Acidic, alkaline as well as mixture solutions can be used to etch ZnO thin films [Jan09a]. In summary, ZnO has provided new insights from both material aspects and application as-pects. Although GaN films are earlier commercialized, ZnO has the advantage of a larger exciton binding energy of about 60 meV which makes it attractive for optical applications. Silicon technology and fabrication of amorphous silicon (Si) TFTs and polycrystalline Si TFTs are mature technologies. However low-temperature magnetron sputtered ZnO TFTs have advantage due to the fact that the maximal reported mobility value for amorphous silicon TFTs are about 1 cm2/Vs and the polycrystalline Si is normally fabricated under very high temperatures. Besides the applications mentioned above of ZnO thin films for transparent TFTs, more complicated electronic applications such as inverters and ring oscillators based on ZnO TFTs with high inverter gains and low propagation delays are also reported recently [Oh10, Sun08].

2.1.2 Defects and impurities in ZnO ZnO shows n-type conductivity regardless of deposition methods and its morphology. The cause of this intrinsic n-type doping is widely investigated and many researchers attribute n-type doping to the intrinsic defects inside ZnO including oxygen vacancies and zinc intersti-tials [Har54, Hut57, Tho57, Moh61, Hag76]. However, recent studies by density-functional calculations have demonstrated that the cause of n-type doping may not be due to oxygen vacancies and zinc interstitials [Koh00, Wal01, Jan05, Jan06, Jan07a, Vla05a, Vla05b]. In-stead of intrinsic defects, impurities such as hydrogen may be the cause of the unintentional

10 CHAPTER 2: THEORY n-type conductivity [Wal00, Jan07b]. The research of determining the cause of n-type doping is still under discussion. The two main sources which can influence the electrical conductivity are intrinsic defects and impurities. A discussion of intrinsic defects will be followed by inves-tigation of possible impurities which can contribute to n-type conductivity. Intrinsic defects are defined as imperfections in the crystal lattice that involve only the con-stituent elements [Lan81, Lan83]. Intrinsic defects can be mainly divided into three different types: vacancies (missing atoms at regular lattice positions), interstitials (extra atoms at in-terstices in the lattice), and antisites (a Zn atom occupying an O lattice site or vice versa in the ZnO structure) [Jan09a]. Assuming thermodynamic equilibrium and neglecting defect-

defect interaction, the concentration of an intrinsic defect in a solid, ,can be expressed by

its formation energy through the following equation [Kit05]:

′ = exp −

,(2.1)

where is the number of sites per unit volume the defect can be incorporated on, is the Boltzmann constant and the temperature. Equation (2.1) indicates that the concentra-tion of defects is lower with higher formation energies. The formation energy of a typical point defect depends on the growth environment or annealing conditions [Wal04]. The formation energy of an oxygen vacancy in ZnO is given by [Jan09a]:

= − ! +# + $% +&!,(2.2)

where is the total energy of a supercell containing the oxygen vacancy in the charge

state $, ! is the total energy of a ZnO perfect crystal in the same supercell, # is the oxygen chemical potential, % is the Fermi level and & is the valence-band maximum. Ex-pressions similar to equation (2.2) can be applied to all intrinsic point defects [Jan09a]. Defects are often electrically active and can create different levels in the semiconductor band gap, resulting in transitions between different charge states of the same defect [Lan81, Lan83]. The transition level '$ $⁄ ! is defined as the Fermi-level position for which the for-mation energies of charge states $ and $′ are equal [Jan07a]. The transition level indicates that for Fermi-level positions below '$ $⁄ ! charge state $ is stable, while for Fermi-level positions above '$ $⁄ ! charge state $′ is stable. The difference of a deep defect level and a shallow defect level lies in where the corresponding defect transition level is located. If a de-fect transition level is such positioned that it can be thermally ionized at room temperature or under device operation conditions, it is a shallow level. Otherwise it is a deep defect level. Considering the relative positioning of the transition levels to the band gaps in the semicon-ductor, the shallow levels can be defined in the following two scenarios: Firstly, the transition levels are close to the edge of the band gap (either to valence-band maximum (VBM) for an acceptor or to conduction-band minimum (CBM) for a donor); second, the transition levels function as resonance centers in either the conduction or valence band. In ZnO, the oxygen vacancy is the most discussed defect and since a long time, has been considered as the main cause of the unintentional n-type conductivity, but recent densi-

2.1 MATERIAL PROPERTIES OF ZNO 11

ty-functional calculations indicate ( to be a deep donor rather than a shallow donor and, therefore, it is not expected to contribute to the n-type conductivity [Jan05, Jan06, Jan07a]. Janotti et al. [Jan07a] have reported that although the oxygen vacancies have the lowest formation energies among all the intrinsic defects, the 3+2 + 0/⁄ transition level lies about 1 eV below the conduction-band minimum (CBM). As as-grown ZnO is unintentionally n-type and the Fermi level lies above the 3+2 + 0/⁄ transition level, therefore, the neutral charge state is stable for ( in n-type ZnO. It is clear that the oxygen vacancies do not satisfy the two scenarios discussed above for the shallow levels. On the contrary, the transition level 3+2 + 0/⁄ lies far away from the conduction-band minimum (CBM) and oxygen vacancies cannot provide electrons to the conduction band by thermal excitation in steady states. Besides the oxygen vacancies, the possibility of other intrinsic defects to act as shallow do-nors in n-type ZnO is analysed. Although zinc vacancies 7 have low formation energies [Jan07a] in n-type ZnO, they are very unlikely to be the cause for the n-type conductivity in the ZnO. 7 are deep acceptors with transition levels 3+0 −/ = 0.18;⁄ and 3+− 2−/ = 0.87;⁄ [Jan07a]. Unlike the deep acceptor levels of 7, the reason that a Zn interstitial atom (,- ) is unlikely to serve as shallow donor is its high formation energy [Jan09a]. Similar to ,-, the other intrinsic defects including zinc antisites, oxygen intersti-tials, and oxygen antisites have even higher formation energies and thus it is very unlikely that these intrinsic defects are the source of the intrinsic n-type conductivity in ZnO [Jan09a]. Since the intrinsic defects are not expected to cause the unintentional n-type conductivity in as-grown ZnO, it is important to investigate possible impurities which are commonly ob-served in ZnO and can eventually act as shallow donors. The characteristics of main dopant impurities are summarized in table 2.1. Table 2.1: Characteristics of major dopant impurities in ZnO. -=>? or @=>? indicate the high-est carrier concentration experimentally observed to date [Jan09a].

Impurity Character Ionization energy -=>? or @=>? ( ABC/ Al Donor 120 meV [Zha01] 8 ×10EF [Hu92a] Ga Donor − 1.1 × 10EF [Ko00]

− 3.7 × 10EF [Hu92b] In Donor − [Hu93] F Donor 80 meV [Zha01] 5 ×10EF [Hu91] H Donor 35 meV [Hof02] − Li Acceptor − Cu Acceptor − N Acceptor 100 meV [Loo02] 9 ×10J [Loo02]

From table 2.1, it can be seen that hydrogen has the lowest ionization energy which indicates that it needs the least energy to release the electron and make it a free electron. This makes hydrogen a good candidate for shallow donors. Moreover, hydrogen is a very reactive atom, occurring in virtually all organic and in many inorganic compounds [Cot99, Mor87]. Hydrogen can be easily incorporated into the material during processing steps such as wet etching or annealing in forming gas [Jan09a]. Therefore, hydrogen is considered to be one of the most dominant impurities in ZnO and the role of hydrogen in ZnO has been widely studied [Ban08,

12 CHAPTER 2: THEORY Wal00, Jan07b, Jan09a]. When incorporated in ZnO, hydrogen can either locate at intersti-tial sites Kor replace oxygen in ZnO which is defined as a substitutional hydrogen K(. What makes hydrogen unique in ZnO is that hydrogen does not show its amphoteric property which can be observed when hydrogen is present in almost all other semiconductors [Pan91, Wal98, Wal06]. Amphoteric property means that hydrogen counteracts the prevailing con-ductivity of the material. In p-type materials, hydrogen exists with the form of KL, and in n-type materials it incorporates as KB. Therefore, hydrogen is not expected to be the source of conductivity in almost all semiconductors due to its amphoteric property. In ZnO, however, K is only present in the positive charge state (KL ) because only the positive charge state is thermodynamically stable. Thus hydrogen can act as a donor [Jan09a]. Although interstitial hydrogen is expected to act as a donor in ZnO, Janotti and Van de Walle have found that during sputtering of ZnO, the observed dependence of conductivity on the oxygen partial pressure cannot be explained only by interstitial hydrogen [Jan07b]. In addi-tion to the interstitial positions, it has been recently found that hydrogen can also replace oxygen in ZnO (K(/ [Jan07b], which may explain the dependence of conductivity on oxygen partial pressure. When substitutional hydrogen (K() replaces oxygen, it is sensitive to the oxygen partial pressure in the growth or annealing environments. Increasing the oxygen par-tial pressure can decrease the K( concentration and hence lower the conductivity by several orders of magnitude. The substitutional hydrogen (K() forms a multicentre bond in which H is equally bonded to the four Zn nearest neighbors [Jan09a]. The concept of this multicentre bond can be easily explained by the classical three-center bonds in diborane MEK, where three atoms share two electrons [Lip63, Bar65]. Similar to the three-center bonds principle, hydrogen bonds equally to the four Zn nearest neighbors when substituting oxygen in ZnO. Figure 2.2 depicts the formation of hydrogen multicentre bond in ZnO. The four dangling bonds on the surrounding Zn atoms form a symmetric (J/ combination, which leads to a doubly occupied electronic state located in the bandgap of ZnO [Jan05]. If hydrogen is located at the center of the oxy-gen vacancy, the H 1N orbital strongly interacts with this symmetric combination to form a fully symmetric state in the valence band and an antibonding state in the conduction band [Jan07b]. There are three electrons available from the combination of substitutional hydrogen with the four Zn dangling bonds, within which one is from hydrogen and the other two are from the four Zn dangling bonds. Two of these three electrons occupy the low-energy fully symmetric orbital deep inside the valence band and stabilize the center; the third electron, which would occupy the next available orbital resonant in the conduction band, is weakly bonded and can be easily transferred to the conduction-band minimum and can contribute to the n-type conductivity in ZnO. Therefore, substitutional K( replacing at oxygen vacancies can act as a shallow donor in ZnO. The formation energy of K( can be calculated by [Jan07b]:

'K()* = 'K()* −+ℎPNQ/ −R + ( + 1 ,(2.3)

where 'K()* is the formation energy of substitutional hydrogen in the charge state 1 , 'K()* is the total energy of a supercell containing the substitutional hydrogen in the charge

2.1 MATERIAL PROPERTIES OF ZNO 13

state 1, +ℎPNQ/ is the total energy of a host ZnO perfect crystal in the same supercell, R is the hydrogen chemical potential. Varying oxygen partial pressure can change the oxygen chemical potential (, thus influencing the formation energy of K( and its concentration in ZnO. As K( is a shallow donor in ZnO, a change of K( concentration can influence the con-ductivity by several orders of magnitude [Jan07b].

Figure 2.2: Coupling between the H 1N orbital and the Zn 4N dangling bonds (Zn dbs) to form the hydrogen multicentre bond in ZnO. The H 1N orbital combines with the J state and re-sults in a fully symmetric bonding state in the valence band, and an antibonding state in the conduction band. The electron that would occupy this antibonding state is then transferred to the conduction-band minimum, making the substitutional hydrogen K( a shallow donor [Jan07b]. In summary, previous models on unintentional n-type doping in ZnO consider zinc interstitials and oxygen vacancies as the source of the n-type conductivity. Recent research groups ar-gue that rather than intrinsic defects in ZnO, the incorporated impurities, especially hydrogen, play an important role in n-type conductivity in ZnO. Both interstitial and substitutional hydro-gen can act as shallow donors in ZnO. The exploration of the source of the n-type conductivi-ty in ZnO and experimental methods for confirmation are still being pursued by research groups worldwide. In the next section, possible p-doping mechanisms are introduced and difficulties in realizing reliable and stable p-doping ZnO are also discussed.

2.1.3 P-doping in ZnO Besides the discussion of the source of intrinsic n-type ZnO, the introduction of shallow ac-ceptors is very important, especially when aiming at p-type doping effects. It is very difficult to obtain stable p-type doping in wide bandgap semiconductors, such as GaN and ZnO [Mor09]. The difficulties arise from a variety of reasons. One reason is that dopants may be

14 CHAPTER 2: THEORY compensated by intrinsic defects with low formation energies, such as Zn interstitials (,-) or oxygen vacancies () [Wal94], or incorporated hydrogen. Another problem in p-type doping is the low solubility of the dopant in the host material [Wal93]. Deep impurity levels can also be a source of the doping problem, making the formation of shallow acceptor levels more difficult [Özg05]. Group-IA elements such as Lithium (Li), Sodium (Na), Potassium (K) can act as possible acceptors by substituting Zn sites with very low ionization energies between 90 meV and 320 meV [Par02]. Look et al. [Loo04] have reported the compensation of p-type doping when these elements are located at interstitial positions. The p-doping by Li and Na has been re-ported experimentally by different groups. Zeng et al. [Zen06] have reported a hole concen-

tration of 1.44×1017 cm-3 and a hole mobility of about 2.65 cm2/Vs through doping of Li in

ZnO. A hole concentration of 4.7×1018 cm-3 and a hole mobility of 1.42 cm2/Vs by doping of Na in ZnO has been achieved by Lin et al. [Lin08]. Group-IB elements copper (Cu), silver (Ag), and gold (Au) can also replace Zn sites and act as acceptors. Although the ionization energies for group-IB elements are in the range of 400 meV and 700 meV, which is much higher than for the group-IA elements, the compensation effects are not expected for group-

IB elements [Yan06]. Kang et al. [Kan06] have reported a hole concentration of 6×1017 cm-3 and a hole mobility of about 2.4 cm2/Vs by doping of Ag. Group-V elements such as nitrogen (N), phosphorus (P), arsenic (As), antimony (Sb) can also act as acceptors when substituting on the oxygen lattice sites. Among the group-V ele-ments, nitrogen is considered to be the most suitable p-type dopant for several reasons [Jan09a]. Firstly, the nitrogen atom has the closest atomic size to oxygen, resulting in mini-mum strain in ZnO. Secondly, the energy of the valence 2p states and the electronegativity of nitrogen are also the closest to those of the oxygen atom. Lin et al. [Lin04] have reported a

hole concentration of 5×1017 cm-3 and a hole mobility of 2 cm2/Vs by incorporation of N into ZnO. However, the p-type conductivity in N-doped ZnO still remains controversial. For in-stance, Lyons et al. [Lyo09] have reported that nitrogen in ZnO has a high ionization energy of 1.3 eV, and therefore, it is actually a deep acceptor and unlikely to contribute to p-type conductivity in ZnO. Besides group-I and group-V elements, fluorine (F) can also act as a shallow acceptor when incorporated at interstitial sites. It is important to differentiate the roles of F as interstitial fluo-rine (T) and substitutional fluorine (T(/. Fluorine has one more electron than oxygen and, therefore, it is a shallow donor in ZnO when replacing at oxygen lattice sites. Different than T(, T strongly bonds to the ZnO atom and one electron from the VBM is transferred to its low-lying p states to complete its octet. The resulting hole can be thermally excited into the valence band when it is free to move under the influence of an electric field [Jan09b]. In sec-tion 4.4.2, the electrical characteristics of fluorine-implanted ZnO TFTs are discussed. Alt-hough p-type conductivity has not been realized by the applied doses and implantation ener-gies used in this work, it has the effect to modify the bulk charge concentration in ZnO and is useful to tune the threshold voltages of the ZnO TFTs.

2.2 THIN FILM TRANSISTORS 15

Another critical problem of realizing stable and reproducible p-type results is that the experi-mental methods for confirming the p-type conductivity in ZnO are still questionable. Hall-effect measurements are one of the most frequently used methods to detect charge carrier types, however, Hall-effect measurements for ZnO often tend to result in wrong interpreta-tions, sometimes even yielding the wrong carrier type [Ohg08, Bie08]. Ohgaki et al. [Ohg08] have reported that in Hall measurement, non-uniform electrical properties of the sample can lead to an incorrect determination of the carrier type. Additionally, it has been reported by Bierwagen et al. [Bie08] that inhomogeneities in carrier mobility do not affect the determina-tion of carrier type and concentration, as long as the carrier concentration remains homoge-neous. However, inhomogeneities in carrier concentrations can result in an incorrect deter-mination of the carrier type. In summary, there are many possibly suitable elements to serve as p-type dopants in ZnO. These possible candidates include interstitial fluorine, group-IA, group-IB, and group-V ele-ments. However, one critical problem regarding to p-doping in ZnO is the stability and relia-bility of the p-doping results. Hall-effect measurements often cannot make correct determina-tion of the charge carrier type and concentration mainly due to the nonuniformity and inho-mogeneities in the ZnO layer. The investigation of reliable p-doping experiments and detec-tion methods is of great importance. If reproducible and reliable p-type doping in ZnO can be achieved, which currently remains to be the main obstacle for realization of bipolar devices, it would dramatically extend the applications of ZnO for optoelectronic applications such as LEDs and lasers.

2.2 Thin film transistors ZnO-based devices can be classified into three main categories: passive linear devices such as resistors, capacitors, and inductors; two-terminal semiconductor devices such as p-n junc-tions, schottky barriers, heterojunctions, and MIS capacitors; three terminal devices such as TFTs [Wag08]. Passive two terminal devices are described by conventional Ohms law, charge-voltage (C-V) and current-voltage (I-V) relations. Among two terminal semiconductor devices, MIS capacitor is one important structure and understanding the working principle of MIS capacitor is the prerequisite of understanding the operations of TFTs. Below the different operation modes of classical silicon MIS capacitors are first introduced. For understanding of switch-on behavior in ZnO TFTs, it is important to compare a p-type silicon MIS capacitor under strong inversion and an n-type ZnO-based MIS capacitor under accumulation because under both conditions there is an electron channel in existance.

2.2.1 Comparison of Si MIS capacitors and ZnO MIS c apacitors In quantum mechanics, the allowed energy levels of electrons in a solid are grouped into bands separated by energy gaps [Sze07]. Energy gaps are defined as regions of energy the electron cannot occupy. In semiconductors, the valence band is the highest range of electron energies in which electrons are normally present at absolute zero temperature. The conduc-tion band is the next higher band which is separated from the valence band by a forbidden gap (the bandgap U). The bottom of the conduction band is labeled as V and the top of the

valence band as 2, which can be seen in Fig. 2.3. The energy distribution of electrons in a

16 CHAPTER 2: THEORY semiconductor is described by the Fermi-Dirac distribution function which gives the probabil-

ity of an energy level being occupied by an electron:

+/ = 11 + ;+BW//XYZ ,(2.4)

The Fermi energy level is the energy level at which the probability of occupation by an electron is 0.5. When electrons are excited from the valence band into the conduction band, holes are left in the valence band. Both electrons in the conduction band and holes in the valence band con-tribute to electrical conductivity. The conductivity is low as the density of these carriers is low in intrinsic silicon. Doping silicon with group-V elements introduces shallow donor energy states in the bandgap and silicon doped with group-V elements is defined as n-type silicon. Doping silicon with group-III elements introduces shallow acceptor energy states in the bandgap and silicon doped with group-III elements is defined as p-type silicon. The corre-sponding group-V and group-III elements are defined as n-type and p-type dopants, respec-tively. The n-type or p-type dopant gets ionized at room temperature, contributing extra elec-trons or holes to the conduction or valence band, respectively. Conduction is then dominated by the donated charge carriers from the dopant known as majority carriers [Fet11]. Majority charge carriers are electrons in n-type silicon and holes in p-type silicon. The introduction of the impurity also causes a corresponding shift in the Fermi level, which is shown in Fig. 2.3. The doping concentration [ for n-type doping and > for p-type doping determines the posi-tioning of the Fermi level . The Fermi level is equivalent to the semiconductor work func-tion ∅ and is given by:

= 1∅N = 1 ]χ + U21 + ψ$^ ,(2.5)

where 1 is the electronic charge and χ is the electron affinity for the semiconductor. The qua-si-Fermi potential ψ$ as shown in Fig. 2.3 is given by:

ψ$ = _ψ − ψ_ = #$%1 × ` - ]-[^ for n-type silicon and, (2.6)

ψ$ = _ψ − ψ_ = #$%1 × ` - ]>- ^ for p-type silicon. (2.7)

where ψ = −/1 is the Fermi potential and ψ = −/1 is the electrostatic potential

which is defined in terms of the intrinsic Fermi level. The metal-insulator-semiconductor (MIS) capacitor is the most fundamental structure in the study of semiconductor surfaces. Here, the metal-oxide-silicon (MOS) system is first intro-duced and then the ZnO-based MIS capacitor will be discussed and compared with the MOS system in detail. The band diagram of an ideal MOS system without voltage bias is shown in

2.2 THIN FILM TRANSISTORS 17

Fig. 2.4, for both n-type and p-type doped silicon. An ideal MOS system can be defined when the following conditions are fulfilled [Sze07]: (1) the only charges that exist in the structure under any biasing conditions are those in the semiconductor and those, with an equal but opposite sign, on the metal surface adjacent to the insulator, i.e., there is no interface trap nor any kind of oxide charge; (2) There is no carrier transport through the insulator under dc biasing conditions; (3) the charge transport takes place only by drift. Furthermore, for the sake of simplicity it is assumed that the work function difference between the chosen metal material and the silicon semiconductor is zero, i.e., ∅= = 0. The above conditions, with the help of Fig. 2.4, can be expressed by: ∅= =∅= − ∅ = ∅= − +χ+ ∅/ = 0for n-type silicon and, (2.8)

∅= =∅= − ∅ = ∅= − ]χ + U1 −∅a^ = 0for p-type silicon. (2.9)

where ∅= and ∅ are the work functions of metal and silicon, and ∅ and ∅a are the Fermi

potentials with respect to the band edges. When there is no applied voltage, the band is flat and it is defined as flat-band condition, as shown in Fig. 2.4.

Figure 2.3: Energy band diagram in intrinsic silicon and doped silicon.

18 CHAPTER 2: THEORY

Figure 2.4: Energy band diagram of ideal MOS system without voltage bias. (a) n-type doped silicon; (b) p-type doped silicon [Sze07]. When there is positive or negative voltage applied, the band starts to bend. Considering p-type silicon first, when a negative voltage ( < 0/ is applied to the metal, the valence band edge 2 bends upward near the surface and is closer to the Fermi level. As no current flows in the structure for an ideal MOS capacitor, the Fermi level remains flat in the semiconductor. Since the carrier density depends exponentially on the energy difference + − 2/ [Sze07], this bend bending causes an accumulation of majority carriers (holes in p-type silicon) at the surface of the silicon substrate. The device is said to be in accumulation (Fig 2.5(a)). If a small positive voltage + > 0/ is applied to the metal, the silicon bands bend downward at the silicon interface to the oxide, causing a reduction in the hole density at the silicon sur-face. The hole concentration at the silicon surface is reduced compared to the silicon bulk and the device is said to be in depletion (Fig. 2.5(b)). When a larger positive voltage is ap-plied to the metal, the silicon bands bend even more downward so that the intrinsic level at the surface crosses over the Fermi level . At this condition the minority carrier density (electron density) exceeds the majority carrier density (hole density) at the silicon surface. The surface is thus inverted and the device is said to be in inversion (Fig. 2.5(c)). So far we have discussed the band bending for accumulation, depletion, and inversion of silicon sur-face in a p-type MOS capacitor. Similar conditions hold true in an n-type MOS capacitor, ex-cept that the polarities of voltage, charge, and band bending are reversed, and the roles of electrons and holes are interchanged [Tau98].

2.2 THIN FILM TRANSISTORS 19

Figure 2.5: Energy-band diagram for ideal MOS capacitors with p-type silicon under different bias, for the conditions of: (a) accumulation, (b) depletion, and (c) inversion. A more detailed band diagram at the surface of a p-type silicon is shown in Fig. 2.6. The po-

tential ψ+d/ = ψ+d/ − ψ+d = ∞/ is defined as the amount of band bending at position d,

where d = 0 is at the silicon surface and ψ+d = ∞/ is the intrinsic potential in the bulk sili-

con. ψ+d/ is positive when the bands bend downward. The boundary conditions are ψ = 0 in the bulk silicon, and ψ = ψ+0/ = ψ at the surface, in which ψ is called the surface potential [Tau98]. In the silicon, the hole and electron concentrations @+d/ and -+d/are given by the following relationships [Tau98]:

@+d/ = - exp f1'ψ − ψ*#$% g = -exp f1'ψ$ − ψ*#$% g = >;d@ ]−1ψ#$%^ ,(2.10)

and

-+d/ = - exp f1'ψ − ψ*#$% g = - exp f1'ψ−ψ$*#$% g = -E> ;d@ ] 1ψ#$%^ (2.11)

where in the bulk silicon, @ = >, - = -E/>, > is the acceptor concentration in p-type

silicon and - is the intrinsic carrier concentration. At the surface the hole and electron con-centrations can be expressed by: @+0/ = >;d@ ]−1ψ#$% ^ ,(2.12)

-+0/ = -E> ;d@ ]1ψ#$%^ .(2.13)

20 CHAPTER 2: THEORY

Figure 2.6: Energy-band diagram near the silicon-insulator interface of a p-type MOS device.

The band bending ψ is defined as positive when the bands bend downward with respect to the bulk [Tau98]. Thus, the different operating conditions in an ideal p-type MOS capacitor can be related to

the surface potential ψ by the following relationships: ψ < 0h iAi`QjP-PℎP`;N+k-lNk;-lj-mi@nol/. ψ = 0T`Q − k-l P-ljQjP-. ψM > ψ > 0p;@`;QjP-PℎP`;N+k-lNk;-lj-mlPn-nol/. ψ = ψMT;oAj`;q;`QAjlm@. 2ψM > ψ > ψMr;#j-q;oNjP-. ψ > 2ψMQoP-mj-q;oNjP-.

In ideal MOS capacitors it is assumed that the metal work function ∅=is equivalent to the

silicon work function ∅. In general, however, the metal work function is not the same as the silicon work function and the silicon surface bends even at zero voltage applied to the metal due to a nonzero oxide field. In order to restore the flat-band condition, a voltage equal to the work function difference must be applied to the metal and this voltage is called the flat-band voltage $. The flat-band voltage is given by:

$ = ∅= − s(t(t = ∅= − ∅ − s(t(t ,(2.14)

where s(t is the equivalent oxide charge per unit area at the oxide-silicon interface and (t is the oxide capacitance per unit area. Unlike classical silicon-based MIS capacitors, the ZnO-based MIS capacitors have only two operation conditions: accumulation and depletion conditions. In semiconductor physics, car-

2.2 THIN FILM TRANSISTORS 21

rier lifetimes are important parameters and fall into two primary categories: recombination

lifetimes and generation lifetimes [Sch82]. The concept of recombination lifetime uv applies when excess carriers decay as a result of recombination. The three well known recombina-tion mechanisms are Shockley-Read-Hall or multiphonon recombination, radiative recombi-

nation and Auger recombination [Sch82]. The generation lifetime uU is the time that it takes

on average to generate an electron-hole pair. When generation events occur in the bulk, they

are characterized by uU and when they occur at the surface, they are characterized by the

surface generation velocity NU. The rate of minority carrier generation for bulk and surface

generation is given by [Sch06]: wx = -uU for bulk generation and, (2.15)

w = -NUfor surface generation. (2.16)

From the above relationships, it can be seen that the minority carrier generation rate de-pends on the intrinsic carrier concentration - in the layer. In silicon, the intrinsic carrier con-centration - at room temperature is 1.4 × 10JFcmBC [Tau98]. Similar to other semiconduc-tors, the intrinsic carrier concentration in ZnO is given by:

- = | exp ] −U2#$%^ , (2.17)

where | and are the effective densities of states in the conduction band and valence band, respectively. At room temperature, the band gap of ZnO has a value of 3.37 eV

[Man95] and the | and values are reported to be 3.0×1018cm-3 and 1.8 × 10JcmBC , respectively [Wag08]. Inserting these values into Eq. (2.17), the calculated intrinsic carrier

concentration in ZnO - is about 10BJF ABC . Comparing to silicon, the minority carrier (holes) generation rate in ZnO is expected to be about 20 orders of magnitude less than that in silicon. This is the main reason why the inversion condition in classical silicon MIS capaci-tors is not relevant in ZnO-based MIS capacitors. Moreover, as a wide band gap semicon-ductor, ZnO requires about 2.5-3 V of surface potential modulation from flat-band condition to inversion condition compared to about 0.7-1 V for silicon [Wag08]. Additionally, surface po-tential modulation in ZnO requires the depletion of filled deep level traps and band tail states prior to reaching the inversion condition. For all these reasons, inversion does not occur in ZnO-based MIS capacitors.

22 CHAPTER 2: THEORY

Figure 2.7: Energy-band diagram and charge distribution for a p-type silicon MIS capacitor under strong inversion (a) and a ZnO-based MIS capacitor under accumulation (b). Figure 2.7 shows the comparison of a p-type silicon MIS capacitor under strong inversion and a ZnO-based MIS capacitor under accumulation. The charge distributions in both cases are also shown schematically in Fig. 2.7. For simplicity of discussion, oxide and interface trapped charges are ignored here. For charge neutrality of the system, it is required that s = −s = −'s + sa* = −+s + 1>r/for p-type silicon MIS capacitor, (2.18)

s = −s = −sfor ZnO-based MIS capacitor, (2.19)

where s is the charge per unit area on the metal side, s is the total charge per unit area in

the semiconductor, s is the electron charge per unit area near the semiconductor surface,

and sa is the charge of ionized acceptors per unit area in the space charge region with de-

pletion width r. In the p-type silicon MIS capacitor, when the applied positive voltage on

the metal is large enough so that the surface potential ψ is larger than 2ψ$, strong inver-

sion takes place and a n-channel inversion layer is built up for channel conduction in p-type silicon. In the ZnO-based MIS capacitor, however, when there is a positive gate voltage ap-plied, the majority carriers (electrons) are attracted to the area near the ZnO surface and an accumulation layer is built up for channel conduction. As ZnO is intrinsically n-doped, no space charge region is available in the semiconductor layer for positive gate voltages. When negative gate voltage is applied, a depletion layer can form in the semiconductor layer.

2.2 THIN FILM TRANSISTORS 23

2.2.2 Comparison of Si MOSFETs and ZnO thin film tr ansistors 2.2.2.1 MOSFETs theory In the last section, the basic structure and the working principles of silicon MOS capacitor is introduced. Compared to the MOS capacitor, the MOSFET consists of two additional termi-nals, source and drain. Source and drain are highly doped regions that are separated by the body region. In the case of a NMOS transistor, the silicon substrate is p-type doped and source and drain regions are highly n-doped, which is signified by a ‘+’ sign after the type of the doping shown in Fig. 2.8. The highly doped source and drain regions can be fabricated by ion implantation or diffusion. A fourth terminal can be connected to the substrate which is defined as the substrate bias $. When a reverse substrate bias −$ is applied to the sili-con bulk, it has the equivalent effect of raising all other voltages (gate, source and drain volt-ages) by +$ while keeping the substrate grounded. The effect of reverse substrate bias is to widen the bulk depletion region and thus raise the threshold voltage [Tau98]. The changes in the threshold voltage by the change in the substrate bias is said to be the body effect. Figure 2.8 schematically shows the structural differences between a planar Si NMOS transis-tor and the ZnO TFT under investigation in this work. In a NMOS transistor the semiconduc-tor material is the bulk silicon, however, in a ZnO TFT a thin ZnO layer is deposited onto a supporting substrate as the semiconductor active layer. Glasses and silicon wafers can be chosen as a supporting substrate. Figure 2.8(b) depicts the bottom gate top contact configu-ration of a ZnO TFT. Firstly, a dielectric layer is deposited on top of the highly doped silicon wafer functioning as the bottom gate. Then, ZnO layer is deposited on the gate oxide by us-ing chemical vapor deposition or physical vapor deposition (usually sputtering). Finally, me-tallic contacts are deposited onto the ZnO active layer as source and drain contacts. Unlike silicon MOSFETs, the source and drain contacts in TFTs do not need to be doped with an opposite type to the body region and different materials such as aluminum and indium tin oxide (ITO) are good candidates for source and drain formation. By using glass as substrate and transparent electrodes such as ITO, TFT devices can be made completely transparent. This makes ZnO TFTs very attractive in liquid crystal display (LCD) applications. Because the glass substrate cannot withstand high annealing temperature, deposition processes with relatively low processing temperature are therefore preferred. Physical vapor deposition such as sputtering is an ideal technique to fabricate ZnO active layers with low processing tem-perature and will be discussed in detail in the following section 2.3.

24 CHAPTER 2: THEORY

Figure 2.8: Schematic of a NMOS transistor (a) and a bottom gate ZnO TFT (b). In an NMOS transistor, if it is assumed that the gradual channel approximation (GCA) vali-dates, which assumes that the variation of the electric field in the -direction (along the channel) is much less than the corresponding variation in the d-direction (perpendicular to

the channel), the current density flowing from source to drain in an NMOS transistor is given by [Tau98]:

+d, / = −1--+d, / l+/l , (2.20)

where is the electron mobility in the channel and -+d, / is the electron density. According to current continuity along the channel, which requires that the drain current is identical at any point along the channel (-direction), the drain current should be a constant, thus in-

dependent of . Therefore, the drain current is given by integrating the current density in Eq. (2.20):

= r −s+/2F l, (2.21)

where s+/ is the inversion charge per unit gate area:

s+/ = −1 -+d, /ld?F , (2.22)

and depends on the potential along the transistor channel in the y-direction and is the

effective charge mobility [Tau98]. By using the charge-sheet approximation [Bre78] which assumes that the inversion layer is a charge sheet with infinitesimal thickness and no poten-tial drop or band bending occurs across the inversion layer, the inversion charge density in Eq. (2.22) is given by:

2.2 THIN FILM TRANSISTORS 25

s = s − s[ = −(t' − $ − 2ψM − * +23Nj1'2ψM + *.(2.23)

where s and s[ are surface charge density and depletion charge density, and 3 is the silicon permittivity. Substituting Eq. (2.23) into Eq. (2.21) and carrying out the integration, the drain current is given by [Tau98]:

= (tr ] − $ − 2ψ$ − 2 ^ − 223Nj1>3(t '2ψ$ + *C/E − '2ψ$*C/E . (2.24)

Equation (2.24) indicates that the drain current depends on the gate voltage and the

drain voltage . Under a fixed gate voltage , the drain current first increases linearly

with the drain voltage (defined as the linear or triode region), then becomes saturated at a certain current level (defined as saturation region). Figure 2.9 shows these regions in an output characteristic curve of a NMOS transistor. These three distinct operating regions are further discussed in detail below.

Figure 2.9: Schematic of output characteristics of an NMOS transistor including the three main operating regions.

When is well below − , is given by [Tau98]:

= ;.r +w − Qℎ/p,(2.25)

26 CHAPTER 2: THEORY where is the threshold voltage given by = $ + ψ + (t

= TM + 2ψ$ +431>ψ$. . (2.26)

The threshold voltage consists of three parts: the flat-band voltage $, the voltage drop in the substrate equating the surface potential ψ and the potential drop on the oxide (t.

Recalling that when ψ > 2ψM, strong inversion happens, is the gate voltage when the

surface potential or band bending reaches 2ψ$ and an inversion layer forms at the interface

between the gate oxide and the silicon substrate of the transistor. When < , there is very little current flow and the transistor operates in the subthreshold region. When > ,

the transistor is turned on. If is much smaller than the difference between the gate volt-age and the threshold voltage, a homogenous channel forms at the interface between the semiconductor and the gate oxide. The transistor acts like a resistor with a sheet resistivity , which is given by:

= 1;.+w −Qℎ/ ,(2.27)

and is modulated by the gate voltage. The drain current is described by Eq. (2.25) and the device is said to be in the linear region. For larger values of , the channel resistance be-gins to increase and the relationship between drain current and drain voltage is not linear any more. When the potential difference between gate and drain becomes smaller due to in-creasing , the number of electrons at the drain end becomes smaller. In this region, the drain current follows a parabolic curve until the saturation level is reached. The transistor is

said to be in the triode region. The drain current in the triode region is given by:

= ;.r !w −Qℎ −p2 &p.(2.28)

When the drain voltage increases to a value that exceeds the difference between the gate voltage and the threshold voltage, there are only few electrons at the drain end and a space charge region extends from drain towards source at the interface between semicon-ductor and insulator. This condition is defined as pinch-off. If increases further, the pinch-off point of the channel begins to move away from the drain towards the source. The poten-tial at the pinch-off point remains unchanged and the number of electrons from the source to the pinch-off point remains unchanged. The transistor is now said to be in the saturation re-

gion. The drain current in the saturation region is given by:

= 12(tr + − /E.(2.29)

2.2 THIN FILM TRANSISTORS 27

From Eq. (2.29), the drain current in the saturation region under a fixed gate voltage stays constant, independent of the drain voltage . The channel formation under different operat-ing regions is shown in Fig. 2.10.

Figure 2.10: Channel formation in an NMOS transistor under different operating conditions (a) turn-off region, (b) linear region, (c) triode region and (d) saturation region.

2.2.2.2 Junction FET theory Compared to the MOSFET, the junction field-effect transistor (JFET) has the advantage of avoiding problems related to the oxide-semiconductor interface such as interface traps and reliability issues arising from hot-electron injection and trapping [Sze07]. A typical JFET con-sists of a conductive channel in which a p-n junction is operated under reverse bias condi-tion. For a n-channel JFET, the channel is n-doped and the p+ well is formed by diffusion or implantation. Figure 2.11 shows the typical structure of an n-channel JFET under different operating regimes. Besides the n-channel and the p-n junction, the JFET consists of three contacts. Two contacts are interchangeable and act as source and drain. The third electrode, the gate, forms a rectifying junction and controls the width of the conductive channel by vary-ing the depletion width. The JFET can only operate in depletion condition, as the p-n junction can only operate under reverse bias in order to avoid high gate current.

When drain voltage is small, the depletion region width r remains practically inde-

pendent of and the channel acts as a resistor (shown in Fig. 2.11 (a)). The depletion lay-

er width at any distance d from the source is given by [Sze07]:

r+d/ = 23ψx + ∆ψ+d/ − 1[ , (2.30)

28 CHAPTER 2: THEORY where ψx is the built-in potential of the p+-n junction in JFET and ∆ψ+d/ is the potential of

the channel with respect to the source (at the source end, d =0).

Figure 2.11: Schematic diagram of JFET structure under different operating regimes: (a) lin-ear region, (b) triode region, (c) saturation region, (d) pinch-off region [Wal11].

When is small, the portion of ∆ψ+d/ in Eq. 2.30 can be neglected and the depletion lay-

er width is expressed as

r = 23'ψx − *1[ . (2.31)

The drain current under this condition can be calculated by:

= rQVR = r+QVR −r/ , (2.32)

where is the electrical conductivity, QVR and QVR are the channel thickness and the net

channel opening, respectively. By substituting rfrom Eq. 2.31 into Eq. 2.32, is given by:

= r QVR −23'ψx − *1[ . (2.33)

From Eq. (2.33) it is seen that for a constant applied gate voltage, the drain current increases linearly with the drain voltage. The channel has a constant resistance and this operating

condition is defined as the linear region of a JFET. However, as increases further, the potential drop across the channel cannot be neglected and the depletion layer width is now dependent on the applied drain voltage. The net channel opening for current flow is reduced because of the increasing reverse bias of the gate junction near the drain area (shown in Fig.

2.2 THIN FILM TRANSISTORS 29

2.11 (b)). Thus, the channel resistance will also increase and the current-voltage characteris-tics will enter the triode region. In the triode region, the drain current is calculated by:

= r QVR −23'ψx + ∆ψ+d/ − *1[ 2F

l∆ψ.(2.34)

By integrating the potential difference from source end to drain end, is given by:

= rQVR − 23ψ 'ψx + − *C/E − 'ψx − *C/E , (2.35)

where ψ is defined as the pinch-off voltage [Sze07]. When the gate voltage satisfies the

following conditions: = ψx − ψ, (2.36)

the channel is fully depleted and the drain current is equal to zero (shown in Fig. 2.11 (d)).