1Ausgewählte Themen des analogen Schaltungsentwurfs Ivan Peric [email protected] .

-

Upload

parzival-lech -

Category

Documents

-

view

109 -

download

3

Transcript of 1Ausgewählte Themen des analogen Schaltungsentwurfs Ivan Peric [email protected] .

2 Ausgewählte Themen des analogen Schaltungsentwurfs

CMOS Technologie MOS Transistor Verstärker Rückkopplung AC Analyse Verstärkervarianten Getaktete Verstärker (switched Caapcitor Circuits) ADCs Filter Komparatore

3 Ausgewählte Themen des analogen Schaltungsentwurfs

Analoge Elektronik - Aufgaben

Design von Sensoren Verstärkern und Filtern ADCs Logikzellen Empfänger, Sender Speicher

Filter ADC

001010100

Verstärker

DSP

S E

L

01011

Sensor

4 Ausgewählte Themen des analogen Schaltungsentwurfs

AE (4) Digitales Design: Kompromiss zwischen Geschwindigkeit und Leistungsverbrauch Analoges Design: Kompromiss zwischen Geschwindigkeit, Leistungsverbrauch, Genauigkeit

(z.B. Linearität, Verstärkung), Versorgungsspannung… Analoge Schaltungen sind viel empfindlicher gegenüber Übersprechen und Rauschen Analogdesign kann nur schwer automatisiert werden

Unterschiedliche Ebenen von Abstraktion

B

A

G

D S

Transistor

PMOS

Verstärker System

5 Ausgewählte Themen des analogen Schaltungsentwurfs

Silizium (15% der Erde) SiO2 – einer der besten bekannter Isolatoren

- (GaAs ICs benutzen Si3N4 oder reines GaAs als Isolator) (GaAs – bessere Mobilität, Rauschen, Lichtdioden…)

1022 Atomen - 1010

freie Elektronen – 1016 Dotierungsatomen in cm3 Si Reines Material wird benutzt (1/106) 1) Chemische Medoden: Rohsilizium –> HSiCl3 (Trichlorsilan) -> Destillierung -> T ->

Si -> (Polykristall - Solarsilizium) Si (Siemens Prozess) 2) Poly Si wird geschmolzen + P-Dotierung. Impfkristall wird in die Schmelze gebracht und unter Drehen hinausgezogen ->

Verunreinigungen bleiben in der Schmelze (Stoffe neigen möglichst rein zu kristallisieren) -> Si Kristall (Halbleitersilizium) -> Wafers werden gesägt (Czochralski Prozess)

Technologie

HCl

HSiCl3Rohsilizium

Solar SiReines Halbleitersilizium1)

2)

3)

6 Ausgewählte Themen des analogen Schaltungsentwurfs

Technologie

Front-End Prozesse – Erzeugung von TransistorenDeponierung von Dotierungssubstanzen, Oxidation, Isolierung von Transistoren

Back-End Prozesse – Erzeugung von Metalllagen (Al, Cu), Isolatorlagen (SiO2, Glas), „Via“ Löcher (Wolfram).

PhotolithographieSchritte:Polymer Photolack wird aufgebrachtStepper wird benutzt: „Reticle“-Dia mit 5X Verkleinerung mittels UV Licht (200 nm)

wird projiziert.Photolack wird belichtet, belichtete Stellen härtenNaOH wird benutzt, Photolack durch Ätzung entfernt

Elektronenstrahllithographie

7 Ausgewählte Themen des analogen Schaltungsentwurfs

Wafer

Epi Lage

SiO2

Si2N3

Photolack

Implantation von Diffusionswannen

Wafer

Epi Lage

Wafer

Epi Lage

SiO2

Wafer

Epi Lage

SiO2

Si2N3

UV Licht

Ätzen

Ionenimplantation

8 Ausgewählte Themen des analogen Schaltungsentwurfs

Technologie – Implantation von Diffusionswannen

Standard N-Well Prozess mit epi-Lage Wafer (Monokristall) Schritt 1 Epi Lage – ein epitaktisch gewachsene Si Schicht (Monokristall) Schritt 2 Schwachdotierte N- und P-Wannen für P und N-Kanal Transistoren werden

erzeugt

- Maske ist SiO2 Oxidation Nitrid wird aufgebracht Photolack Ätzung

Ionen (P) werden mit 80KV beschleunigt, Ionenimplantation, Dotierung…

9 Ausgewählte Themen des analogen Schaltungsentwurfs

Feldoxid

SiO2

Si2N3

Wafer

Epi Lage

SiO2

Si2N3

Lack

Ätzen

H2O

Oxidation

SiO2 SiO2

Anisotropische Ätzung u. Polieren

10 Ausgewählte Themen des analogen Schaltungsentwurfs

Feldoxid

Dickes Oxid (Feldoxid) – Isolierung zwischen TransistorenMaske: SiO2 + Silizium-Nitrid

„LOCOS“: Lokale „feuchte“ Oxidation: Si + 2H2O - > SiO2 + 2H2 (Oberfläche nicht eben)

„STI“: Plasma Ätzung – Trench – CVD (Chemical Vapour Deposition) Oxid (benutzt Gas Si(OC2H5)4 ) – Polieren (CMP – Chemical Mechanical Polishing) – ebene Oberfläche – erlaubt mehr Metalllagen.

11 Ausgewählte Themen des analogen Schaltungsentwurfs

Feldoxid

Dickes Oxid (Feldoxid) – Isolierung zwischen TransistorenMaske: SiO2 + Silizium-Nitrid

„LOCOS“: Lokale „feuchte“ Oxidation: Si + 2H2O - > SiO2 + 2H2 (Oberfläche nicht eben)

„STI“: Plasma Ätzung – Trench – CVD (Chemical Vapour Deposition) Oxid (benutzt Gas Si(OC2H5)4 ) – Polieren (CMP – Chemical Mechanical Polishing) – ebene Oberfläche – erlaubt mehr Metalllagen.

12 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Oxid

Epi Lage

Oxidation

800° C 02

13 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Oxid

Transistoren (aktive Bereiche) und ohmsche Kontakte sind jetzt isoliert. Der kritischste Schritt – Erzeugung vom Gate – Oxid Trockene thermische Oxidierung (in Sauerstoff Atmosphäre) 100 min @ 800°C.

(Si + O2 -> SiO2) – 7nm Oxid

14 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Oxid

Transistoren (aktive Bereiche) und ohmsche Kontakte sind jetzt isoliert. Der kritischste Schritt – Erzeugung vom Gate – Oxid Trockene thermische Oxidierung (in Sauerstoff Atmosphäre) 100 min @ 800°C.

(Si + O2 -> SiO2) – 7nm Oxid

15 Ausgewählte Themen des analogen Schaltungsentwurfs

Transistor

SiH4

Chemische Abscheidung

Poly-Silizium

Photolack

Oxidation

Ionenimplantation

P+ P+

Poly Si

thermische Ausheilung

16 Ausgewählte Themen des analogen Schaltungsentwurfs

Transistor

Ganzflächige Abscheidung von Polysilizium – (CVD) (Silan – SiH4). Photolack + Polysilizium wird abgeätzt – Gate Elektroden. Maske deckt die aktive Bereiche ab. Rundumisolierung von Gate Elektroden „spacer“ definiert schwach dotierte

Source und Drain As (Arsen) und P (Phosphor) Ionen – n+ Drain, Source, ohmsche Kontakte –

Polysilizium Gates dienen als Masken – Prozess ist selbstjustierend (self-aligment)

B (Bor) Ionen – p+ Drain, Source, ohmsche Kontakte Thermische Ausheilung – Diffusion von Ionen.

17 Ausgewählte Themen des analogen Schaltungsentwurfs

Metallisierung (selbstjustierendes Silizid)

Poly Si

Anisotropische Ätzung

Aufbringen gasförmigen Titans

Silizierung(TiSi2)Ätzung

18 Ausgewählte Themen des analogen Schaltungsentwurfs

Transistor

Ti wird angebracht – TiSi2 bildet sich am Silizium – SiO2 Oberfläche reagiert nicht – Ti wird abgeätzt – (self aligned silicide)

19 Ausgewählte Themen des analogen Schaltungsentwurfs

Metallisierung

Poly Si

Aufbringen von SiO2 und Bor-Phosphor-Silikat-Glas

Aufbringen von Wolfram

Sputtern von Al oder CuStrukturierungAufbringen vom Dielektrikum

20 Ausgewählte Themen des analogen Schaltungsentwurfs

Metallisierung

SiO2 und Phosphorglas werden angebracht 1) „Via“ Öffnungen werden gemacht 2) und mit Titan und Wolfram aufgefüllt 3) Polieren 4) Aufbringen von Dielektrikum 5) Sputtern von Al oder Cu 6) Metall wird strukturiert 7) Polieren … Passivierung Die letzte Maske – Öffnungen in Passivierung

21 Ausgewählte Themen des analogen Schaltungsentwurfs

Metallisierung

SiO2 und Phosphorglas werden angebracht 1) „Via“ Öffnungen werden gemacht 2) und mit Titan und Wolfram aufgefüllt 3) Polieren 4) Aufbringen von Dielektrikum 5) Sputtern von Al oder Cu 6) Metall wird strukturiert 7) Polieren … Passivierung Die letzte Maske – Öffnungen in Passivierung

MOS Transistor

23 Ausgewählte Themen des analogen Schaltungsentwurfs

MOS Transistor

N N

pn

verarmt

Leitungsband

Valenzband

Löcher

Elektronen

Gate

Source Drain

24 Ausgewählte Themen des analogen Schaltungsentwurfs

Leitungsband

Valenzband

Elektronen Löcher

Valenzelektronen + Donator-IoneValenzelektronen + Anzeptor-Ione

N Silizium P Silizium

25 Ausgewählte Themen des analogen Schaltungsentwurfs

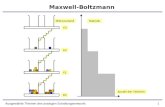

kT

E

kT

EEefe

enen

0

1

1

kT

EE f

e

n

kT

E

kT

EEhef

epen

01

ΔEe

ΔEh

26 Ausgewählte Themen des analogen Schaltungsentwurfs

MOS Transistor

N N

pn

verarmt

Leitungsband

Valenzband

Löcher

Elektronen

Gate

Source Drain

27 Ausgewählte Themen des analogen Schaltungsentwurfs

MOS Transistor – Gate Spannung

pn

Leitungsband

Valenzband

Elektronen

N NN N- q

q

28 Ausgewählte Themen des analogen Schaltungsentwurfs

MOS Transistor

pn

Leitungsband

Valenzband

Elektronen

N NN N- q

q

29 Ausgewählte Themen des analogen Schaltungsentwurfs

MOS Transistor - Inversion

pn

Leitungsband

Valenzband

Elektronen

N NN N- q0

q0

0 ψ0 ~ 0.85 V

n

ψ

ψ0

30 Ausgewählte Themen des analogen Schaltungsentwurfs

MOS Transistor

pn

Leitungsband

Valenzband

Elektronen

N NN N- q0

q0

0 ψ0 ~ 0.85 V

n

ψ

ψ0

31 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Spannung - Kanal

N NN Nψ0

VG=VT0+ΔV

- Δq

- q0

q0+ΔqVG=VT0+ΔV

pn

Leitungsband

Valenzband

Elektronen

32 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Spannung - Kanalladung

N NN Nψ0

VG=VT0+ΔV

- Δq

- q0

q0+ΔqVG=VT0+ΔV

pn

Leitungsband

Valenzband)( 0

'TGox VVCQ

Q‘ ( q/cm2)

Ladung pro Fläche

Oxydkapazität pro Fläche

33 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Spannung – Drain/Source Bias

N NN NΨ0+VS

)('STGox VVVCQ

Q‘ ( q/cm2)

Ladung pro Fläche

Oxydkapazität pro Fläche

- Δq

- q0

q0+ΔqVs Vs

VG=VT0+ΔV

VG=VT0+ΔV

Vs

pn

Leitungsband

Valenzband

)('TGSox VVCQ

34 Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Spannung – Drain/Source Bias

N NN NΨ0+VS

)(0 STGox VVVC

Q‘ ( q/cm2)

Ladung pro Fläche

Oxydkapazität pro Fläche

0

- q0

q0+0VDS ΔV

VG=VT0+ΔV

VG=VT0+ΔV

ΔV

VT

pn

Leitungsband

Valenzband

TGS VV

35 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Strom

N NN N

VGS Vds

Vds sehr klein

36 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Strom

N NN N

Vds

dsTGSoxnds

nn VVVCL

W

L

VWQESqI )('

Querschnitt

LadungsdichteMobilität

E-Feld

Breite/Lange des Gates

VGS Vds sehr klein

37 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Strom

N NN N

VdsVGS Vds sehr klein

38 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Strom

N NN N

Vds

eVds

Vds

I

dsTGSoxn VVVCL

WI )(~

VGS

dsn VQL

WI '~

39 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Stromsättigung

N NN N

Vds

eVDB

VdsVdssat=Vgs-VT

Ilim

IsatI

2lim )( TGSoxn VVC

L

WI

2)(2

1TGSoxnsat VVC

L

WI

VT

Pinch off

VGS TGD VV

TGSDS VVV

40 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Stromsättigung

N NN N

Vds

I

Vds

VGS

41 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Stromsättigung

N NN N

Vds

I

Vds

VGS

42 Ausgewählte Themen des analogen Schaltungsentwurfs

Drain Spannung - Stromsättigung

N NN N

Vds

I

Vds

VGS

43 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromsättigung

N NN N

Vds

I

Vds

VGS

44 Ausgewählte Themen des analogen Schaltungsentwurfs

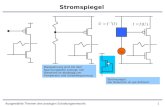

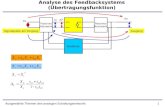

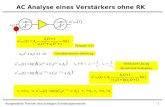

Analyse des Feedbacksystems (Übertragungsfunktion)

PassivesNetzwerk

PassivesNetzwerk

Feedback

Xs Xi Xi* Xo

osi XtXtX 2221

*1211 iso XtXtX

*ii XX

2212

211211

1 tt

ttt

X

XA

s

oF

Signalquelle am Eingang Ausgang

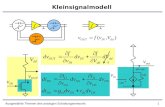

Kleinsignalmodell

46 Ausgewählte Themen des analogen Schaltungsentwurfs

Kleinsignalmodell

),( ddINOUT Vvfv

dddd

ININ

OUT dVV

fdv

v

fdv

gmvgs

rds

vgs

OUTvINv

ddV

inv

outv

DSDS

DGS

GS

DDS dv

v

idv

v

idi

DSdsGSmDS dvrdvgdi

0

+-