Eingebettete Systeme (VAK 18.142) · bestimmter Weise beeinflusst werden soll(en); beispielsweise...

Transcript of Eingebettete Systeme (VAK 18.142) · bestimmter Weise beeinflusst werden soll(en); beispielsweise...

Eingebettete Systeme (VAK 18.142)

Prof. Dr.-Ing. D.P.F. MöllerSS 2005

Tech

nisc

he

Syste

me

Syste

me

Info

rmat

ik

Leitung: Prof. Dr.-Ing. D.P.F. Möller

Embedded Systems (EBS)3. Embedded Control3.1 Grundlagen der Regelungstechnik 3.2 Strukturkonzept eingebetteter Regelungen3.3 Mathematische Methoden für die Entwicklung eingebetteter

Regelungssysteme 3.4 Componentware3.4.1 µC-Kern3.4.2 Embedded Fuzzy Controller3.4.2.1 Fuzzy Set Theorie3.4.2.2 Componentware für Fuzzy Control Entwurf3.4.2.3 Auswahl der Zielplattform3.4.2.4 Entwurfsmethodik3.4.2.5 Fuzzyfizierung3.4.2.6 Aggregation3.4.2.7 Inferenz3.4.2.8 Akkumulation3.4.2.9 Defuzzyfizierung

Embedded Systems (EBS)3. Embedded Control3.4.2.10 Modellentwurf3.4.2.11 Entwurf3.4.2.12 Regelbasis3.4.2.13 Fuzzy Sets3.4.2.14 Speicherschnittstelle3.4.2.15 Registerbank3.4.2.16 Kommunikationssteuerung3.4.2.17 Fuzzy Embedded Control Architecture3.5 Open-Loop and Closed Loop Embedded Control Systems

3.1 Grundlagen der Regelungstechnik

SteuerungDie Ausgangsgröße der Steuerung ist in ihrem Wert aufgrund der einseitig erreichten Wirkung in der Anordnung nicht allein von der

Führungsgrößesondern vielmehr auch von von den

Störgrößenabhängig.Steuerung besteht aus einer Anzahl Übertragungsgliedern die alle hintereinander als Kette geschaltet sind

Stellgröße→Stellglied→gesteuerte Objekt→Ausgangsgröße→← Strecke →

3.1 Grundlagen der Regelungstechnik

Steuerung

Wirken in ein abgegrenztes System mit äußeren Eingriffen – der Ein-gangs- oder Führungsgröße – diese so ein, dass für die Ausgangs-oder Eingangsgrößen gemäß vorgegebener physikalischer Gesetzmäßig-keiten, Verknüpfungen und Zeitabläufe ein gewünschter Wert zuerwarten ist, spricht man von einer Steuerung.

Die Ausgangsgröße nimmt dabei keinen Einfluss auf die EingangsgrößeWeshalb die Ausgangsgröße infolge äußerer Störungen beträchtlich vomgewünschten Wert abweichen kann.

3.1 Grundlagen der Regelungstechnik

Regelung

Treten in einem System Änderungen von Störgrößen zu beliebiger Zeitund in beliebiger Amplitude bis zum Grenzwert auf, ist es besser, dieAufgabengrößen zu erfassen und bei Abweichungen von der erwartetenRelation zur Stellgröße diese Eingangsgröße der Strecke zu verändern.Auf diese Weise kann man nicht vorhersehbaren Störungen entgegen wirken. Das geschilderte Verfahren wird Regelung genannt. Hierfür ist eine Regeleinrichtung erforderlich, die im einfachsten Fall aus einer Einrichtung zur Erfassung der Regelgröße, zum Vergleichen mit der Führungsgröße und zum Bilden der Stellgröße besteht.

3.1 Grundlagen der Regelungstechnik

Regelung

Der Vergleich zwischen Führungsgröße und Regelgröße ist erforderlich um festzustellen, wie weit sich die Regelgröße von dem vorgegebenen Wert entfernt hat. Die Differenz zwischen Führungsgröße und Regel-größe ist die Regeldifferenz. Die Regeleinrichtung soll die Regeldifferenz jederzeit so klein wie irgend möglich halten..

3.1 Grundlagen der Regelungstechnik

Regelungregelt mittels Regelkreis Störgröße aus bzw. Führungsgröße ein. Ausgangspunkt ist ein System in dem zeitveränderliche Größe(n) in bestimmter Weise beeinflusst werden soll(en); beispielsweise auf einenkonstanten Wert gebracht und dort gehalten soll (en).

• zu beeinflussende Größe heißt Regelgröße x, • das gegebene System ist die Regelstrecke, • die Regelgröße ist die Ausgangsgröße der Strecke.

In die Strecke greifen Störgrößen z(t) ein um die Regelgröße xs(t) zu beeinflussen.

3.1 Grundlagen der Regelungstechnik

RegelungUm die Regelgröße auf gewünschten Zeitverlauf zu bringen und dort zu halten wird sie durch eine Messeinrichtung erfasst. Erfasste Regelgröße xR wird mit dem gewünschten Sollverlauf Kxs verglichen. Dieser wird als zusätzliche Größe, die Führungsgröße w eingespeist. Der Vergleich erfolgt durch Differenzbildung:

xd = w – xR.

Ihr Ergebnis ist die Regeldifferenz xd.

3.1 Grundlagen der Regelungstechnik

RegelungMan spricht von Soll-Ist-Vergleich, da der Sollwert w = Kxs der Regel-größe mit ihrem Istwert xR = Kx verglichen wird. Ist die Regeldifferenz

xd = w – xR = Kxs – Kx = K(xs – x)

identisch Null, ist die Regelgröße x(t) identisch mit ihrem Sollwertverlaufxs(t). Ist die Regeldifferenz von Null verschieden, wirkt sie auf die Regel-strecke ein.

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Beschreibung des dynamischen Verhaltens eingebetteter Systeme durch das Strukturbild und durch Übertragungsglieder• Proportionalglied• Integrierglied• Differenzierglied• Totzeitglied• Kennlinienglied• Multiplikatives Glied• Verzögerungsglied 1. und 2. Ordnung• Vorhaltglied

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

.oi qqdtdV

−=

).()( tHAtV ⋅=

dtdHA

dtdV

⋅=

.oi qqdtdHA

dtdV

−=⋅=

)(1 tHR

qo ⋅=

)(1 tHR

qdtdHA

dtdV

i ⋅−⋅=

)(11 tHAR

qAdt

dHi ⋅

⋅−⋅=

)(1)( tHR

ty ⋅=

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Regler Componentware, welche Differenz zwischen Führungsgröße und Regel-größe feststellt und daraus Stellgröße bildet und ausregelt, d.h. zu Nullmacht.Beispiel:Geschlossener Regelkreis abhängig von Führungsgröße. Daraus ergibtsich für Regelgröße die komplexe Darstellung

[w(s) - x(s)]*FR(s)*FS(s) - x(s)oder

x(s)*[1 + FR(s)*FS(s)] = w(s)*FR(s)*FS(s)

x(s)*[1 + F0(s)] = w(s)*F0(s)

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme Regler Damit folgt für komplexen Frequenzgang des geschlossenen Regel-kreises in Abhängigkeit der Führungsgröße w

Fw(s)=x(s)/w(s)für Regelgröße x

x(s)=w(s) Fw(s)

für Eingangsgröße am Regler

w(s) - x(s) = Fw(s) = x(s)/w(s) = w(s) [Fw(s)/F0(s)] = w(s)[1/1+F0(s)]

für Regelfehler in Bezug auf den Sollwert

[w(s)-x(s)]/w(s) = 1 - [x(s)/w(s)] = 1 - Fw(s) = [1/1+F0(s)]

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Für die Übertragungsglieder erhält man damit:

• Proportionalglied: F(t) = xa(t)/xe(t) = VS

• Integrierglied:F(t) = xa(t)/xe(t) = t/TI

• Differenzierglied:F(p) = xa(s)/xe(s) = pTD

• Kennlinienglied:F(t) = xa(t)/xe(t) = NL

• Verzögerungsglied 1. Ordnung:F(t) = xa(t)/xe(t) = 1-e-(t/T)

• Verzögerungsglied 2. Ordnung:F(t) = xa(t)/xe(t) = 1-e-(ξ+t/T)

• ....

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Warum digitale Regler (embedded control)? • Flexibilität größer als bei analogen Reglern• leichtere Umstellung der Regelalgorithmen bei Änderung der

Betriebsmodi Prozess/Anlage• leichtere Adaption der Reglerparameter• unempfindlicher gegenüber Umwelteinflüssen• Parameter digitaler Regler beliebig genau einstellbar • digital realisierte Operationen lassen sich beliebig genau ausführen• Mehrgrößenregelungen mit Digitalreglern effizienter als mit

Analogreglern zu betreiben• Bei digitaler Regelung kann Protokollierung der interessierenden

zeitveränderlichen Größen nebenbei erfolgen

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Regler Mathematische Beschreibung eingebetteter (digitaler) Regler Digitale Regler durch Abtastsysteme beschreibbar mit den Teilprozessen• Abtastung• Speicherung• VerarbeitungSetzt die Abtastung zum Zeitpunkt t=0 mit der äquidistanten Abtast-periode T ein entsteht aus kontinuierlicher Zeitfunktion f(t) die Werte-folge fk = f(kt), für k=1,2,...,n.In der Regel wird der Messwert fk über die gesamte Abtastperiode gespeichert, damit f(t) während dieser Zeitspanne für die Weiterver-arbeitung zur Verfügung steht

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

AbtastungAbtastvorgang entspricht Entnahme von Funktionswerten zu diskreten Zeitpunkten aus einem kontinuierlichen Funktionsverlauf

f(t) f(kT)Abtastung

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

SpeicherungFunktionswerte der Wertefolge werden über die Abtastperiode TGespeichert ⇒ Treppenfunktion

f(kT) f(t)Speicherung

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Abtastung und SpeicherungKombination von Abtastung und Speicherung ergibt Abtasthalteglied

f(t) f(t)

Zur mathematischen Beschreibung des Abtastvorgangs werden Basis-funktionen verwendet:• Einheitssprung,• δ-Funktion,• Rampenfunktion,• Trigonometrische Funktionen,• Treppenfunktionen.

Abtasthalteglied

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Einheitssprung

>

<<

<

=

1

10

0

1

1

0

)(

ttfor

tttfor

ttfor

tuus

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

δ-Funktion

hhtutu

tu USUS )()()(

−−=δ

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Rampenfunktion

>

<<−−

<

=

1

1001

0

00

)(

ttfora

tttfortttta

ttfor

tuR

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Trigonometrische Funktionen

uenzAbtastfreqTmit

kTkTuu

Abtastung

ttu

AA

k

==

+==⇓

⇓

+=

ωωπω

ϕω

ϕω

;2

:

)sin()(

)sin()(

0

0

0

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Treppenfunktionen

kTs

kk

Ts

TskkTs

kk

USUSk

k

efsesF

se

sefsFtfL

tionTransformaLaplace

TktukTtuftf

−∞

=

−

+−−∞

=

∞

=

∑

∑

∑

−=

−==

−

+−−−=

0

)1(

0

0

1)(

][)()]([

:

])1(()([)(

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Treppenfunktionen

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

TreppenfunktionenGewichtsfaktor fk wird über das Zeitintervall T gehalten

F(s) F(s)(1-e-Ts)/s

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Technische & mathematische Beschreibung der Abtastung

f(t) fk f(t)

Technisch: Reihenschaltung von Abtastung und Speicherung

f(t) f*(t) f(t)

Mathematisch: mathematische Zerlegung in eine Reihenschaltung aus δ-Abtaster undHalteglied

Abtaster Speicher

δ-Abtaster (1-e-Ts)/s

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

AmplitudenquantisierungA/D-Umsetzer ⇒ zusätzlich zur Zeitquantisierung,

Amplitudenquantisierung

f(t) fg(k)

kontinuierlich diskret

A/D-Umsetzer

3.3 Mathematische Methoden für die Entwicklung eingebetteter RegelungssystemeAmplitudenquantisierung

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

3.3 Mathematische Methoden für die Entwicklung eingebetteter RegelungssystemeAmplitudenquantisierung

D.P.F.Möller:Rechnerstrukturen, Kap. 2 Springer Verlag, ISBN 3-540-67838-4

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Amplitudenquantisierung

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

3.3 Mathematische Methoden für die Entwicklung eingebetteter RegelungssystemeAmplitudenquantisierung

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

P R I

O R I T Ä T S D E K O D E R

an-1

Kn-2

K1

Kn-3

K2

Kn-1 Ue

R/2 y/2

Takt

a1

a0

D Q

D Q

D Q

D Q

D Q

3.3 Mathematische Methoden für die Entwicklung eingebetteter RegelungssystemeZählstrategie

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

Steuerung

Halten

Ue>Ud

E SET Zähler

Takt

D

Ausgaberegister freigeben

Z

3.3 Mathematische Methoden für die Entwicklung eingebetteter RegelungssystemeFolgestrategie

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

Halten

Schieberegister

Steuerung Dn-1

1

≥1

D

Q Q

&

1

≥1

D

Q Q

&

1

≥1

D

Q Q

&

1

≥1

D

Q Q

&

Ausgaberegister freigeben

Takt

D

Ue>Ud

Dn-2 D1 D0

Qn-1 Qn-2 Q1 Q0

3.3 Mathematische Methoden für die Entwicklung eingebetteter RegelungssystemeSukzesssive Approximation

D.P.F.Möller:Rechnerstrukturen, Kap. 2, Springer Verlag, ISBN 3-540-67838-4

DAC D Q

Ausgaberegister

Steuerung gemäß Strategie K

UDAC

-

+

Y/2

Ue/Ud

Ue>Ud

URef

Takt

D

Halten

Ausgabe- Register freigeben

a

3.3 Mathematische Methoden für die Entwicklung eingebetteter Regelungssysteme

Shannon´sches Abtasttheorem

u(t) wird eindeutig durch die Abtastwerte uk=u(kT) abgebildet

Anwendung des Shannon´schen Abtasttheorems setzt die Kenntnis der Grenzfrequenz des abgetasteten Signals voraus.

In Abhängigkeit der Abtaststelle im Regelkreis setzt sich das abgetastete Signal aus dem• Sollwert und dem Istwert zusammenoder beinhaltet nur die• Führungsgröße des Regelungssystems.

D.P.F.Möller:Rechnerstrukturen, Kap. 1, Springer Verlag, ISBN 3-540-67838-4

3.4 Componentware

Eingesetzte Mikrocontroller (µC) enthalten 8, 16, bzw. 32 Bit CPUs; 64Bit Markt ist im Entstehen.

µC zeichnen sich durch anwendungsspezifische Fertigung zahlreicherVarianten aus. Die verschiedenen Derivate unterscheiden sich durch:• Wahl des integrierten Speichers• angebotenen Peripherie Module.

Als On-Chip-Speicher werden RAM, maskenprogrammierbares ROM, EPROM und EEPROM angeboten; EEPROM als kostengünstiger Flash-Speicher, der allerdings nur in größeren Blöcken löschbar ist.

µC typischerweise im Plastikgehäuse ohne Fenster angeboten ⇒ ausEPROM wird OTP (One-Time-Programmable-Baustein).

3.4 Componentware

Damit Auflage eines Derivates lohnend, sind Volumina jenseits 1 MillionStück pro Jahr notwendig. Preis liegt dann bei 1 bis 30 DM. Typische Anwendungen die solche Auflagen versprechen sind: • Steuerungen im Automobil, • Telekommunikationsendgeräte, • Computerperipherie, • Haushaltsgeräte, • Unterhaltungs-Elektronik.

• µC in der Industrieelektronik, • Automatisierungstechnik, • Messtechnik basieren auf Standardprodukten der Volumenmärkte.

3.4 Componentware

µC • zeichnen sich durch Befehlssätze niedriger Komplexität und kurzer

Befehlsausführungszeit aus• sind Ein-Chip Mikrocomputer für Ereignisgesteuerte Echtzeit-

regelungen und -steuerungen technischer Prozesse• oft als Embedded Application eingesetzt• rauhen Umwelteinflüssen ausgesetzt

3.4 Componentware

Mikrocontroller: ergibt sich aus Integration (RISC) CPU mit Speicher und Peripherie auf einem Chip. Vielzahl vom µC enthalten µP, der zuerst für General Purpose Anwendungen als GPS entwickelt und später mit Veränderungen im Embedded Bereich eingesetzt wurde.

Beispiele:Motorola HC11 und 68K-Familie, deren Vorgänger der 6800 und der 68000 sind, Intel 8096, PIC (Mikrochip).

Allerdings gibt es eine Reihe von Architekturen, die direkt für EmbeddedAnwendungen entwickelt wurden, zu ihnen zählen M-CoreTM, TriCoreTM, die SH7000, die 8051- und die C166-Familie. Auf hohe I/O-Leistung, niedrigen Leistungsbedarf, hohe Codedichte und niedrige Produktions-kosten optimiert.

3.4 Componentware

µC für Mikrocomputersystem enthält: • µC bestehend aus µC-Kern (Core, CPU),• Speicher für Instruktionen (Programmspeicher) und Daten

(Datenspeicher) • Peripherie-Module.

3.4 Componentware

Mikrocontrollerkern: programmierbare Einheit zur Adressierung und Manipulation von Daten; zur Steuerung des zeitlichen und logischen Ablaufs eines ProgrammsSpeicher:zur Datenablage sowie zur Ablage der Programminstruktionen; RAModer ROM, sowie integrierter schneller RegisterspeicherPeripherie: liest Daten und Ereignisse ein bzw. gibt sie aus; in begrenzten Umfangprogrammierbar, um Funktionalität an Bedarf der Anwendung anzu-passen. Periphere Module digitalisieren analoge externe Signale; Timererlauben Zählen externer Pulse sowie die Erzeugung einer diskretenZeitbasis, Kommunikationsschnittstellen erlauben Datenaustausch zu anderen Bausteinen über standardisierte Protokolle; Verwendung spezieller Kommunikationsmodule DMA Busse:µC-Kern, Speicher, Peripherie tauschen tauschen Daten/Info via BUS

3.4.1 µC-Kern

Aufgaben µC-Kern: Datenmanipulation und Datenflusskontrolle.Register dient zum Deponieren von Operanden, Ergebnissen und Adressen. Verschiedene Arten von Registern im µC-Kern als Programmiermodelle bezeichnet.Befehle zur Programmierung bilden Instruktionssatz. Programmiermodell des µC entspricht Summe aller Register -die nicht sichtbar sind-; Konfigurierbarkeit des µC Kerns in der Instruktion kodiert. Selten veränderte Konfigurationen werden durch Bits in speziellen Kontrollregistern eingestellt. Kontrollregister bilden damit quasi-statische Erweiterung der Instruktionen. Interrupt ControlRegister legt z.B. fest, welche Interrupts zugelassen und welche gesperrt werden. Andere Kontrollregister legen die Funktionalität der ALU fest, bzw. von peripheren Modulen.

3.4.1 µC-Kern

KonzeptSpezifikation, Entwurf, Implementation, Test eines vollständigen µC SystemEntwurf soll grundlegende Eigenschaften von Standard µC berück-sichtigen

Einsetzbar als SoC Prozessor Kern

AnsatzInstruktion/Register Set Speicher Subsystem ALU und Control Unit Integration

3.4.1 µC-Kern

CU/ALU GoalsControl Unit SpecificationControl Unit DesignControl Unit ImplementationALU SpecificationALU DesignALU Implementation

Initial Architecture16-Bit Data, 16-Bit address integer computerLoad/Store Architecture8-Bit external Data Bus, 16-Bit internal Data BusComplete Register Transfer ability

3.4.1 µC-Kern Control Flow

Verarbeitungssequenz

Op-Code FetchOperand FetchDecodeExecute

Basic flowchart of the Control Unit

Op-Fetch

DecodeExecute

Operand Fetch

3.4.1 µC-Kern

Problem ConstraintsCode für CU soll in Flex10k20 hineinpassenEs sollen alle Zellen des 10k20 Chip neutzt werden

Architektur Restriktionen• Zahl der Instruktionen (Zustände) sind zu reduzieren

Erhöht die Ausführungsgeschwindigkeit . Bit breite Akkumulator und Daten Register auf 8 Biut beschränkt Interner Daten Bus auf 8-Bit beschränktDMA vernachlässigt Register Transfer begrenzt

3.4.1 µC-Kern Revised Control Flow

Processing Sequence:Op-Code FetchDecodeOptional Operand FetchExecute

Basic flowchart of the Control Unit

3.4.1 µC-Kern ALU Capabilities

Bezogen auf die Restríktionen wurden folgende ALU Funktionen realisiert: Arithmetische Operationen:

AdditionSubtraktionInkrementDekrement

Operanden: Akkumulator und Daten RegisterErgebnisse: Speicherung im Akkumulator

3.4.1 µC-Kern Instruction Set

Instruktions Sätze:Instruktions Satz SpezifikationInstruktions Satz AssignmentRegister Satz SpezifikationAssembler Implementation

Initialer Instruktions SatzµC entwickelt für zwei Instruktions Typen:

Long Instructions: 8-Bit op-code, 16-Bit operandShort Instructions: 8-Bit op-code only

µC verfügt über 6 Instruktionsatz Arten

3.4.1 µC-Kern Instruktionssatz Arten

Arithmetic (11 Instructions)Load/Store Direct (3 Instructions)Load/Store Indirect (3 Instructions)Load Immediate (1 Instruction)Register Transfer (12 Instructions)Flow Control( 2 Instructions )

Total: 32

3.4.1 µC-Kern

Probleme

Größenbeschränkung erfordert ein Re-Design der µC ArchitekturÄnderungen betreffen:

Daten Register und Akkumulator, wurden von 16-Bit auf 8-Bit reduziertAdressierungs Modi wurden reduziertInstruktionssatz Arten wurden beschränkt

3.4.1 µC-Kern Reduzierter Instruktions Satz

Arithmetic (11 Instructions)Load/Store Indirect (2 Instructions)Load Immediate (3 Instructions)Register Transfer (2 Instructions)Flow Control (2 Instructions)

Total: 20

3.4.1 µC-Kern Assembler Entwurf

Assembler enthält folgende Funktionalität:Symbolische Beschreibung von Konstanten und Adressen Konvertiert nemonischen Op-Code in binären Op-CodeErzeugt Maschinen Code in Form die geladen und ausgeführt werden kann

Assembler Tasks:Liest das Assembler Programm. Unterteilt das Programm in Symbole.Überprüft die Werte der Symbole mit den Symbolen der Einträge in die Symbol Tabelle Bei Übereinstimmung schreibt der Assembler den äquivalenten Binären Code für das Assembler Programm.Nachdem alle Symbole in die äquivalenten Binärwerte übertragen wurden wird das ausführbare Maschinen Proramm erzeugt.

3.4.1 µC-Kern Assembler Design

Initialer AssemblerAssembler in ‘C’ geschriebenErzeugt Code für die initiale µCCPU ArchitekturRevision der µCCPU erfordert eine Revision des Assemblers

Geänderter AssemblerEntwurf auf Basis neuer und reduzierter Instruktionssätze, behält jedoch die Eigenschaften der älteren Assembler Version.Fügt Code für neue Instruktionen hinzu wie beispielsweise BEQ, INC , DEC etc. Nutzung von “third party utility” für S-Record Export

3.4.1 µC-Kern Assembler Design

S-Record Format Motorola S-records are an industry-standard format for transmitting binary files to target systems and PROM programmers.The µCCPU processor uses a 32Kx8 flash memory which must be programmed using an EEPROM burning device.S-Record Files form the bridge form the assembler to the EEPROM Burner

S-Record DescriptionThe S-record standard is as follows:S<type><length><address><data....><check> where: <type> Record type<length> Number of bytes on a line<address> Location of the line in memory<data> Data bytes: Each pair of Hex character represents one byte in

memory.<check> Is one’s complement of 8-bit checksum. Used for error checks

3.4.1 µC-Kern S-Record Example

Example S00600004844521B

S-record type S0, indicating that it is a header record.06 Hexadecimal 06 (decimal 6), indicating that six character pairs (or ASCII bytes) follow.0000 Four-character, 2-byte, address field484452 ASCII H, D and R - "HDR".

1B The checksum.

3.4.1 µC-Kern Assembler Funktion

Liest Anwender Programm vom Input FileUnterteilt Anwender Programm in TokenKonvertieret die gelesenen Token des Anwender Programms in vordefinierte Binäre Muster Falls erforderlich werden Operanden geparstExportiert Binäre Muster und Operanden in einen sequentiellen Binären File„Third party software utility“ konvertiert Binärfile in einen S-RecordFile

3.4.1 µC-Kern Assembler Design

FoundNot

FoundGenerate Binary Code

START

Get input file

Parser

Check Tokens Write Output file

S-REC Converter

S-Rec format for EPROMEnd

3.4.1 µC-Kern Memory Subsystem

MCU Entwurfsziele:Definiton der Memory System SpezifikationMCU Entwurf und Implementation basierend auf VHDLSimulation der MCUEntwurf und Implementation externer Memory Komponenten

3.4.1 µC-Kern Testing

Table #1 $00000-$07FFF (ROM)Inputs Outputs

XXXXX11XXXXX0110101101110100

WRITE*READ*CS_RAM*CS_ROM*MU_ACK*CU_R/W*CU_STROBE*

Table #2 Table #2 $08000$08000--$0FFFE (RAM)$0FFFE (RAM)InputsInputs OutputsOutputs

XXXXX11XXXXX0110011100101100

WRITE*READ*CS_RAM*CS_ROM*MU_ACK*CU_R/W*CU_STROBE*

3.4.1 µC-KernPCB

ROM chip AtmelAT28C256-15RAM chip Cypress Cy7C199-15ROM address range $0000 to $7FFFRAM address range $8000 to $FFFF

3.4.1 µC-Kern RAM Timing

Read Cycle for RAM – CY7C199-15

Write Cycle for RAM – CY7C199-15

tACE = 15ns

tWC = 15ns

tSCE = 10ns

to tAW =10ns

3.4.1 µC-Kern ROM Timing

Read Cycle for ROM – 28C256-15

tACC = 150ns

Each Wait State = 1 / 25*10^6 = 40ns

3.4.1 µC-Kern Goals Achieved

Alle Entwurfsziele wurden erreicht :Memory System SpecificationMemory und I/O Controller EntwurfMCU ImplementationMCU Simulation basierend auf Max-Plus II

Entwurf und Aufbau eines externen Memory board

3.4.1 µC-Kern Integration Goals:

• Target board (UP1, FLEX-10K20) Expertise

• Target board Capability Estimation

• Target board Interface Capability Estimation

• Technical review of the implementations and Simulations.

• Component level implementation of CPU system.

• Integration of all subsystems

3.4.1 µC-Kern About the UP1 Board

2 Programmable DevicesEPM7128 And FLEX 10k20Input : Switches Output : Seven Segment And LEDsExternal Connections To Programmable Devices.Configurable From PC

Byte-Blaster MV Cable Used for H/W Configuration.

• On-board 25.175 MHz Clock.

• Momentary Push Button Switches

• VGA Port And Mouse Port.

• Select Either Device Or Both.

• EPROM Configuration For FLEX10k20.

3.4.1 µC-Kern Flex10k20

•Reconfigurable SRAM Elements.

•240-pin TQFP Package.

•1,152 Logical Elements And

•6 EAB’s.

•20,000 Typical Gates

•12,288 Total RAM Bits

3.4.1 µC-Kern On Board Clock

•25.175 MHz CRYSTAL

•Verification Of Clock Frequency

•Simple VHDL Code

• Uses On Board Clock As Input Pin.

• Frequency Verified On Oscilloscope.

• Verified Using Decrement Counter.

• Output Checked On 7 SEG Display.

3.4.1 µC-Kern Implementation

µCCPU Coded In VHDL.

Configured Using Max-plus II Into Flex10k20.

Uses External Memory Interface.

ROMRAM

3.4.1 µC-Kern Implementation Overview

Stages

Description Of The External Pin Out Of CSUCPU.

Description Of The Architecture Body.

Defining Internal Signals And Register

Defining ALU And Memory Unit As Components

Coding The Control Unit State Machine.

Simulation.

Timing Diagram Using On Max-plus II

Verified The Operation Of State Machine

3.4.1 µC-Kern Implementation Overview

•Configuration

• Assigning FLEX10k20 Pins To Signals

• Compilation Of VHDL Code And Debugging

Problem!!!

Code Could Not Accommodate Into FLEX10k20

USED MORE THAN 1700 LE’s

FLEX10K20 PROVIDES 1152 LE’s

3.4.1 µC-Kern Solution

Initially 16 Bit, Redesigned To 8 Bit Memory Unit Still Outside The Main Code.Design as Implemented did not fit in the FLEX10K20The memory unit was integrated into the main program along with the control unit.The result was the code properly accommodated into the Flex10k20Chip.The code used over 95% of the chip.

3.4.1 µC-Kern Control Unit States

r00 – Reset state

f00-f02 – Fetch State

d00 – Decode State

e_alu_00 – ALU Execution

e_rti_00 – Register Transfer Execution

e_ldi_00-e_ldi_05 – Load Immediate Execution

e_ldmi_00-e_ldmi_02 – Load Indirect Execution

e_stmi_00-e_stmi_02 – Store Indirect Execution

e_gt_00-e_gt_07 – Branch Execution

3.4.1 µC-Kern

Testing the µCTest A, Displaying AB

; basic output test

ldii $ffff

ldid $AB

loop stmd

bra loop

3.4.1 µC-Kern

Testing the µCTest A, Listing File

CSUCPU Assembler V1.0 Listing File

File name: test2.lst

Address Data Opcode Operand

$0000 $22FFFF LDII $FFFF

$0003 $20AB LDID $AB

$0005 $60 STMD

$0006 $300005 BRA $0005

3.4.1 µC-Kern

Testing the µCTest A, S-Rec File

S0030000FC

S117000022FFFF20AB6030000500000000000000000000007F

S9030000FC

3.4.1 µC-Kern

Testing the µCTest A Result

“Ab” was successfully displayed on the Seven segment Display

3.4.1 µC-Kern

Testing the µCTest B, Basic Input Output Test

; basic input/output test

ldid $05

ldii $FFFF

loop ldma

add

stma

bra loop

3.4.1 µC-Kern

Testing the µCTest B, Basic Input Output Test

CSUCPU Assembler V1.0 Listing File

File name: test3.lst

Address Data Opcode Operand

$0000 $2005 LDID $05

$0002 $22FFFF LDII $FFFF

$0005 $41 LDMA

$0006 $01 ADD

$0007 $61 STMA

$0008 $300005 BRA $0005

3.4.1 µC-Kern

Testing the µCTest B, S-Record File

S0030000FC

S1170000200522FFFF410161300005000000000000000000E2

S9030000FC

3.4.1 µC-Kern

Testing the µCTest C, Delay Counter

stma

;

outer ldma

dec

beq loop

stma

;

ldia $ff

inner dec

beq outer

bra inner

; delay loop testldia $00ldii $8000stma

loop ldii $8000ldma

inc

stma

ldii $ffff

;

stma

ldia $80

ldii $8001

3.4.1 µC-Kern

Testing the µCTest C, Delay Counter

CSUCPU Assembler V1.0 Listing File

File name: delay1.lstAddress Data Opcode Operand$0000 $2100 LDIA $00$0002 $228000 LDII $8000$0005 $61 STMA$0006 $228000 LDII$8000$0009 $41 LDMA$000A $09 INC$000B $61 STMA$000C $22FFFF LDII $FFFF

$000F $61 STMA$0010 $2180 LDIA $80$0012 $228001 LDII

$8001$0015 $61 STMA$0016 $41 LDMA$0017 $0A DEC$0018 $310006 BEQ

$0006$001B $61 STMA$001C $21FF LDIA $FF$001E $0A DEC$001F $310016 BEQ

$0016$0022 $30001E BRA

$001E

3.4.1 µC-Kern

Testing the µCTest C, S-Record File

S0030000FC

S117000021002280006122800041096122FFFF6121802280CA

S11700140161410A3100066121FF0A31001630001E000000B2

S9030000FC

3.4.1 µC-Kern

Beispiel 1:Interrupt bewirkt Programmverzweigung in Interrupt-Service-Routine. Während Abarbeitung können z.B. nur Interruptanforderungen mit höherer Priorität die Interrupt-Service-Routine unterbrechen. Restliche Interruptanforderungen erst nach Beendigung der laufenden Interrupt-Service-Routine bearbeitet.

Derartige Zustandsänderungen könnten in der Instruktion bzw. in denErgebnisoperanden abgespeichert werden. Dies würde zu sehr langen Instruktionen bzw. Operanden führen. Daher werden neben denKontrollregistern spezielle Register im µC-Kern integriert, welche den Zustand (Status) des µC-Kernsspeichern. Diese Statusregister sind z.B. Programm-Status-Register (PSR), Interrupt-Status-Register (ISR), Multiplier-Status-Word (MSW), etc.

3.4.1 µC-Kern Beispiel 2:Programm-Status-Word (PSW) C166-Architektur als Beispiel fürStatusregister PSW signalisiert einerseits Eigenschaften des Ereignisses der letzten arithmetischen Operation (ALU-Status), andererseits dient es zur Konfiguration des Interruptsystems bzw. des externen Busses.

3.4.2 Embedded Fuzzy Controller3.4.2.1 Fuzzy Set Theorie

Fuzzy Set Theorie 1965 von Prof. Lotfi A. Zadeh begründet; basierend auf Verfahren zur Verarbeitung unscharfer Konzepte. Grundbegriffe: • Unscharfe Menge (fuzzy set) mathematisches Konzept zur

Repräsentatiion vager Angaben, welches graduelle Mengenzu-gehörigkeit erlaubt

• Unscharfe Logik (fuzzy logic) isomorphes Konzept unscharfer Mengen, welches den Umgang mit graduellen Wahrheitswerten regelt

• Unscharfe Regel (fuzzy rule) Regel deren Prämissen- und Konsequenzprädikate unscharfe Mengen enthalten

• Unscharfes Schliessen (fuzzy reasoning, approximative reasoning) mathematische Notation zur Formalisierung und Auswertung unscharfer Regelbasen

• Unscharfe Regelung (fuzzy control) Einbettung unscharfer regelbasierter Systeme in technischen Anwendungen

3.4.2 Embedded Fuzzy Controller3.4.2.1 Fuzzy Set Theorie

Hinzu kommen:• Stochastische Unschärfe: wird in Zahlen zwischen 0 und 1 als

Wahrscheinlichkeit für das Eintreten eines Ereignisses ausge-drückt. Wahrscheinlichkeiten werden nach mathematischen Ver-fahren berechnet oder geschätzt und haben keinen Bezug zum tatsächlichen Eintreten eines Ereignisses. In diesem Sinne täu-schen sie scharfe Realitäten oft nur vor

• Lexikale (sprachliche) Unschärfe: Menschen können sprachli-che Unschärfe im Kontext oft zu Begriffsdefinitionen verdichten, wohingegen Rechner nicht in der Lage sind, selbständig Begriffe im Kontext abzuklären

• Informale Unschärfe: basiert häufig auf mangelndem Wissen und fehlenden Informationen, die häufig auch nicht zu beschaffen sind

3.4.2 Embedded Fuzzy Controller3.4.2.2 Componentware für Fuzzy Control

Embedded Fuzzy Control Componentware (EFCC) verfügt über Befehle, die den Befehlsatz des Hauptprozessors um Makroinstruktionen ergän-zen. Das Architekturmodell der EFCC unterscheidet sich von klassischen Ansätzen, hat aber Gemeinsamkeiten:• Kommunikationsschnittstelle; getrennter Befehls- und Datensatz• Befehlssatz; wenige einfache Befehle, alle in einem Taktzyklus

ausgeführt• Interne Ablaufsteuerung festverdrahtetRechenwerk der EFCC besteht aus:• Fuzzyfizierung• Aggregation• Inferenz• Akkumulation• Defuzzyfizierung

3.4.2 Embedded Fuzzy Controller3.4.2.2 Componentware für Fuzzy Control

Embedded Fuzzy Control Componentware (EFCC) beinhaltet vier Kom-ponenten:• Speicherbänke; nehmen Regelbasis und Fuzzy Sets auf, bilden

zusammen mit Registerbank Schnittstelle zwischen Kommunikati-onssteuerung und Inferenzmaschine; Kommunikationssteuerung greift schreibend auf Inferenzmaschine und lesend auf Speicher-bänke zu

• Registerbank; speichert Operanden, Funktionsparameter, Zeiger Datenadressierung, Inferenzmaschine legt Berechnungsergebnisse in Registerbank ab, Kommunikationssteuerung und Inferenzma-schine greifen nur schreibend oder nur lesend auf Registerbank zu

• Kommunikationssteuerung; Initialisierung: Regelwerke und Fuzzy Sets, Operanden- und Parameter-Register, Berechnung; Übertragung von Ergebnis und Status

• Inferenzmaschine; Algorithmus des unscharfen Schliessens

3.4.2 Embedded Fuzzy Controller3.4.2.3 Auswahl der Zielplattform

Embedded Fuzzy Control Componentware (EFCC) basierend auf PLD beinhalten Entwicklungsumgebungen und bieten vollautomatisches Zu-ordnen, Plazieren und Verbinden (Mapping, Place & Route), Signallauf-zeit-Analyse und Simulations-Werkzeuge. Auswahl Zielplattform• PLD muss sehr schnell sein, d.h. hohe Schaltfrequenzen ermögli-

ichen und kurze Pin-zu-Pin-Verzögerungszeit haben• PLD muss über ausreichende Kapazität hinsichtlich kombinatori-

scher und sequentieller Logik verfügen• Speicherintensive Anwendungen erfordern ausreichend große und

schnelle interne RAM-Strukturen des PLD

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A• Simple PLD (monolithische PLD),

• Complex PLD (blocksegmentierte PLD)

• Field-Programmable-Gate-Arrays (FPGA werden als Channel-Array-PLD bezeichnet)

Diese Einteilung ist willkürlich und weder vollständig noch disjunkt, sie entstammt dem Bemühen zur Schaffung einer strukturellen Übersicht.

D.P.F.Möller:Rechnerstrukturen, Kap. 6, Springer Verlag, ISBN 3-540-67838-4

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A

D.P.F.Möller:Rechnerstrukturen, Kap. 6, Springer Verlag, ISBN 3-540-67838-4

PAL, GAL, FPLA

(bipolar, CMOSEPROM/

MACH (AMD, CMOS EEPROM)MAX (Altera u. Cypress, CMOS EPROM)

FPGA (Plus Logic, CMOS EPROM)PEEL (ICT, CMOS EEPROM)PML (Signetics, CMOS EPROM)ATVxxxx (Atmel)

20 44 84 120 >175

LCA 20xx/30xx/31xx/40xx (Xilinx, CMOS SRAM)AT10xx/AT12xx (Actel, CMOS Antifuse)ATT1C05 (AT&T, CMOS SRAM)pASIC (QuickLogic u. Cypress, Vialink Antifuse)

SPLDs (monolithische PLDs)(100...500 Gatteräquivalente, 60...150 MHz)

(Segmented-BlockPLDs) (500...5000Gatteräquivalente,25...150 MHz)

(Channeled-Array PLDs)(1000...20000 Gatter-äquivalente, 10...100MHz)

Anzahl der externen Anschlüße

100

10000

1000

Gatteräquivalente

CP2xxxx (Crosspoint Solution, CMOS Antifuse)CLi600x (Concurrent Logic, CMOS SRAM)

(is)pLSI (Lattice, CMOS EEPROM)

CPLDs

FPGAs

EEPROM/)

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

Programmierbare Rückkopplung

Eingangs-Block

Ausgangs-Block

ProgrammierbareUND/ODER-Matrix (Array)

Eingang Ausgang

D.P.F.Möller:Rechnerstrukturen, Kap. 6, Springer Verlag, ISBN 3-540-67838-4

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A

Globale Struktur der LCAs

General PurposeInterconnect

DirectConnection

CLB

Switching Matrix

Longlines

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A

IOBs (Xilinx)

=1

=1

Out

/OE

Out-Invert

/OE-Invert

D Q

OutputSelect

SlewRate

PassivePull-Up

R

Flip-Flop

DQ

R

Flip-Flop oder

I/O-PAD

Latch

Direct_In

Registered_In

(*1)

(Global Reset)

(*1)

(*1)

CK1

CK2

.o

.i

.q

.t

.ik.ok

Programmable Memory Cells VCC

(*2)

(*1) Program Controlled Multiplexer

(*2) Programmable Interconnection Point (PIP)

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A

Blockstruktur MACH 445

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

8

16 16 16

33 24

8 I/O-Pins

8

ClockGenerator

4

4

4

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

8

16 16 16

33 24

8 I/O-Pins

8

ClockGenerator

4

4

4

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

8

16 16 16

33 24

8 I/O-Pins

8

ClockGenerator

4

4

4

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

8

16 16 16

33 24

8 I/O-Pins

8

ClockGenerator

4

4

4

6 CLK0/I0, CLK1/I1, CLK2/ICLK3/I4, I2, I5

Central Switch Matrix

Block A Block B Block C Block D

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

24

8 I/O-Pins

ClockGenerator

Block E

334

16

88

4

416 16

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

24

8 I/O-Pins

ClockGenerator

Block F

334

16

88

4

416 16

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

24

8 I/O-Pins

ClockGenerator

Block G

334

16

88

4

416 16

AND-Logic-Array(66 In, 90 AND-Lines) und

Logic Allocator

Macrozellen (16) und Output Switch (8 aus 16)

InputSwitch

I/O-Zellen (inkl. Input Reg.)

8

24

8 I/O-Pins

ClockGenerator

Block H

334

16

88

4

416 16

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A

Blockdiagramm des ispLSI1032

D7 D6 D5 D4 D1 D0D3 D2

Input Bus

Output Routing Pool

I/O-Zellen Inputs

A0

A1

A2

A3

A4

A5

A6

A7

Output

Routing

Pool

Inputs

I/O-Zellen

Input

Bus

Megablock

GenericLogicBlock

B0 B1 B2 B3 B6 B7B4 B5

Output Routing Pool

I/O-Zellen Inputs

Input Bus

C7

C6

C5

C4

C3

C2

C1

C0

Output

Routing

Pool

Inputs

I/O-Zellen

Input

Bus

Global Routing Pool

Y0 Y3

ClockDistribution

Network

CLK0CLK1CLK2IOCLK0IOCLK1

4#

(GRP)

3.4.2.3.1 Programmierbare Logikbausteine (PLD)

A

Generic Logic Block eines ispLSI1032

&&&&&&&&&&&&&&&&&&&&

2 ded. Inputs16 Signale vom GRP

AND-Array

>1

>1

>1

>1

Zuordnung inGrundkonfiguration

D QMUX

D QMUX

D QMUX

D QMUX

D, T- und JK-FlipflopProduct TermSharing Array

&>1Global RESET

PT Reset

an alle Register

& PT Clock

CLK0

CLK2CLK1

MUXKontrollfunktionen

& PT Output Enable (1 pro Megablock) zum ORP

zum GRP

3.4.2 Embedded Fuzzy Controller3.4.2.4 Entwurfsmethodik

Unter der Prämisse der Maximierung der Schaltgeschwindigkeit sind rein grafische Ansätze als Entwurfsmethodik zweckdienlich. Die grafi-sche Logikbeschreibung, in Form von Schaltplänen, ermöglicht eine bes-sere Kontrolle über den Syntheseprozess als es mit abstrakten Beschrei-bungssprachen wie Verilog oder VHDL möglich ist. Zudem lassen sichbausteinspezifische Merkmale besser berücksichtigen. Das Syntheseer-gebnis zeichnet sich im allgemeinen durch eine höhere Geschwindigkeitund eine besserer Ausnutzung der Logik-Ressourcen aus.

3.4.2 Embedded Fuzzy Controller3.4.2.5 Fuzzyfizierung

Während der Fuzzyfizierung werden die Erfüllungsgrade aller Aussagen auf den linken Regelseiten ermittelt. Dazu wird für jede Aussage der Form:

linguistische Variable = linguistischer Wert

der Zugehörigkeitsgrad des Fakts zum bezeichnenden Fuzzy Set ermit-telt. Jeder Aussage innerhalb eines Ausdrucks ist nach der Fuzzyfizie-rung ein Erfüllungsgrad zugeordnet. Der folgende Pseudocode-Abschnitt veranschaulicht die Fuzzyfizierungfor i:=1 to n do

for j=1 to m doGrad [ i ] [ j ]:= Regel [ i ] [ j ] [Fakt [ j ]];

3.4.2 Embedded Fuzzy Controller3.4.2.6 Aggregation

Als Aggregation wird die UND-Verknüpfung der Aussagen-Erfüllungs-grade innerhalb eines Ausdrucks bezeichnet. Diese Verknüpfung ist in der Regel als Minimum-Operator realisiert. Nach der Aggregation ist jedem Ausdruck ein Kompatibilitätsmaß zugeordnet.

for i:=1 to n dobegin

Komp [ i ]:= Grad [ i,1 ];for j:=2 to m do

Komp [ i ]:= min (Komp [ i ], Grad [ i,j ]);end;

3.4.2 Embedded Fuzzy Controller3.4.2.7 Inferenz

Während der Inferenz wird für jede Regel der unscharfe Ergebniswert(d.h. ein Fuzzy Set) unter Verwendung der Schlussfolgerung und des sog. Kompatibilitätsmasses des Ausdrucks ermittelt. Dazu stehen ver-schiedene Methoden zur Verfügung, z.B. die Minimum-Methode und die Produkt-Methode.Aus Gründen der Einfachheit wird in der Regel die Minimum Methode eingesetzt bei der das Folgerungen Fuzzy Set mit dem Kompatibilitäts-maß gekappt wird. Bei der Produktmethode werden die Zugehörigkeitswerte mit dem Kompatibilitätsmaß multipliziert.Für die Minimum Methode giltfor i:=1 to n do

for k:=1 to q doFolg [ i ] [ k ]:= min (Folg [ i ] [ k ], Komp [ i ])

3.4.2 Embedded Fuzzy Controller3.4.2.8 Akkumulation

Während der Akkumulation werden die verschiedenen Folgerungen-Fuzzy-Sets per ODER-Verknüpfung zu einem einzigen Ergebnis-Fuzzy-Set überlagert. Dazu wird für jede Abszisse das Maximum der Zugehörigkeitsgrade aller Ergebnis-Fuzzy-Sets ermittelt:

for k:=1 to q dobegin

Ergeb [ k ]:= 0;for i:=1 to n do

Ergeb [ k]:= max (Ergeb [ k ], Folg [ i ] [ k ]);end;

3.4.2 Embedded Fuzzy Controller3.4.2.9 Defuzzyfizierung

Bei regelungstechnischen Anwendungen ist es notwendig, aus dem unscharfen Ergebniswert in Form eines Fuzzy Sets eine scharfe Aus-gangsgröße zu berechnen. Eine gängige Methode dafür ist die Bildung des Flächenschwerpunktes (Center of Gravity) durch Division des Flächenmoments durch den Flächeninhalt

CoG = M / F mit M = INT x*µ(x)dx und F = INT µ(x)dxDie Bestimmung von Flächeninhalt und Flächenmoment erfolgt im diskreten Fall durch einfache Summation der (gewichteten) Zugehörigkeitswerte:F:= 0; M:= 0;for k:=1 to q dobegin

F:= F+Ergeb [ k ];M:= M+k*Ergeb [ k ];

end;if F<>0 then

CoG:= M/F

3.4.2 Embedded Fuzzy Controller3.4.2.10 Modellentwurf

Der zu entwerfende Co-Prozessor soll universell sein da Regelbasis und Fuzzy Sets variabel sind, Programmierung beschränkt sich auf Datenini-tialisierung, Laden der Operanden und die Initiierung der Berechnung. Es handelt sich nicht um vollwertigen Rechner a la von-Neumann- oder Harvard-Architektur sondern um eine Maschine die eine ganz bestimmte Operation um einige Größenordnungen beschleunigen soll. „Hardwarebeschleuniger“ ⇒ Fuzzy Customized Computing Machine(FCCM) ⇒verfügt über Befehle die Befehlssatz des Hauptprozessors um Makroinstruktionen ergänzen aber über keinen eigenen BefehlsspeicherAuch wenn sich die Architektur von klassischen Ansätzen unterscheidet, finden sich gewisse Elemente wieder:• Kommunikationsschnittstelle, weist getrennten Befehls- und

Datenbus auf• Befehlssatz besteht aus wenigen einfachen Befehlen die alle in

einem Taktzyklus ausgeführt werden• Interne Ablaufsteuerung festverdrahtet

3.4.2 Embedded Fuzzy Controller3.4.2.11 Entwurf

• FCCM: Co-Prozessor mit universeller Kommunikationsschnittstelle• FCCM: verfügt über Speicher für Regelbasis und Fuzzy Sets• FCCM: verarbeitet bis zu vier 8 Bit Eingangswerte, liefert 8 Bit

Ausgangswert• FCCM: Wertebereich auf das Intervall von 0 bis 255 normiert• Fuzzy Sets liegen in normierter 8-Bit Quantisierung vor (0-255)• Fuzzy Set benötigt 256*8Bit = 256 Byte Speicherplätze• Regelbasis maximal 256 Regeln; in den Regeln werden nicht die

Fuzzy Sets, sondern die Indizies von Fuzzy Sets gespeichert• FCCM: arbeitet nach dem Prinzip des unscharfen Schließens• UND/ODER-Verknüpfungen durch Maximum- bzw. Minimum-

Operator• Inferenz und Akkumulation mit wählbarer Schrittweite realisiert

3.4.2 Embedded Fuzzy Controller3.4.2.11 Entwurf

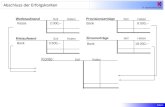

FCCM besteht im wesentlichen aus:• Speicherbänken: beinhalten Regelbasis und Fuzzy Sets; beinhal-

tet mit Registerbank Schnittstelle zwischen Kommunikationssteue-rung und Inferenzmaschine

• Registerbank: speichert die von Inferenzmaschine benötigten Operanden, verschiedene Funktionsparameter und Zeiger für die Datenadressierung, sowie Berechnungsresultate und Statusinfor-mationen (Shared Memory)

• Kommunikationssteuerung: übergeordnetes Steuerwerk der FCCM, bildet Schnittstelle zwischen Host und FCCM-Kern mit an-geschlossenen Speichern

• Inferenzmaschine: Kern der FCCM; realisiert den Algorithmus des unscharfen Schließens

3.4.2 Embedded Fuzzy Controller3.4.2.11 Entwurf

D.P.F.Möller:Rechnerstrukturen, Kap. 9, Springer Verlag, ISBN 3-540-67838-4

3.4.2 Embedded Fuzzy Controller3.4.2.12 Regelbasis

Regelbasis enthält die Regeln, im PLD gespeichert, z.B. 256 Regeln.Dazu sind 8 RAM-Module in der Konfiguration 32x18 Bit notwendig, die als logischer Block von 256x18 Bit zusammengefasst werden. Die 18 Bit enthalten vier 4 Bit Werte (Wert 0 Bit 0-3, Wert 1 Bit 4-7, etc.) als Indizes der Eingangs-Fuzzy Sets und ein 2 Bit Ergebnis als Index des Ausgangs-Fuzzy-Sets (Bits 16 und 17).Regelbasis als Ringspeicher realisiert, nach Bearbeitung von Regel 255 wird mit Regel 0 fortgesetzt

3.4.2 Embedded Fuzzy Controller3.4.2.12 Regelbasis

Regelbasis kann aus einer oder mehreren Regelwerken bestehen; nicht in feste Segmente unterteilt; erste und letzte Regel des akuten Regel-Regelwerkes werden dynamisch durch entsprechende Zeiger markiert.Regelstruktur entspricht der Form:WENN

Eingang 1 = Wert 1 UNDEingang 2 = Wert 2 UNDEingang 3 = Wert 3 UNDEingang 4 = Wert 4

DANNAusgang: = Ergebnis

Eingang 1 bis 4 und Ausgang sind linguistische VariableWert 1 bis 4 und Ergebnis sind Fuzzy Sets bzw. Indizies von Fuzzy SetsFür Eingangswerte stehen 16 Fuzzy Sets, für Ausgangswert 4 FuzzySets zur Verfügung

3.4.2 Embedded Fuzzy Controller3.4.2.13 Fuzzy Sets

Wertebereich der Eingangsvariablen wird aus Optimierungsgründen in externen SRAM-Baustein gespeichert; Kapazität 32K 8-Bit-Worte; Zugriffszeit max. 12 ns.⇒ jeder Fuzzy-Set-Block 1benötigt 6x256 = 4096 Byte benötigt ⇒ Speicherbaustein wird in 8 Segmente zu je 16 Fuzzy Sets (Fuzzy-

Set-Block) unterteilt. Das einzelne Fuzzy Set verfügt wiederum über 256 Bit.

3.4.2 Embedded Fuzzy Controller3.4.2.14 Speicherschnittstelle

Anbindung externer Speicherbausteine an FCCM durch Steuerleitungen (dünne Linien) und Adress- und Datenbusse (dicke Linien). Speicherbau-stein verfügt neben 15 Bit breiten Adressbus und 8 Bit Datenbus noch über drei Steuerleitungen: CS (Chip Select), OE (Output Enable), WE (Write Enable)

3.4.2 Embedded Fuzzy Controller3.4.2.14 Speicherschnittstelle

Schreibvorgang durch High-Pegel auf CS und WE eingeleitet; zum Lesen CS und OE müssen gleichzeitig High sein. Low-Pegel auf CS deaktiviert Speicherbaustein. Die oberen 3 Bit des Adressbus (Bit 14, 13, 12), von SEL bestimmt, adressieren die Segmente 0-7 der Fuzzy Sets, die unteren 12 Bit des Adressbus adressieren Fuzzy Set innerhalb eines Segments (0-15) (Bit 11 – 8) und die Abszisse (0-255), (Bit 7 – 0).Die Anzahl der für die Speicheranbindung erforderlichen FCCM-Pins beträgt insgesamt:Pins = CS + OE + WE + SEL + 4xADR + 4xDAT =

1 + 1 + 1 + 3 + 4x12 + 4x8 = 86

3.4.2 Embedded Fuzzy Controller3.4.2.15 Registerbank

Registerbank der FCCM besteht aus 12 Registern, die entsprechendihrer Funktion in vier Registergruppen eingeteilt sind:• Speicher-Adressierung

SEL (Segment Selector), 4 Bit; ADR (Adress Pointer), 12 Bit• Funktionsparameter

PRC (Precision), 2 Bit; BEG (Begin Rule), 8 Bit; END (End Rule), 8 Bit

• Operanden IN0, IN1, IN2, IN3 (Input Values), 4x8 Bit

• Resultat & StatusOUT (Output Value), 8 Bit; ERR (Output Error), 1 Bit; INT (Output Integral), 16 Bit

3.4.2 Embedded Fuzzy Controller3.4.2.16 Kommunikationssteuerung

Kommunikation zwischen Host und FCCM über universelle Schnittstelle mit getrenntem Daten- und Befehlsbus

3.4.2 Embedded Fuzzy Controller3.4.2.16 Kommunikationssteuerung

Neben der Befehlsschnittstelle die aus 3 Bit Befehlsbus (CMD) und bidirektionalen 32 Bit Datenbus (DATA) besteht, gibt es noch Status-und Steuersignale:• VALID (Command Valid)• DAC (Data Accepted)• RESET (Processor Reset) FCCM initialisieren• BUSY (Operation Busy)• IRQ (Interrupt Request)• DVA (Data Valid)• ERR (Error)Kommunikationsschnittstelle benötigt 42 I/O-Pins; Speicherschnittstellen benötigen 86 Pins. Bei PLD mit 196 – 128 = 68 Pins frei verfügbare I/O-Pins

3.4.2 Embedded Fuzzy Controller3.4.2.17 Fuzzy Embedded Controller Architecture

D.P.F.Möller:Rechnerstrukturen, Kap. 9, Springer Verlag, ISBN 3-540-67838-4

3.5 Open-Loop and Closed-Loop Embedded Control

Control System minimally consists of several parts:

• Plant – the process –, physical system to be controlled• Output, interest in controlling• Reference input• Actuator, device we use to control the input to the plant• Controller• Disturbance, additional undesirable input

3.5 Open-Loop and Closed-Loop Embedded Control

Closed-Loop Automobile Cruise Controller:

• Reduce speed error caused by disturbances, like grade or wind, by enabling the controller to detect speed errors and correct them

• P-Controller• Control goal is to achieve υ equal to r in steady state, with υ as

car´s current speed, r as reference signal

3.5 Open-Loop and Closed-Loop Embedded Control

Closed-loop cruise controller trying to accelerate from 20 to 50 mph, ignoring disturbance

Same closed-loop cruise controller trying to accelerate from 20 to 50 mph, with disturbance

3.5 Open-Loop and Closed-Loop Embedded Control

3.5 Open-Loop and Closed-Loop Embedded Control

A better controller could be designed if it could predict the future. Both controllers haveforced the output halfway to the desired value. But the controller for a) short start to reduce the plant input, while the controller for b) should have increased the input earlier.

3.5 Open-Loop and Closed-Loop Embedded Control

Software Coding of a PID Controller using Cvoid main (){

double sensor_value, actuator_value, error_current;PID_DATA pid_data;PidInitialize(&pid_data);while (1) {

sensor_value = SensorGetValue();reference_value = ReferenceGetValue();actuator_value = PidUpdate(&pid_data,sensor_value,reference_value);ActuatorSetValue(actuator_value);

}}Creating main function to loop forever. During each iteration, we first read the plant output sensor, read the current desired reference input value, and pass this information to Function PidUpdate. PidUpdate determines the value of the plant actuator, which we then use to set the actuator.Reading the sensor will typically involve an ADC, and setting the actuator will involve a DAC.

3.5 Open-Loop and Closed-Loop Embedded Control

Software Coding of a PID Controller using C

Data structure of PID_DATA has the following form:

typedef struct PID_DATAdouble Pgain, Igain, Dgain {double sensor_value_previous; // find the derivativedouble error_sum; // cumulative error

}

PID_DATA holds three gain constants, which we assume are set in the PidInitialize Function. It also holds the previous sensor value, which will be used for the derivative term. Finally, it holds the cummulative sum error values, used for the integral term.

3.5 Open-Loop and Closed-Loop Embedded ControlSoftware Coding of a PID Controller using CDefining the PidUpdate function:double PidUpdate (PID_DATA *pid_data, double sensor_value, double reference_signal){

double Pterm, Iterm, Dterm;double error, difference;error _ reference_value – sensor_value;Pterm = pid_data->Pgain *error; /*proportional term*/pid_data->error_sum += error; /*current + cummulative*/// the integral termIterm = pid_data->Igain *pid_data->error_sum;difference = pid_data->sensor_Value_previous – sensor_value;// update for next iterationpid_data->sensor_value_previous = sensor_value;// the derivative termDterm = pid-data->Dgain *difference;return (Pterm + Iterm + Dterm

}There are some modifications typically made to the basic code to improve PID controller performance. For example, the error_sum is typically constrained to stay within a particular range, to reduce oscilla-tion, and to avoid having the variable reach its upper limit and hence roll over to 0. Also the actuator of the error is typically stopped both when the tracking error is large and during periods of actuator saturation.

3.5 Open-Loop and Closed-Loop Embedded Control

Quantization

Quantization occurs when a signal or machine number must be altered to fit the constraints of the computer memory.Number 0.36 were to be stored as a 4-bit fraction, then it would have toquantized to one of the following machine numbers 0.75, 0.50, 0.25, 0.00, -0.25, -0.50, -0.75, -1.00. The closed machine number is 0.25, which would result in a quantization error of 0.11.

Quantization occurs for two reasons:• machine arithmetic can generate results requiring more precision that the

original values• analog signals available from the sensors are real valued, which are

quantized into machine numbers through ADC; accuracy and expenseincrease as the number of bits in the digital representation increase

3.5 Open-Loop and Closed-Loop Embedded Control

Overflow

Overflow results when a machine operation outputs a number with magnitude too large to be represented by the numeric processor4-bit example: 0.75+0.50=1.25 is too large to be represented as a machine Number

The results of overflow are dependent on the method that the numeric processor uses to implement the binary representation of machinenumbers

3.5 Open-Loop and Closed-Loop Embedded Control

Aliasing

Physical systems typically evolve in continuous time, but discrete time control signal operate on samples of the evolving process. These simple facts can lead to counter intuitive behavior, if the sampling processes are not properly designed.

Aliasing is an artifact of the sampling process. When the sampling frequency is fS based on the sample record, the computer can only resolve frequencies in a range of fS Hz.

In most applications, the system is designed so that this range is

f ∈[-fN, fN]

where fN= fS /2 is the Nyquist frequency.

3.5 Open-Loop and Closed-Loop Embedded Control

Aliasing

Circles every 0.4 s represent the discrete time samples, sampling frequency is 25 Hz.Actual signal is y(t) =1.0*sin(6πt) which is periodic with frequency 3.0 Hz. The figure shows that based on the samples available to it from the sampling process, the actual signal is indistinguishable from v(t)=1.0*sin(πt). In Fact anay of the sinusoids given by z(t)=1.0*sin((2π)(0.5+2.5n)+t) for any integer n would result in these same samples