Allgemeine Lösung mittels Hazard Detectionunikorn/lehre/gdra/ss14/04... · Control‐Hazards...

Transcript of Allgemeine Lösung mittels Hazard Detectionunikorn/lehre/gdra/ss14/04... · Control‐Hazards...

Allgemeine Lösung mittels Hazard‐Detection‐Unit

Grundlagen der Rechnerarchitektur ‐ Prozessor 83Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Implementation der Hazard‐Detection‐Unit

Grundlagen der Rechnerarchitektur ‐ Prozessor 84

Quiz: Vermeiden von Pipeline‐Stalls

Grundlagen der Rechnerarchitektur ‐ Prozessor 85

lw $t1, 0($t0)

lw $t2, 4($t0)

add $t3, $t1, $t2

sw $t3, 12($t0)

lw $t4, 8($t0)

add $t5, $t1, $t4

sw $t5, 16($t0)

Wo findet ein Pipe‐line‐Stall statt? Bitte ankreuzen.

Bitte Befehle umorganisie‐ren, sodass alle Stalls vermieden werden.

Anzahl Taktzyklen mit Stalls?Anzahl Taktzyklen ohne Stalls?

Control‐Hazards

Grundlagen der Rechnerarchitektur ‐ Prozessor 86

Control‐Hazards

Grundlagen der Rechnerarchitektur ‐ Prozessor 87Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

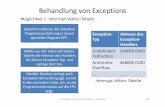

Branch‐Not‐Taken‐Strategie und Pipeline‐Flush

Grundlagen der Rechnerarchitektur ‐ Prozessor 88

Flush = Verwerfe Instruktionen in der Pipeline. Hier: Setze IF/ID‐, ID/EX‐ und EX/MEM‐Register auf 0.

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Reduktion des Branch‐Delays• Adressberechnung kann schon in der

ID‐Stufe stattfinden• beq und bne erfordert lediglich ein

32‐Bit‐XOR und ein 32‐Bit‐OR– Dazu braucht man keine ALU– Also auch in der ID‐Stufe realisierbar

• Damit ist der Sprung schon in der ID‐Stufe entschieden

Grundlagen der Rechnerarchitektur ‐ Prozessor 89Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Beispiel: für $1 und $3:

Reduktion des Branch‐Delays

• Konsequenz– Branch‐Delay ist damit ein Instruktions‐Zyklus– Wir brauchen lediglich ein Flush‐IF/ID‐Register

Grundlagen der Rechnerarchitektur ‐ Prozessor 90

Reduktion des Branch‐Delays• Achtung!

– Forwarding aus späteren Stufen macht die Sache kompliziert.

– Kann Pipeline‐Stall aufgrund von Data‐Hazards erforderlich machen.

• z.B. ein Zyklus, wenn ALU‐Ergebnis in den Vergleich einfließt

• z.B. zwei Zyklen, wenn Vergleichsoperator einen Schritt vorher aus dem Speicher geladen wurde

– Betrachten wir aber hier nicht genauer.

Grundlagen der Rechnerarchitektur ‐ Prozessor 91Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Dynamic‐Branch‐Prediction‐Strategie

Grundlagen der Rechnerarchitektur ‐ Prozessor 92

Unterer Teil der Adresse

Branch hat stattgefunden

0x00 10x04 00x08 1...0xf8 00xfc 0

Branch‐Prediction‐Buffer

0x400000 : lw $1, 0($4)0x400004 : beq $1, $0, 400x400008 : add $1, $1, $10x40000c : ......

...0x40c004 : bne $3, $4, 120...

Vorhersagegenauigkeit

Grundlagen der Rechnerarchitektur ‐ Prozessor 93

Annahme unendlich langer Loop, der immer 9 mal und dann einmal nicht durchlaufen wird. Was ist die Vorhersagegenauigkeit der vorher beschriebenen Branch‐Prediction?

Lässt sich das verbessern?

loop: ......bne $1,$2,loop...j loop

N‐Bit‐Vorhersage am Beispiel 2‐Bit

Grundlagen der Rechnerarchitektur ‐ Prozessor 94Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Vorhersagegenauigkeit

Grundlagen der Rechnerarchitektur ‐ Prozessor 95

Annahme unendlich langer Loop, der immer 9 mal und dann einmal nicht durchlaufen wird. Was ist die Vorhersagegenauigkeit der vorher beschriebenen 2‐Bit‐Branch‐Prediction?

loop: ......bne $1,$2,loop...j loop

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Branch‐Delay‐Slot‐Idee

Grundlagen der Rechnerarchitektur ‐ Prozessor 96

loop: ......bne $1,$2,loop<instruktion><instruktion>

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

• Wird immer ausgeführt.• Instruktion muss aber unabhängig vonder Branch‐Entscheidung sein.

• Das muss der Compiler entscheiden.• Im Zweifelsfall: nop passt immer.

Beispiele von Branch‐Delay‐Slot‐Schedules

Grundlagen der Rechnerarchitektur ‐ Prozessor 97Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Weniger Branches mit Conditional‐Instruktionen

Grundlagen der Rechnerarchitektur ‐ Prozessor 98

Beispiel MIPS‐Instruktionen movn und movz:movn $8, $11, $4 # $8 = $11, wenn $4 != 0movz $8, $11, $4 # $8 = $11, wenn $4 == 0

Beispiel ARM‐ISA:ADDEQ r0,r1,r2 ; If zero flag set then…

; ... r0 = r1 + r2

Quiz

Grundlagen der Rechnerarchitektur ‐ Prozessor 99

Betrachte die folgenden Branch‐Strategien:1. Vorhersage Branch findet statt2. Vorhersage Branch findet nicht statt3. Dynamische Branch‐Vorhersage (mit 90% Genauigkeit)

Was ist die beste Strategie, wenn:

• Branch findet mit 5% Häufigkeit statt?

• Branch findet mit 95% Häufigkeit statt?

• Branch findet mit 70% Häufigkeit statt?

Multiple‐Issue

Grundlagen der Rechnerarchitektur ‐ Prozessor 100

Motivation• Bisher: Instruction‐Level‐Parallelism (ILP) durch Pipelining

– ILP kann durch Pipeline‐Stufe erhöht werden– Pipelines mit mehr Stufen sind anfälliger gegenüber Data‐ und Control‐

Hazards– Also: Pipeline‐Stufen nur bis zu gewisser Tiefe sinnvoll– Außerdem: Grenzen aufgrund der Leistungsaufnahme– CPI bleibt gleich oder steigt sogar (wegen Hazards), Clock‐Rate steigt

• Hier eine weitere Methode um ILP zu steigern: Multiple‐Issue– Replikation von internen CPU‐Strukturen, sodass mehrere Instruktionen pro

Pipeline‐Stufe möglich sind– CPI sinkt und Clock‐Rate bleibt gleich (oder sinkt sogar wegen erhöhter

Komplexität)– Beispiel: CPI eines 4‐Wege‐Multiple‐Issue‐Mikroprozessor hat eine ideale CPI

von? 0.25!– CPI liegt aber in der Regel höher, wie wir gleich sehen werden

• Wir unterscheiden zwischen:– Static‐Multiple‐Issue: Entscheidungen werden zur Compile‐Zeit gefällt– Dynamic‐Multiple‐Issue: Entscheidungen werden zur Laufzeit gefällt

(auch Superskalare CPU bezeichnet)

Grundlagen der Rechnerarchitektur ‐ Prozessor 101

Multiple‐IssueStatic‐Multiple‐Issue

Grundlagen der Rechnerarchitektur ‐ Prozessor 102

Generelle Idee• Eine große Instruktion pro Clock‐Cycle• Große Instruktion besteht aus mehreren gleichzeitig stattfindenden Operationen

• Aber nicht jede Kombination von Operationen möglich

• Beispiel:– ALU‐Operation und Speicheroperation gleichzeitig möglich

– Aber zwei ALU‐Operation auf einmal nicht möglich

• Terminologie: VLIW (Very Long Instruction Word)

Grundlagen der Rechnerarchitektur ‐ Prozessor 103

Beispiel am MIPS‐Datenpfad

Grundlagen der Rechnerarchitektur ‐ Prozessor 104Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Extra ALU für gleichzeitige Adresskalkulation

ALU für arithmetische Operationen

Statische Two‐Issue Pipeline im Betrieb

Grundlagen der Rechnerarchitektur ‐ Prozessor 105Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Was ist der CPI‐Wert?

Was ist nun die Aufgabe des Compilers?

Grundlagen der Rechnerarchitektur ‐ Prozessor 106Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Loop: lw $t0, 0($s1) # $t0=Array-Elementaddu $t0, $t0, $s2 # addiere Wertsw $t0, 0($s1) # Speichere Elementaddi $s1, $s1, -4 # nächstes Elementbne $s1, $zero, Loop # solange $s1 != 0

Compiler erzeugt Assembler‐Code:

und ordnet Instruktionen so an, dass keine Pipeline‐Stalls entstehen

Was ist der CPI‐Wert?

Verbesserung: Loop‐Unrolling

Grundlagen der Rechnerarchitektur ‐ Prozessor 107

Loop: lw $t0, 0($s1) # $t0=Array-Elementaddu $t0, $t0, $s2 # addiere Wertsw $t0, 0($s1) # Speichere Elementaddi $s1, $s1, -4 # nächstes Elementbne $s1, $zero, Loop # solange $s1 != 0

Code wie vorher (der Einfachheit sei Loop‐Index Vielfaches von 4):

Loop‐Body vier mal kopiert und Register‐Renaming

Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Was ist der CPI‐Wert?

Multiple‐IssueDynamic‐Multiple‐Issue

Grundlagen der Rechnerarchitektur ‐ Prozessor 108

Generelle‐Idee• CPU entscheidet, ob und wie viele aufeinander folgende Instruktionen parallel gestartet werden können

• Compiler erzeugt nur eine Folge von Instruktionen; kein VLIW

• Instruktions‐Scheduling des Compilers nicht mehr erforderlich aber trotzdem aus Performance‐Gründen sinnvoll

• Verbesserung der Superskalarität durch dynamisches Pipeline‐Scheduling: Instruktionsreihenfolge darf geändert werden, um Stalls zu vermeiden

Grundlagen der Rechnerarchitektur ‐ Prozessor 109

Dynamic‐Pipeline‐Scheduling Motivation

Grundlagen der Rechnerarchitektur ‐ Prozessor 110

lw $t0, 20($s2) # zunächst $t0 ladenaddu $t1, $t0, $t2 # addu durch lw verzögertsub $s4, $s4, $t3 # sub könnte schon startenslti $t5, $s4, 20 # und genau so auch slti

Warum nicht sub (und ggf. slti) vor addu vorziehen?

Dynamic‐Pipeline‐Scheduling generell

Grundlagen der Rechnerarchitektur ‐ Prozessor 111Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

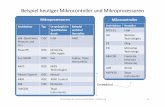

Wiedervorlage: Daten einiger ausgewählter Prozessoren

Grundlagen der Rechnerarchitektur ‐ Prozessor 112Bildquelle: David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 2012

Zusammenfassung und Literatur

Grundlagen der Rechnerarchitektur ‐ Prozessor 113

Zusammenfassung• Schlechte Performance von Single‐Cylce‐Ansatz• Instruktionsabarbeitung besteht aus mehreren Zyklen• Moderne Prozessoren nutzen dies für

– Pipelining– Multiple‐Issue

• Allgemein als Instruction‐Level‐Parallelism bezeichnet• Für High‐Level‐Programmierer ist die Parallelität nicht sichtbar

– Sichtbar auf Assembler‐Ebene– Sichtbar auf Compiler‐Ebene

• Hauptprobleme die die Parallelität einschränken– Daten‐Abhängigkeiten– Control‐Abhängigkeiten

• Methoden um Data‐ und Control‐Hazards zu reduzieren– Scheduling– Spekulation

• Sichtbare Grenze der Power‐Wall ist erreicht• Trend zu Multicores mit einfacheren Pipelines• Konsequenz: Parallelität nicht mehr von der Hardware gekapselt

Grundlagen der Rechnerarchitektur ‐ Prozessor 114

Quiz

Bildquelle: www.geemag.de/wp‐content/artikel_endgegner_bild.jpg

Welchen Einfluss hat Pipelining auf den CPI‐Wert?[ ] Der CPI‐Wert bleibt immer unverändert. [ ] Der CPI‐Wert kann unter 1 fallen. [ ] Der CPI‐Wert steigt in der Regel an.

Grundlagen der Rechnerarchitektur ‐ Logik und Arithmetik 115

Mittels Pipelining kann man die Taktrate eines Rechners erhöhen.[ ] Stimmt! [ ] Nein, das ist völliger Quatsch.

Eine Pipeline mit k Stufen erreicht asymptotisch immer eine Performance‐Ratio von k.[ ] Jawohl. [ ] Nein, die Ratio kann darunter liegen.[ ] Nein, die Ratio kann sogar noch höher liegen.

Welchen Einfluss hat Superskalarität auf den CPI‐Wert?[ ] Der CPI‐Wert bleibt immer unverändert, [ ] Der CPI‐Wert steigt an.[ ] Der CPI‐Wert kann unter 1 fallen.

Pipelining erhöht den Durchsatz aber reduziert nicht die Instruktions‐Latenz.[ ] Nein, Durchsatz und Latenz sinken [ ] Nein, Durchsatz und Latenz steigen [ ] Ja, das ist richtig

Super! Geschafft. Auf zum nächsten Level.

Literatur[PattersonHennessy2012] David A. Patterson und John L. Hennessy, „Computer Organization and Design“, Fourth Edition, 20124.1 Introduction4.2 Logic Design Conventions4.3 Building a Datapath4.4 A Simple Implementation Scheme4.5 An Overview of Pipelining4.6 Pipelined Datapath and Control4.7 Data Hazards: Forwarding versus Stalling4.8 Control Hazards4.10 Parallelism and Advanced Instruction‐Level Parallelism4.11 Real Stuff: the AMD Opteron X4 (Barcelona) Pipeline

Grundlagen der Rechnerarchitektur ‐ Prozessor 116

![Vorlesung Compiler für Eingebettete Systeme (SS14) · Compiler für Eingebettete Systeme [CS7506] Sommersemester 2014 Heiko Falk Institut für Eingebettete Systeme/Echtzeitsysteme](https://static.fdokument.com/doc/165x107/5e0bcca2238c66363403635c/vorlesung-compiler-fr-eingebettete-systeme-ss14-compiler-fr-eingebettete-systeme.jpg)